基于FPGA的电子时钟的设计.docx

《基于FPGA的电子时钟的设计.docx》由会员分享,可在线阅读,更多相关《基于FPGA的电子时钟的设计.docx(10页珍藏版)》请在冰豆网上搜索。

基于FPGA的电子时钟的设计

1.设计要求:

1).能够显示时、分、秒的六位数值,实行24小时制。

2).具有方便的调时功能。

3).具有跑表的功能,可以方便的进行计时。

4).具有一定的稳定性。

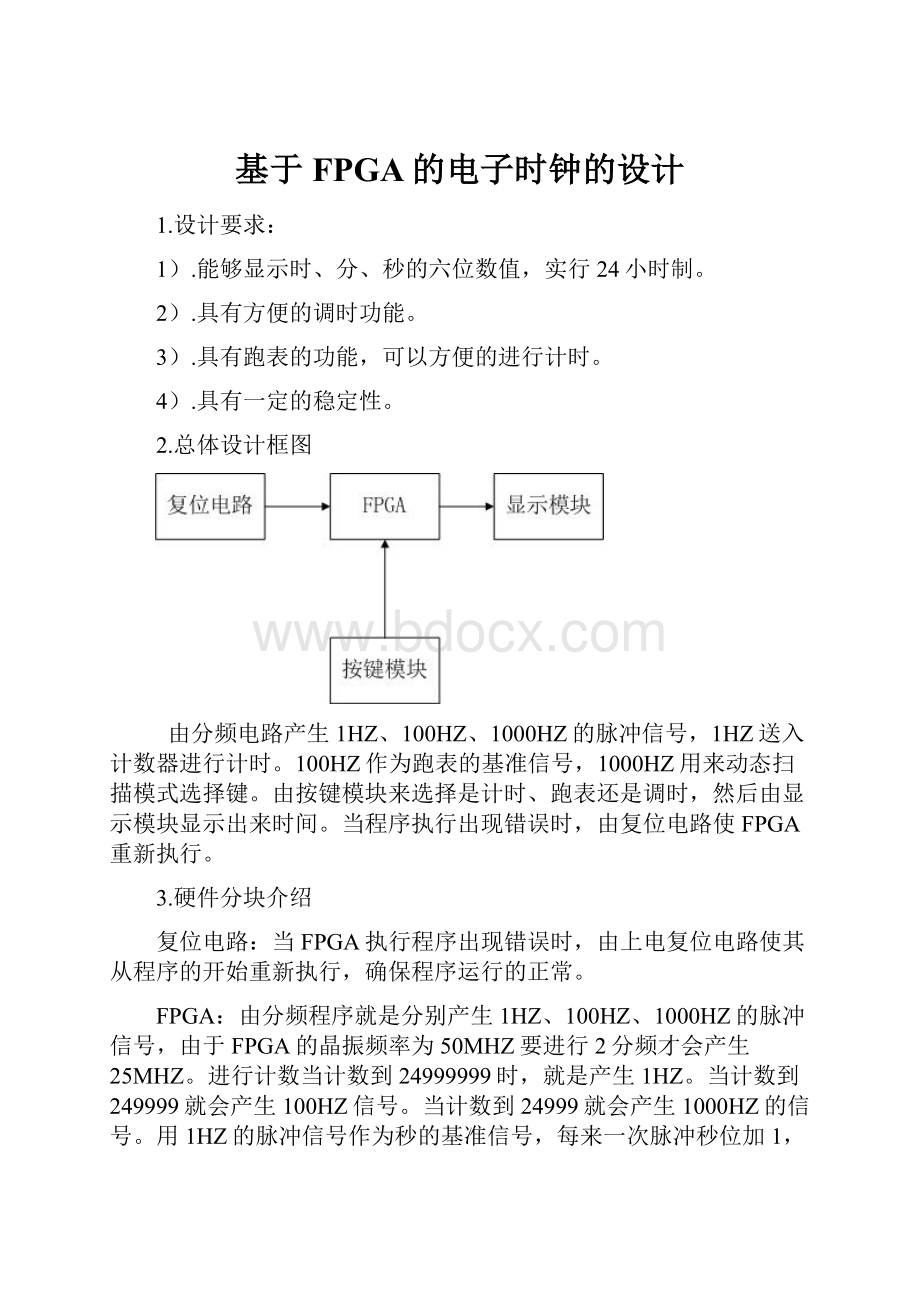

2.总体设计框图

由分频电路产生1HZ、100HZ、1000HZ的脉冲信号,1HZ送入计数器进行计时。

100HZ作为跑表的基准信号,1000HZ用来动态扫描模式选择键。

由按键模块来选择是计时、跑表还是调时,然后由显示模块显示出来时间。

当程序执行出现错误时,由复位电路使FPGA重新执行。

3.硬件分块介绍

复位电路:

当FPGA执行程序出现错误时,由上电复位电路使其从程序的开始重新执行,确保程序运行的正常。

FPGA:

由分频程序就是分别产生1HZ、100HZ、1000HZ的脉冲信号,由于FPGA的晶振频率为50MHZ要进行2分频才会产生25MHZ。

进行计数当计数到24999999时,就是产生1HZ。

当计数到249999就会产生100HZ信号。

当计数到24999就会产生1000HZ的信号。

用1HZ的脉冲信号作为秒的基准信号,每来一次脉冲秒位加1,当满60时分位加1,同时秒位清0;当分位满59时,秒位满59时再过一秒时位加1,同时分、秒位清0。

按键模块:

主要是用来实现模式选择。

本时钟有三个模式,分别是正常计时、跑表、时间调整。

而时间调整只能调分、时,且只有加1的功能。

当调整到跑表功能时,用一个按键就可以实现开始、暂停、清0的所有功能。

显示模块:

显示分为正常显示和调时显示为8位数码管显示,信号分为段选和位选,位选为先选秒个位然后循环左移逐个选择8位数码管,段选为译码器根据输出信号选择点亮的数码段。

4软件分块介绍

主流程图

分频模块流程图由于时钟频率为50MHZ要产生1HZ、100HZ、1000HZ的脉冲信号。

而且时钟先要二分频。

这是产生1s信号。

这是产生10ms信号。

这是产生1ms信号。

符号图如下:

计时模块流程图由分频产生1s的信号。

来一个脉冲秒位加1,如果满60,分位加1,秒位清0;如果分为满60,小时加1,分位清0。

符号图如下:

模式选择模式模式0为计时模式,模式1为跑表模式,模式2为调时模式。

通过一个按键来实现模式转换。

按一下为计时模式,再按一下为跑表模式,第三下为调时模式。

再按一下,重新回到计时模式。

其符号图如下:

跑表模块流程图

符号图如下:

显示模块程序流程图:

显示分为正常显示和调时显示,当模式为调时时,又分四种状态00、01、10、11。

当为00或为10时,会使分位延时一段时间,效果为跳动;当为01、11时,会使时位跳动,可以对时进行调整。

调时时的显示符号图如下:

正常调试的模块图如下:

符号图如下:

5.总的原理图如下:

6.总体仿真图如下:

7.管脚分配表:

8.实际效果图:

9.测试模块

经过测试本电子时钟的基本功能正常。

测试步骤如下:

1.按到计时模式,看秒到59时,再过一秒,秒位清0,分位加1,秒进制正常。

把分位调到59,过一分钟,分位变0,小时位加1。

然后把小时位调到23,分位调到59,过一分钟,发现小时位和分位都变0。

表示计时正常。

2.按到跑表模式,看到最低两位,到99时,再过10ms,最后两位变0,中两位的低位加1。

表示跑表功能正常。

3.按到调时模式,调节不是很正常,按键加1功能有时按几下也不会加1。

4.模式转换键也不是很正常,有时按几下也不会转换。

10.心得体会

通过这次的课程设计,我又学会了一种软件的使用,既使用Quartus软件进行程序的编辑。

为实现预期功能,能够对系统进行快速的调试,并能够对出现的功能故障进行分析,及时修改相关软件。

了解了关于EDA技术及VerilogHDL语言的基本编程形式,在此之后,我会继续学习关于VerilogHDL语言的运用。

通过这次课程设计,不仅检验了我所学习的知识,也培养了我如何去把握一件事情,如何去做一件事情,又如何完成一件事情。

在设计过程中,和同学们相互探讨,相互学习。

通过这次课程设计,本人在多方面都有所提高。

通过这次课程设计,综合运用本专业所学课程的理论从而培养和提高我的独立工作能力,巩固与扩充了EDA课程设计等课程所学的内容,掌握数字钟设计的方法和步骤,并懂得了怎样使用数字钟的功能,怎样确定设计方案,了解了数字钟的基本结构,提高了整体构思能力,实际应用能力,熟悉了规范和标准,独立思考的能力也有了提高。

总的来说,这次设计的数字钟还是比较成功的,有点小小的成就感,终于觉得平时所学的知识有了实用的价值,达到了理论与实际相结合的目的,不仅学到了不少知识,而且锻炼了自己的能力,使自己对以后的路有了更加清楚的认识,同时,对未来有了更多的信心。