AT89C52单片机Word文件下载.docx

《AT89C52单片机Word文件下载.docx》由会员分享,可在线阅读,更多相关《AT89C52单片机Word文件下载.docx(10页珍藏版)》请在冰豆网上搜索。

输入输出接口

计数器

定时器

时钟

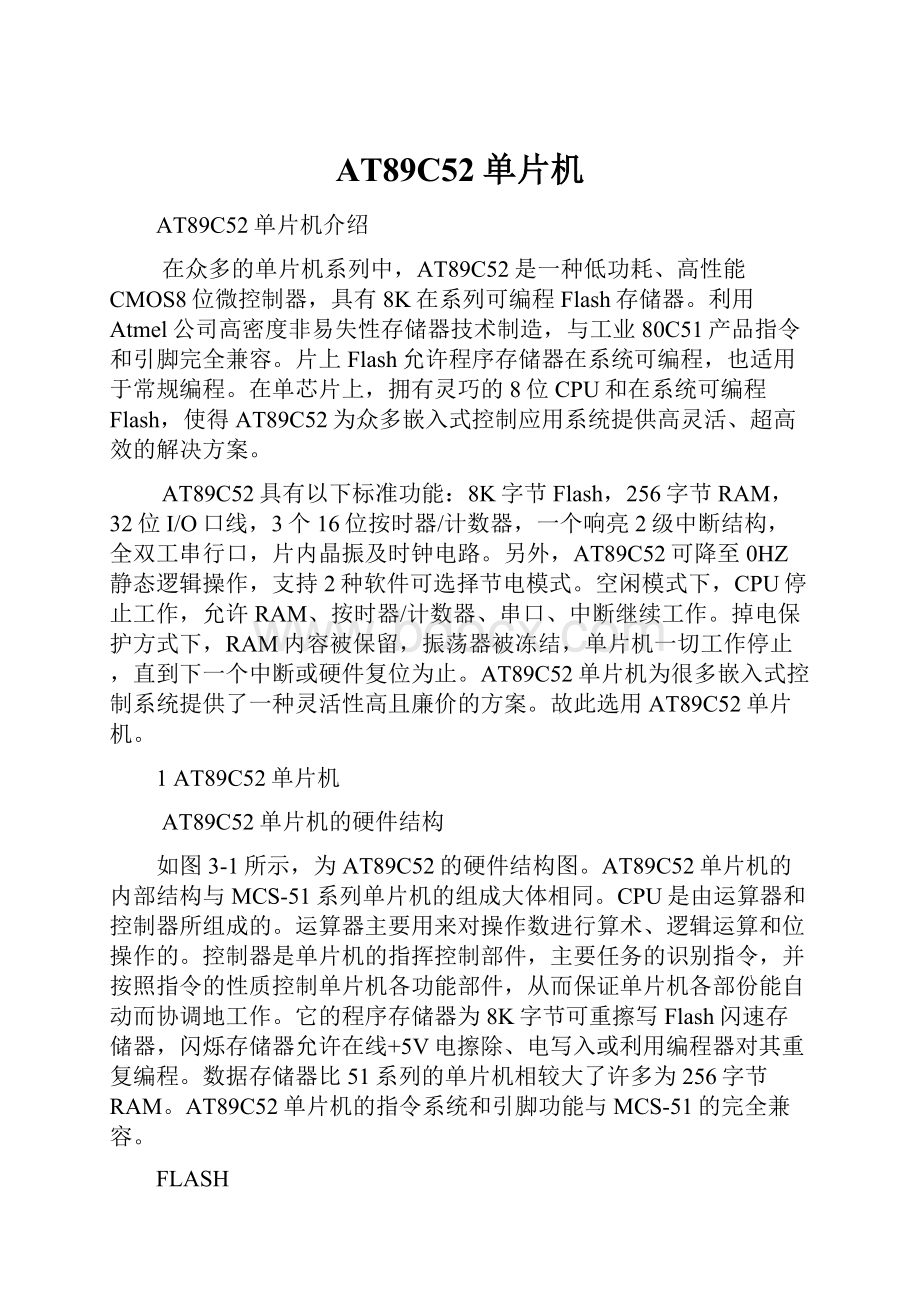

图3-1单片机89C52结构框图

主要性能参数

•8K字节可重擦写Flash闪速存储器

•1000次可擦写周期

•全静态操作:

0Hz-24MHz

•三级加密程序存储器

•256×

8字节内部RAM

•32个可编程I/O口线

•3个16位按时/计数器

•8个中断源

•可编程串行UART通道

•低功耗空闲和掉电模式

图3-2AT89C52外部引脚图

AT89C52管脚说明

VCC:

电源

GND:

接地

P0口:

P0口是一个8位漏级开路的双向I/O口。

作为输出口,每位能驱动8个TTL逻辑电平。

对P0口端口写“1”时,引脚作高阻抗输入。

当访问外部程序和数据存储器时,P0口也被作为低8位地址/数据复用。

在这种模式下,P0具有内部上拉电阻。

在flash编程时,P0口也用来接受指令字节:

在程序效验时,输出指令字节。

程序效验时,需要外部上拉电阻。

P1口:

P1口是一个具有内部上拉电阻的8位是双向I/O口,P1的输出缓冲级可驱动(吸收或输出电流)4个TTL逻辑电平。

对P1口写“1”时,内部上拉电阻的原因,将输出电流ILL。

另外,与AT89C51不同的地方是,和还可别离作为按时/计数器2的外部计数输入(T2)和输出(T2EX),具体如下表所示。

表和的第二功能

引脚号

功能特性

T2(定时/计数器2外部计数脉冲输入),时钟输出

T2EX定时/计数2捕获/重装载触发和方向控制

在Flash编程和校验时,P1口接收低8位地址字节。

P2口:

P2口是一个具有内部上拉电阻的8位双向I/O口,P2输出缓冲级可驱动吸收或输出电流4个TTL逻辑电平。

对P2口写“1”时,通过内部上拉电阻把端口拉高,此时可以作为输入口利用。

作为输入利历时,被外部拉低的引脚由于内部电阻的原因,将输出电流ILL。

在访问外部好曾许存储器或用16位地址读取外部数据存储器时,P2口送出高8位地址。

在这种应用中,P2口利用很强的内部上拉发送1。

在利用8位地址访问外部数据存储器时,P2口输出P2锁存器的内容。

在Flash编程和校验时,P2口接收低8位地址字节和一些控制信号。

P3口:

P3口是一个具有内部上拉电阻的8位双向I/O口,P3输出缓冲级可驱动(吸收或输出电流)4个TTL逻辑电平。

对P3口写“1”时,内部上拉电阻把端口拉高,此时可以作为输入端口利用。

P3口除作为一般、的I/O口线外,更重要的是它的第二功能,如下表所示。

表P3口引脚第二功能

第二功能

RXD(串行输入)

TXD(串行输出)

INT0(外部中断0)

INT1(外部中断1)

T0(定时器0外部输入)

T1(定时器1外部输入)

WR(外部数据存储器写选通)

RD(外部数据存储器读选通)

在Flash编程和校验时,P3口也接收一些控制信号。

RST:

复位输入。

晶振工作时,RST脚持续2个机械周期以高电平将利用单片机复位。

ALE/

:

地址锁存器控制信号(ALE)是访问外部程序存储器时,锁存低8位地址的输出脉冲。

在Flash编程时,此引脚(

)也利用作编程输入脉冲。

在一般情况下,ALE以晶振六分之一的固定频率输出脉冲,可用来作为外部按时器或时钟利用。

但是,特别强调,在每次访问外部数据存储器时,ALE脉冲将会跳过。

若是需要,通过将地址为8EH的SFR的第0位置“1”,ALE操作无效。

这一名置“1”,ALE仅在执行MOVX或MOVC指令时有效。

不然,ALE将被微弱拉高。

这个ALE使能标志位的设置对微控制器处于外部执行模式下无效。

外部程序贮存器选通信号(

)是外部程序存储器选通信号。

当AT89C52从外部程序存储器执行外部代码时,

在每一个机械周期被激活两次,而在访问外部数据储存器时,

将不被激活。

访问外部程序存储器控制信号。

为使能从0000H—FFFFH的外部程序存储器读取指令,

端必需维持低电平(接地)。

为了执行内部程序指令,

应该接VCC。

在flash编程期间,

也接受12伏VPP电压。

XTAL1:

振荡器反相放大器及内部时钟发生器的输入端。

XTAL2:

振荡器反相放大器的输出端。

存储器结构

MCS-51器件有单独的程序存储器和数据存储器。

外部程序存储器和数据存储器都可以64K寻址。

1.程序存储器

若是EA引脚接地,程序读取只从外部存储器开始。

对于89C52,若是EA接VCC,程序先从内部存储器(地址为0000H~1FFFFH)开始,接着从外部寻址,寻址范围为:

2000H~FFFFH。

2.数据存储器

AT89C52有256字节RAM。

高128字节与特殊功能寄放重视叠。

也就是说高128字节与特殊功能寄放器有相同的地址,而物理上是分开的。

当一条指令访问高于7FH的地址时,寻址方式决定CPU访问高字节RAM仍是特殊功能寄放器空间。

直接寻址方式访问特殊功能寄放器(SFR)。

按时器

1.按时器0和按时器1

在AT89C52中,定时器0和定时器1都是16位加法计数结构,分别由TH0(地址8CH)和TL0(地址8AH)及TH1(地址8DH)和TL1(地址8BH)两个8位计数器组成。

这4个计数器均属于专用寄存器之列。

每个定时器/计数器都有定时和计数两种功能。

2.计数功能

所谓的计数功能是指对外部事件进行计数。

外部事件的发生以输入脉冲表示,因此计数功能的实质就是对外脉冲进行计数。

MCS-51系列的芯片有T0()和T1()两个信号引脚,别离就是这两个计数器的计数输入端。

外部输入的脉冲在负跳变时有效,进行计数器加1。

计数方式下,单片机在每一个机械周期的S5P2拍节对外部计数脉冲进行采样。

若是前一个机械周期采样为高电平,后一个机械周期采样为低电平,即为一个有效计数脉冲。

在下一个机械周期的S3P1进行计数。

可见采样计数脉冲是在2个机械周期进行的。

鉴于此,计数脉冲的频率不能高于振荡脉冲的频率不能高于振荡脉冲频率的1/24。

3.按时功能

按时器也是通过计数器的计数来实现的,不过此时的计数脉冲来自单片机的内部,即每一个机械周期产生一个计数脉冲。

也就是每一个机械周期计数加1。

由于一个机械周期等于12个振荡脉冲周期,因此计数频率为振荡频率的1/12。

若是单片机采用12MHz晶体,则计数频率为1MHz。

即每微秒计数器加1。

这样不但可以按照计数值计算出按不时间,也可以反过来按按不时间的要求计算出计数器的预置值。

4.按时器2

按时器2是一个16位按时器/计数器,它既可以作按时器,又可以做事件计数器。

其工作方式由特殊寄放器T2CON中的C/T2位选择(如表2所示)。

按时器2有三种工作模式:

捕捉方式、自动重载(向上或向下计数)和波特率发生器。

如表所示,工作模式由T2CON中的相关为选择。

按时器2有2个8位寄放器:

TH2和TL2。

在按时工作方式中,每一个机械周期,TL2寄放器都会加1。

由于一个机械周期由12个晶振周期组成,因此,计数频率就是晶振频率的1/12。

表按时器2工作模式

RCLK+TCLK

CP/RL2

TR2

MODE

1

16位自动重载

16位捕捉

×

波特率发生器

不用

在计数工作方式下,寄放器在相关外部输入角T2发生1至0的下降沿时增加1。

在这种方式下,每一个机械周期的S5P2期间采样外部输入。

一个周期采样到高电平,而下一个周期采样到低电平,计数器加1。

在检测到跳变的这个周期的S3P1期间,新的计数值出此刻寄放器中。

因为识别1—0的跳变需要2个机器周期(24个晶振周期),所以,最大的计数频率不高于晶振频率的1/24。

为了确保给定的电平在采样前采样到一次,电平应该至少在一个完整的机器周期内维持不变。

表T2MOD-按时器2控制寄放器

T2MOD地址:

0C9H复位值:

00B

-

T2OE

DCEN

7

6

5

4

3

2

符号

功能

—

无定义,预留扩展

定时器2输出允许位

置1后,定时器2可配置向上或向下计数

中断

AT89C52有6个中断源:

两个外部中断(INT0和INT1),三个按时中断按时器0、一、2和一个串行中断。

每一个中断源都可以通过置位或清除特殊寄放器IE中的相关中断允许控制位别离使得中断源有效或无效。

IE还包括一个中断总控制位EA,它能禁止所有中断。

如表所示,位是不可用的。

对于AT89S52,位也是不能用的。

用户软件不该给这些位写1。

它们为AT89系列新产品预留。

按时器2可以被寄放器T2CON中的TF2和EXF2的或逻辑触发。

程序进入中断服务后,这些标志位都可以由硬件清0。

实际上,中断服务程序必需判定是不是是TF2或EXF2激活中断。

标志位也必需由软件清0。

按时器0和按时器1标志位TF0和TF1在计数溢出的那个周期的S5P2被置位。

它们的值一直到下一个周期被电路捕捉下来。

但是,按时器2的标志位TF2在计数溢出的那个周期被置位,在同一个周期被电路捕捉下来。

表中断允许控制位

位地址

EA

中断允许控制位,EA=0,中断总禁止;

EA=1,各中断由各自的控制位设定

预留

ET2

定时器2中断允许控制位

ES

串行口中断允许控制位

ET1

定时器1中断允许控制位

EX1

外部中断1允许控制位

ET0

定时器0中断允许控制位

EX0

外部中断0允许控制位

晶振特性

AT89C52单片机有一个用于组成内部振荡器的反相放大器,XTAL1和XTAL2别离是放大器的输入、输出端。

石英晶体和陶瓷谐振器都可以用来一路组成自激振荡器。

从外部时钟远驱动器件的话,XTAL2可以不接,而从XTAL1接入。

由于外部时钟信号通过二分频触发后作为外部时钟电路输入的,所以对外部时钟信号的占空比没有其它要求,最长低电平持续时间和最少高电平持续时间等仍是要符合要求的。

石英晶振C1,C2=30PF+-10PF

陶瓷谐振器C1,C2=40PF+-10PF

空闲模式

在空闲工作模式下,CPU处于睡眠状态,而所有片上外部设备维持激活状态。

这种状态可以通过软件产生。

在这种状态下,片上RAM和特殊功能寄放器的内容维持不变。

空闲模式可以被任一个中断或硬件复位中止。

由硬件复位终止空闲模式只需两个机械周期有效复位信号,在这种情况下,片上硬件禁止访问内部RAM,而可以访问端口引脚。

空闲模式被硬件复位终止后,为了避免预想不到的写端口,激活空闲模式的那一条指令的下一条指令不该该是写端口或外部存储器。

掉电模式

在掉电模式下,晶振停止工作,激活掉电模式的指令是最后一条执行指令。

片上RAM和特殊功能寄放器维持原值,直到掉电模式终止。

掉电模式可以通过硬件复位和外部中断退出。

复位从头概念例如SFR的值。

在VCC未恢复到正常工作电压时,硬件复位不能无效。

而且应维持足够长的时间以使晶振从头工作和初始化。

表空闲模式和掉电模式下的外部引脚状态

模式

程序存储器

ALE

PESN

PORT0

PORT1

PORT2

PORT3

空闲

内部

数据

外部

浮空

地址

掉电