crosstalk文档格式.docx

《crosstalk文档格式.docx》由会员分享,可在线阅读,更多相关《crosstalk文档格式.docx(23页珍藏版)》请在冰豆网上搜索。

(2)

(3)

CLC

Cs

Cgd

Cps’

Cps

Cpg

Cpg’

Common

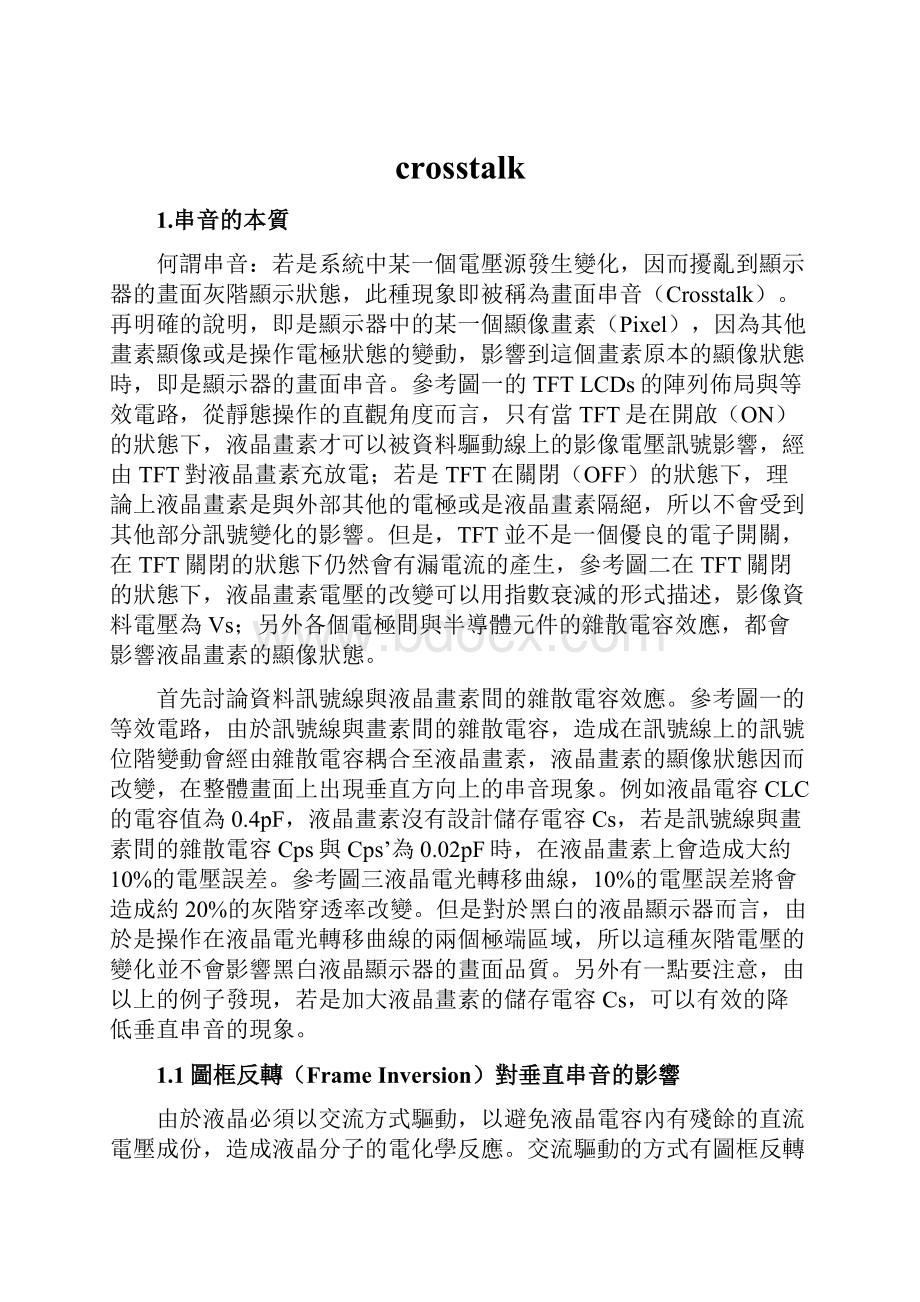

圖1.TFTLCDs的畫素矩陣佈局與液晶畫素的等效電路

在同一條水平掃描線上,跨於液晶畫素電容兩端的畫素電壓可用(4)式描述,隨掃描時間不同,液晶畫素被其他掃描時間的影像資料訊號(Vj)影響,所以液晶畫素的有效電壓為在整個圖框掃描的均方根電壓(RMS)。

(4)

對於訊號電壓的極性定義以共通電極(Common)的電壓位準為參考依據,若是訊號的電壓位準低於共通電極的電壓位準,此時訊號電壓Vj(t)即為負極性,若是高於共通電極的電壓位準,即為正極性的影像訊號,同理Vi的定義也是以共通電極的電壓位準為參考。

參考(4)式,若Vi是正極性而Vj(t)為負極性,(4)是可改寫成如(5)式:

(5)

(5)式中Vi,Vj都是取正數。

圖2.採用圖框反轉交流驅動時,TFTLCDs的驅動波形與液晶畫素電壓波形。

Vgh與Vgl分別為水平掃描脈波開啟與關閉TFT的電壓位階,Vs為垂直訊號線上的驅動波形,Vp為液晶畫素內的電壓波形。

圖3.液晶的電光特性曲線

若是採用圖框反轉的極性交換方式,第i列(Row)的液晶畫素的有效電壓值,是整個畫面完成掃描的週期時間內的電壓均方根(RMS)值。

假設第i列水平掃描線被選取驅動時,對應的垂直影像電壓為Vi;

同理,當其他水平掃描線被選取驅動時,對應的垂直影像電壓為Vj(1<

j<

N,N為水平掃描線的數目),所以對於第i列上液晶畫素的最後RMS電壓值如(6)式:

(6)

分析(6)式各項所表示的意義:

大括號內的第一項Vi2是掃描第i列時的訊號電壓平方值,第二項多項式重寫如下式:

這項是表示在第i列以上的水平掃描線,在掃描週期內對於第i列的電容耦合效應。

由於從第1列至第i-1列的垂直影像訊號與第i列上液晶畫素所儲存的影像訊號電壓極性是相反的,對於第i列的液晶畫素所造成的影響趨勢是將液晶畫素內儲存的電荷經由耦合電容洩漏到垂直影像訊號驅動線。

所以液晶畫素的有效電壓會較理想的電壓位階低。

參考(5)式中的第三項:

這項是表示在第i列以下的水平掃描線,在掃描週期內對於第i列的電容耦合效應。

由於從第i-1列至第N列的垂直影像訊號與第i列上液晶畫素所儲存的影像訊號電壓極性是相同的,對於第i列的液晶畫素所造成的影響趨勢是將儲垂直影像訊號驅動線上的電荷經由耦合電容洩漏到液晶畫素內。

重新審視整理(6)式,經過計算後可得到如(7)式的結果。

(7)式的三個部份分別代表不同的意義:

第一部份表示第i列上液晶畫素被寫入的正確電壓,第二部份表示第一階串音成份,第三部份表示第二階串音成份。

至於造成串音的主要成份是第一階串音,第二階串音由於是平方項所以造成串音的影響很小。

所以垂直串音都以第二項的一階串音為主要克服對象。

假設一個液晶顯示器的畫面具有240條水平掃描線,交流驅動的方式採用圖框反轉驅動,畫面顯示單一灰階背景時,在實際畫面上會有什麼情況發生?

參考(7)式的結果:

若i<120也就是第i列是在前半部的水平掃描中的某一條時,由於從i+1至第N條水平掃描線的對應垂直影像電壓極性與第i列相同,而且電容耦合的效果大於由第1列至第i-1列的相反極性電壓耦合的影響,所以會造成第i列上液晶畫素的RMS電壓值大於理想正確電壓值(1-α-β)2Vi2,而且當i愈接近1時此一情況愈嚴重。

相反的情況發生在當i>120時,液晶畫素上的RMS電壓值會愈來愈小於理想的正確電壓值。

若是液晶顯示器是NW(NormalWhite)顯像模式,垂直串音造成的結果是畫面的亮度由畫面頂端到底端分佈不均勻,愈頂端畫面愈黑,愈低端畫面亮度愈亮。

參考圖4的顯示畫面。

(7)

若是畫面顯示如圖5的視窗畫面時,同樣可以用上述的方式來討論:

若是視窗畫面為黑色背景與白色視窗時,由於白色視窗訊號電壓為低電壓驅動訊號,所以在白色視窗的垂直區域內,電壓的電容耦合效應較低,所以上半部份的畫面會較背景的亮度更低,下半部的情況則相反。

若畫面的視窗圖樣是白色背景與黑色視窗時,畫面的顯示狀態如圖6所示。

圖4.採用圖框反轉交流驅動時,液晶畫面的垂直串音現象。

圖5.採用圖框反轉交流驅動時,液晶畫面顯示黑底白視窗畫面的垂直串音現象。

(a)沒有串音現象時顯示的均勻灰階畫面。

(b)垂直串音造成的不均勻畫面

圖6.採用圖框反轉交流驅動時,液晶畫面顯示白底黑視窗畫面的垂直串音現象。

1.2直行反轉(ColumnInversion)對垂直串音的影響

前面介紹了圖框反轉的垂直串音效應,現在繼續考慮直行反轉的交流驅動方式對垂直串音現象的影響。

首先考慮直行反轉時的垂直驅動電壓的極性,若在第i列、第j行上的垂直驅動電壓為正極性時,其相鄰的第j’行上的驅動電壓極性變為負極性驅動,所以在第i列、第j行上的液晶畫素電壓為:

(8)

如同前一節討論的方式,若是以第i列為參考依據時,從第1列至第i-1列的水平掃描週期時間內,第j行上的垂直驅動電壓極性都是與第i列,第j行上液晶畫素所儲存的電壓極性相反,從i+1至第N列的水平掃描週期時間內的垂直驅動電壓極性與第i列相同;

相反的,在相鄰的第j行上的電壓極性正好相反,意即從第1列至第i-1列的垂直驅動電壓極性與液晶畫素所儲存的電壓極性相同,從i+1至第N列的垂直驅動電壓極性是相反。

所以在整個圖框週期內,液晶畫素內儲存的RMS電壓如(9)式:

(9)

比較(7)式與(9)式,可以發現在造成串音的主要成份中((7)式與(9)式中的第二項),直行反轉由於相鄰垂直電極對於液晶畫素所造成的電容耦合效應有相互抑制的效果(參考(9)式第二項),所以垂直串音的現象因為採用直行反轉的交流驅動方式而獲得改善。

參考(9)式,若是假設Vm=Vm’時,(9)式可以改寫成如(10)式:

(10)

同樣的若(7)式的Vj=Vj’時,(7)式可以重寫成如(11)式:

(11)

參考(10)與(11)可以更明顯的看出圖框反轉的驅動方式與直行反轉的驅動方式之間的差異;

圖框反轉的方式中,水平方向上相鄰的電極對於液晶畫素是造成加成的耦合效應(因為電容耦合項為(α+β)),直行反轉是造成相互抑制的效應(因為電容耦合項為(α-β))。

1.3線反轉(LineInversion)對於垂直串音的影響

對於線反轉的交流驅動訊號而言,在同一條水平線上的影像驅動訊號極性是相同的,但是相鄰的水平掃描線上的垂直驅動訊號極性是相反的。

若是第i條(假設i是偶數時)水平掃描線上對應的垂直訊號電壓極性為正極性時;

在整個圖框掃描週期時間內,掃描第1條至第i-1條的水平掃描線時對應的訊號極性,偶數條的水平掃描線的訊號極性是負極性,奇數條掃描線上的驅動訊號為正極性;

而後在驅動第i條掃描線上的液晶畫素時,是將液晶畫素由正極性轉變成負極性;

剩下的第i+1條至最後一條掃描線的驅動訊號極性也是偶數條是負極性,奇數條是正極性。

所以對於第i條水平掃描線上的液晶畫素的有效RMS可以用(12)式來表示:

(12)

(12)式中的第二項對應在第i條掃描線以上的驅動訊號對於液晶畫素的影響,其中奇數條掃描線的影響是向正極性的方向(假設第i條掃描線為偶數條掃描線,而且液晶畫素所儲存的電荷電壓極性為正極性),偶數條掃描線的驅動電壓影響為向負極性的方向;

同理從第i+1條到第N條掃描線的驅動電壓影響與前述的相反。

將(12)式簡化可以獲得(13)式的結果:

(13)

觀察(13)式可以發現使用線反轉的交流驅動方式,由於奇數條與偶數條水平掃描線對於液晶畫素相反的電容耦合效應,使其具有與直行反轉相似的抑制作用,不同的地方在於直行反轉是相鄰垂直驅動訊號間的抑制作用,線反轉的交流驅動是由於相鄰的水平掃描線上相反的垂直驅動電壓極性,造成電容耦合效應的抑制。

所以採用直行反轉或是線反轉對於垂直方向上的畫面串音有明顯的抑制,可以改善畫面的顯像品質。

若是將(13)式簡化,同樣假設Vj=Vj’時,即是以顯像畫面為單調的灰階畫面為參考時,能夠更加的明瞭線反轉對於垂直串音的影響。

(14)

1.4點反轉(DotInversion)對於垂直串音的影響

點反轉的交流驅動方式可以視為直行反轉與線反轉交流驅動方式的組合,對於任意的一個液晶畫素,它與周圍其他四個液晶畫素的電壓極性都不相同。

若是顯示某一灰階畫面實,點反轉的驅動方式對於液晶畫素的影響如(15)式:

(15)

所以比較(15)式與其他驅動方式的分析結果,可以發現採用點反轉的驅動方式對於垂直串音的抑制效果最佳。

1.5水平串音的畫面分析

水平串音的形成主因在於各個驅動電極上的訊號電壓變化,經由液晶面板間的雜散電容耦合效應,影響到共通電極的參考位準,因而造成畫面的水平串音。

在此對於水平串音的分析主要是對於影像驅動訊號對於液晶畫素的充電方式所造成的效應做討論。

1.5.1串列輸入/並列輸出(SerialIn/ParallelOut)方式的影響

首先考慮訊號驅動的方式是採用串列輸入/並列輸出的架構,這也是一般大尺寸高解析度的液晶顯示器所採行的訊號驅動架構。

基本的動作方式是影像訊號依時間的順序依序的輸入至影像訊號驅動電路,驅動電路依序的將影像訊號儲存起來,等到一條水平掃描線的訊號全部都儲存起來後,再同時並行的輸出至液晶畫素。

所以此種方式對於共通電極的影響是發生在同一個時間點上。

以下的討論分別對於不同的極性驅動方式做更進一步的分析:

(a)採用圖框反轉或是線反轉的驅動方式:

考慮一個影像訊號電極的輸出電壓訊號對於共通電極的影響為αVm,水平解析度為N的影像畫面,對於共通電極的參考位準影響為NαVm,而且共通電極的影響會隨水平解析度的增加而愈加嚴重。

由於共通電極是一個RC的電路負載,所以共通電極上的參考位準變化可用RC放電曲線來描述,所以共通電極被耦合效應影響後,對於液晶畫素參考電壓位準的變化,必須視RC等效電路而定。

若RC常數大的話,代表放電時間長,所以產生的誤差電壓大,因而造成較嚴重的水平串音的效應。

參考圖7。

圖7.並列輸出方式,圖框反轉與線反轉之驅動方式對於共通電極的參考電位影響

(b)採用直行反轉或是線反轉的驅動方式:

採用直行反轉與點反轉的驅動方式,由於水平方向上,相鄰的液晶畫素的驅動電壓極性是相反的,所以對於共通電極的耦合影響會有相互抑制的效果,因而降低水平串音的現象。

1.5.2串列輸入/串列輸出(SerialIn/SerialOut)方式的影響

若訊號驅動的方式是採用串列輸入/串列輸出的架構,這也是一般小尺寸低解析度的低溫多晶矽液晶顯示器(LowTemperaturePoly-SiTFTLCDs)所採行的訊號驅動架構。

基本的動作方式是影像訊號依時間的順序依序的輸入至影像訊號驅動電路,驅動電路再依序的將影像訊號經由傳輸閘或是輸出驅動電路輸出至液晶畫素。

所以此種方式對於共通電極的參考電位影響是發生在不同時間點上。

考慮一個影像訊號電極的輸出電壓訊號對於共通電極的影響為αVm,水平解析度為N的影像畫面,對於共通電極的參考位準影響如圖8,而且共通電極的影響會隨水平解析度的增加而愈加嚴重。

由於共通電極是一個RC的電路負載,所以共通電極上的參考位準變化可用RC放電曲線來描述,由於共通電極被耦合效應影響的時間點不在同一時間點上,所以會造成更嚴重的共通電極的參考電位漂動問題。

若RC常數大的話,代表放電時間長,所以產生的誤差電壓大,因而造成更嚴重的水平串音的效應。

參考圖8。

圖8.串列輸出方式,圖框反轉與線反轉之驅動方式對共通電極的參考電位影響

2.低溫多晶矽薄膜電晶體液晶顯示器的電路架構

經由上述對於影像畫面的分析,我們可以明確的架構出LTPoly-SiTFTLCDs的電路架構,以及預測不同的架構對於畫面的影響;

此節主要是由驅動系統的觀點來討論不同的架構的優缺點:

2.1串列輸入/串列輸出(SerialIn/SerialOut)方式

NthGatePulse

(N+1)thGatePulse

Pixel’sChargeTime

Time

串列輸入/串列輸出方式的架構,對於高解析度大面積的TFTLCDS而言,是一個極不洽當的驅動方式,主要原因在於對於每個液晶畫素的充放電時間不相同,參考圖9,愈先取樣輸出的影像電壓,對於液晶畫素的充放電時間愈長,愈後取樣輸出的影像電壓,對於液晶畫素的有效充放電時間會愈短,因而造成畫面的左右亮度不均勻。

圖9.串列輸出架構的液晶畫素充放電時間

所以,對於大尺寸高解析度的液晶顯示器而言,不建議採用此種架構,因為隨著解析度的提高,表示一條水平掃描線的時間亦加縮短,因而會加重畫面的不均勻性;

隨著面板面積的增加,造成垂直驅動電極與水平驅動電極的負載增加,使得水平脈波與訊號電壓的驅動波形延遲時間增長,降低有對液晶畫素的有效充放電時間,同樣會增加畫面亮度分佈的不均勻性。

若為了克服亮度分佈不均勻的問題,可以採用如圖10的驅動架構,先將垂直電極走線上的雜散電容充電(此時雜散電容當作是訊號電壓的儲存電容),待依序充電完畢後在開啟水平脈波,但是此方式所面臨的問題是水平脈波的時間寬度大幅的減小,對於高解析度的影像畫面而言,所面臨的問題是整個畫面的液晶畫素充放電時間不夠,造成整個畫面的亮度不足,而且畫面對比劇降。

1Line

Pixel’sSamplingTime

GatePulse

圖10.串列輸出架構的驅動時序

串列輸入/串列輸出的驅動電路架構,如圖11所示。

參考圖11的架構,影像訊號的輸入有三個路徑,分別為Phase1,Phase2,以及Phase3;

對於彩色的液晶面板而言,這三個影像訊號輸入的路徑分別為紅色、綠色、及藍色。

若是VGA解析度的液晶面板,移位暫存器(ShiftRegister)的鐘控訊號(Clock)的頻率為25MHz。

若是黑白的液晶面板而言,Phase1、Phase2、及Phase3的影像訊號為原本的影像訊號除三倍頻後的低頻訊號,而且移位暫存器的鐘控訊號亦為25MHz的除三倍頻,約為8.33MHz;

如此架構的好處在於在玻璃上的積體化多晶矽驅動電路的操作頻率可以降低,同時對於每一條垂直訊號電極走線上的雜散電容充電的時間較原本增加三倍,由原本的40ns增加為120ns。

但是外部的影像訊號驅動電路的複雜度會增加許多。

參考圖12影像驅動分相電路的架構圖、圖13分相鐘控訊號時序圖。

圖11.串列輸入/串列輸出電路架構

圖12.影像驅動分相電路架構

參考圖12與圖13,LCK1、CLK2、及CLK3分別控制第一級上半部三個栓鎖電路(Latch1、Latch2、及Latch3),CLK4、CLK5、及CLK6分別控制第一級上半部三個栓鎖電路;

CLK7控制第二級的三個栓鎖電路。

第一級的兩組栓鎖電路將影像訊號交錯的取樣儲存起來,第二級的栓鎖電路則是經由內部多工器的選擇,交錯的選取上半部或是下半部栓鎖電路所取樣

儲存的影像訊號,經由CLK7的鐘控訊號將三個不同相位的影像訊號同步成為相同相位的訊號,再送至液晶顯示器的驅動電路。

PixelClock

CLK1

CLK2

CLK3

CLK4

CLK5

CLK6

CLK7

圖13.分相電路控制時序圖

2.2串列輸入/並列輸出(SerialIn/ParallelOut)方式

對於高解析度,大尺寸的液晶面而言,如果如同小尺寸的液晶面板一般,採用所謂的DriveronGlass的架構,就是將水平掃描脈波驅動線路與垂直影像驅動線路全部都設計佈局與玻璃之上,薄膜的製程採用多晶矽(Poly-Si)的元件,雖然可以提高電荷載子的移動率(Mobility),克服非晶矽(AmorphousSi)元件電荷載子移動率不足的問題,但是仍需要注意多晶矽元件在玻璃基板上製作電路的元件特性,是否達到高解析度的高頻操作要求。

例如對於SVGA的解析度而言,若是圖框重複率(FrameRate)為60Hz,對應的系統操作頻率需要39MHz;

若為XGA時,需要65MHz;

若是更高的SXGA的解析度而言,所需的操作頻率高達130MHz。

所以在高解析度、高頻的操作模式下,採用DriveronGlass的架構時,對於驅動電路的設計架構,必須先做評估:

在此提出三種驅動電路的架構以解決高頻動作所可能面臨的問題。

2.2.1影像分相電路架構(VideoMulti-PhaseStructure)

第一種架構如前節所介紹的影像分相架構,但是為了增加對於垂直驅動電極走線上雜散電容的充電時間,驅動電路的架構為串列輸入/並列輸出的架構。

若影像分相的數目愈多,垂直驅動電路的鐘控訊號頻率就愈低;

假若將影像分成10相,對於60Hz圖框重複率的VGA而言,鐘控訊號由原先的25MHz降至2.5MHz;

但是要注意,若是外部影像分相驅動電路(圖12)處理的影像訊號是類比影像訊號時,影像分相的數目愈多,最後在液晶面板上所顯示的影像畫面會愈模糊,這是由於分相電路的低通濾波特性所造成,而且隨分相數目的增加,低通的效果會愈明顯;

因此,若採用影像分相電路架構時,對於影像分相的數目需要多考慮,同時分相數目過多時,影像分相電路的控制時序會變的更複雜,所需的處理電路亦會增加許多。

ShiftRegisterArray

Clock

Start

InputLatchArray

OutputLatchArray

OutputBufferArray

OutputLatch

Video1

Video2

Video3

OutputChannels

圖14.並列輸出驅動電路架構

參考圖14、移位暫存器(ShifterRegisterArray)依序的送出控制訊號控制輸入栓鎖暫存器(InputLatchArray),輸入栓鎖暫存器將影像訊號依序的取樣儲存起來,等到一條水平掃描線上的影像訊號全部都被取樣儲存後,利用輸出栓鎖訊號將輸入栓鎖暫存器所儲存的影像資料轉移至輸出栓鎖暫存器(OutputLatchArray),同時輸出對應的驅動電壓至液晶面板上,在此同時輸入栓鎖暫存器再繼續取樣儲存下一條水平線的影像訊號。

由以上的動作方式可知,輸出至液晶面板的驅動電壓作用時間長達一條水平掃描線的週期,所以與串列輸出的方式最大的不同,即是增加了對液晶面板上垂直驅動電極走線的雜散電容充電時間,改善顯像畫面的亮度不均勻性與低的畫面對比。

至於圖中的影像輸入訊號有三組,對於彩色的液晶面板而言,此三組的影像輸入訊號分別為紅色、綠色、與藍色。

此時驅動電路的鐘控訊號頻率每有降低三倍,仍然維持顯像系統的影像畫素更換頻率(PixelRate),若為三個相同顏色訊號的輸入影像訊號,此時驅動系統的鐘控訊號頻率即可較畫素更換頻率降低三倍。

2.2.2垂直畫面分割架構

另一種降低驅動系統頻率的方式是將顯像畫面分割成數個小的顯像掃描區域,每個顯像掃描區域都是同時的掃描顯示畫面。

這種分個畫面掃描的分是可以歸納成為兩類,一為垂直畫面分割,另一為時間擴展(TimingExpansion)的訊號處理架構。

這節先對垂直畫面分割的驅動架構做一簡單的分析與介紹。

首先參考圖15的液晶面板佈局方式,將一個液晶面板分割成為上下兩半,上面一半與下面一半的畫面是被同時驅動顯像,所以對於垂直訊號驅動電極走線的設計也與傳統的方式不同,傳統的垂直訊號電極佈局的方式是一條垂直訊號電極由面板的上方舖設到下方,若是對於VGA的驅動訊號而言,垂直方向的解析度為480條水平掃描線,所以一條垂直驅動訊號電極上便會連接480個液晶顯像畫素;

但是垂直畫面分割是將垂直訊號驅動電極走線分成上下兩半,上半部連接240個液晶畫素,下半部連接240個液晶畫素。

此種驅動架構使得每一條水平掃描線的週期成為傳統的兩倍,意即系統的操作率可以降低一半。

圖15.垂直分割掃描的液晶面板架構圖

從圖15中可以看出垂直影像驅動電路需要兩組,傳統的掃描方式只需要一組的垂直影像驅動電路。

對於外部的影像處理電路而言,影像電路處理的架構如圖16:

圖16.垂直畫面分割影像處理電路架構

參考圖16,輸入影像訊號先經由多工器選擇輸入至哪一個圖框緩衝記憶體。

當圖框緩衝記憶體A被多工器選擇輸入影像訊號儲存時,在同一時間圖框緩衝記憶體B將其所儲存的影像資料輸出至液晶面板的驅動電路。

反之,圖框緩衝記憶體A與B的處理動作交換;

為何要如此的架構設計?

其中原因為垂直分割畫面的掃描方式,在輸出影像訊號時記憶體所儲存的資訊內容不可以變更,所以需要兩組緩衝記憶體交互讀寫的動作。

在將影像訊號寫入緩衝記憶體時,寫入資料的順序是從第一個圖框