数字逻辑电路与系统设计蒋立平主编习题解答docxWord文档格式.docx

《数字逻辑电路与系统设计蒋立平主编习题解答docxWord文档格式.docx》由会员分享,可在线阅读,更多相关《数字逻辑电路与系统设计蒋立平主编习题解答docxWord文档格式.docx(74页珍藏版)》请在冰豆网上搜索。

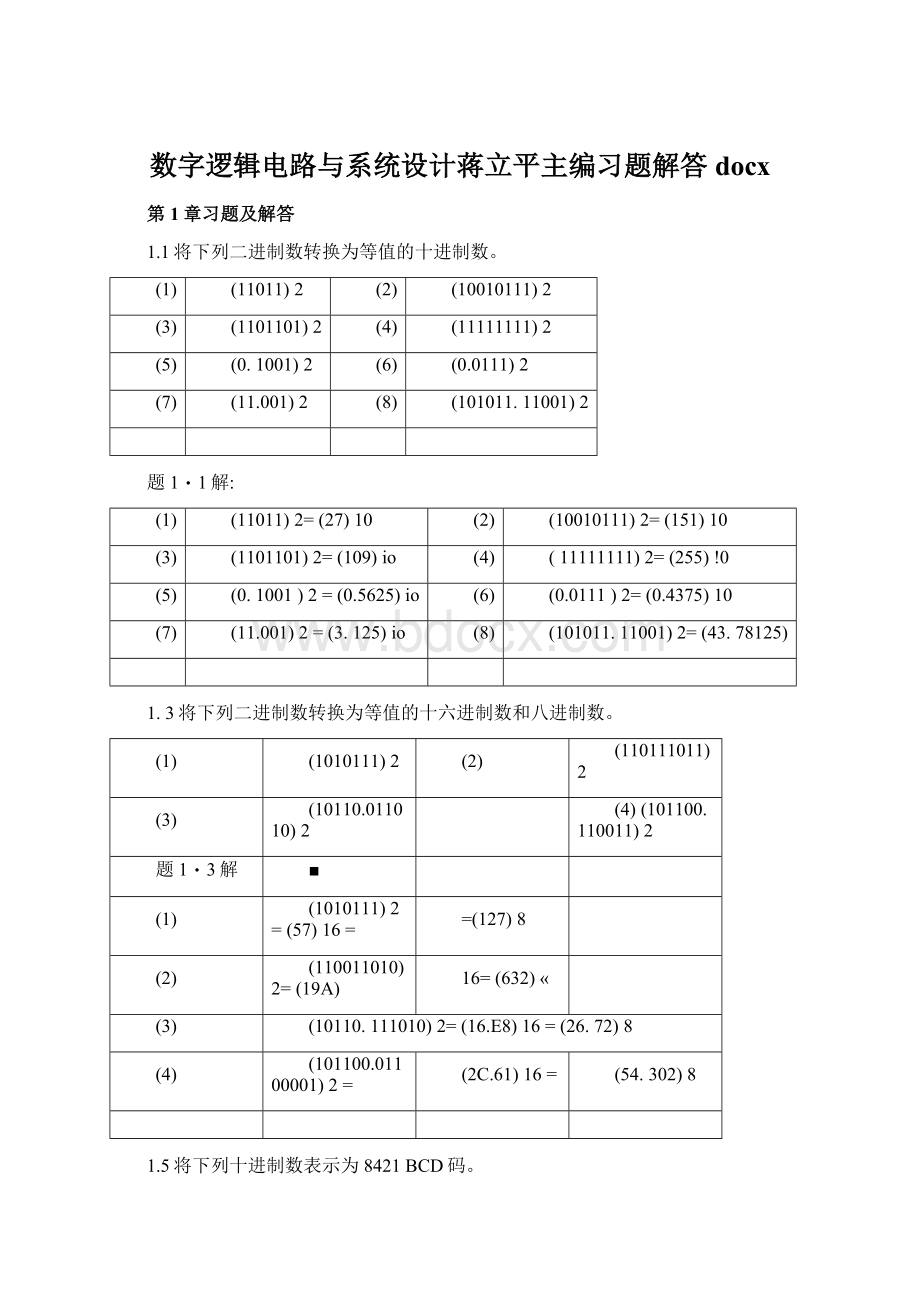

(1)(43)10—(01000011)8421BCD

(2)(95.12)】0=(10010101.00010010)842ibcd

(3)(67.58)io=(01100111.01011000)8⑵盹

(4)(932.1)io=(100100110010.0001)叱晦

1.7将下列有符号的十进制数表示成补码形式的有符号二进制数。

(1)+13

(2)-9

(3)+3

(4)一8

i二)(寸)

(三2)H61

(2)

噸6・I

up+CQPHOP+gp

^+T)H2

(寸)

("

)

(op)㊉(ayTG㊉g)p

(2)

。

沖廷気厶旦a脳阳猱壬6二2(11000)Hg+(g)z(3二0);

I+u)

囁卜・I®

Ag+

y—i

10

u

CQ

C^^—4◄

oooo

o

7—H

p

!

H

1<

、4

v—

H

♦4

(up)㊉(8P)H(3㊉CQWs

(g)

100

101

110

1

111

(4)证明AB+AC=AB+AC

A

B

C

AB+AC

1.11用逻辑代数公式将下列逻辑函数化成最简与或表达式。

(1)F=AB+AC+BC+ACD

(2)F=(A+Ac\a+CD-^-D)

(3)F=BD+D+D(B+C^AD+B)

(4)F=ABC+AD+{B+C)D

(5)F=AC+万C+B(A㊉C)

(6)F=(A㊉瞅3㊉C)

题1・11解:

(1)F=AB+AC+BC+ACD=A+BC

(2)F=(a+AC^A+CD+D)=A+CD

(3)F=~B万+万+D(B+C彷万+万)=万+入B+亍C

(4)F=ABC+AP+(B+C)D=ABC+D

(5)F=AC+BC+B(A㊉C)=AC+万C

(6)F=(A©

B\B®

C)=AB+BC+AC或=人〃+万k+瓜C

1.13用卡诺图将下列逻辑函数化成最简与或表达式。

(1)F=(A㊉3)C万+ABC+~ACD且4B+CD=0

(2)F=AC+AB且A,B,C不能同时为0或同时为1

(3)F(A,B,C)=X加(3,5,6,7)+工d(2,4)

(4)F(A,B,C,D)=工加(0,4,6,8,13)+工d(l,2,3,9,l0,11)

(5)F(A,5C,£

>

)=工m(0,l,8,10)+工d(2,3,4,5,l1)

(6)F(A,B,C,D)二工加(3,5,&

9,10,12)+》d(0,1,2,13)题1・13解:

(1)F=(A㊉B)C~5+ABC+~ACD且A3+CD=0

F=B+AD+AC

F=B+C

(3)F(A,B,C)=X加(3,5,6,7)+工d(2,4)

F=A+B

(4)F(A,B,C,D)二工加(0,4,6,&

13)+丫d(l,2,3,9,l0,11)

F=AD+ACD+B

(5)F(A,B,C,D)=工^(0,1,8,10)+工d(2,3,4,5,l1)

F=~BD+~AB或F=BD+AC

(6)F(A,B,C,D卜工加(3,5,8,9,10,12)+工d(0,l,2,l3)

F=~B万+兔方++

1.15将下列逻辑函数化简为或非一或非式。

(1)F=ABC+BC

(2)F=(A+C)(A+B+cJa+B+C)

(3)F=(ABC+BCp+~ABD

(4)F(A,5C,D)二工加(0,2,3,&

9,10,11,13)

题1・15解:

F=B+C+?

1+C+B+C或F=B+C+B+C+_A+B

(2)F=(/I+C)p+B+C^A+B+C)

F=B+C+4+C+A+B+C

(3)F(A,B,C,£

)=^m(0,l,8,9,l0)

F=jB+C+D+A+C

(4)F(A,B,C,D)=》加(0,2,3,8,9,10,11,13)

F=A+C+Z)+B+C+B+D

第2章习题及解答

2.1判断图P2.1所示电路中各三极管的工作状态,并求出棊极和集电极的电流及电压。

30kQ

o+6V

3kQ

.0=20

(b)

图P2.1

题2.1解:

(a)三极管为放人状态;

设VC£

5=0.3V^:

=6_O.7=o」06加I=0.106x50=5.3mA

B50c

%=0.7VVc=6.7V

(b)三极管为饱和状态;

T6—0.7c1rrAT6—0.3{aa

Ir==0.177mAIc==1.9mA

B303

2.3试画出图P2.3中各门电路的输出波形,输入A、B的波形如图中所示。

F2

F3

0>

t

图P2・3

题2.3解:

TF2

八F3

2.5指出图P2.5中各TTL门电路的输出为什么状态(高电、低电平或高阻态)?

图P2.5

题2.5解:

心为高阻;

佗为高阻;

F7=1;

心=0。

2.7在图P2.7各电路屮,每个输入端应怎样连接,才能得到所示的输出逻辑农达式。

=A®

图P2.7

题2.7解:

F}=A+B

F3=AB+CD

F4=A®

8

2.9试写出图P2.9所示CMOS电路的输出逻辑表达式。

(a)

图P2・9

题2.9解:

F}=AB=A+B;

F2=A+B=AB

2.11试写出图P2.11屮各NMOS门电路的输出逻辑表达式。

图P2.11

题2.11解:

F}=AQB;

F2=A(B+C);

F.=E\B+D)(^+C)+E•AB+CD

2.13试说明下列各种门电路中哪些可以将输出端并联使用(输入端的状态不一定相同)o

(1)具有推拉式输出级的TTL电路;

(2)TTL电路的0C门;

(3)TTL电路的三态输出门;

(4)普通的CMOSfl;

(5)漏极开路输出的CMOSH;

⑹CMOS电路的三态输Jllfjo

题2.13解:

(1)、(4)不可以;

(2)、(3)、(5)、(6)可以。

第3章习题及解答

3.1分析图P3.1所示电路的逻辑功能,写出输出逻辑表达式,列出真值表,说明电路完成

何种逻辑功能。

图P3.1

题3.1解:

根据题意可写出输出逻辑表达式,并列写真值表为:

F=AB+AB

F

该电路完成同或功能

3.2分析图P3.3所示电路的逻辑功能,写出输出片和竹的逻辑表达式,列出真值表,说明

电路完成什么逻辑功能。

图P3.3

题3・3解:

根据题意nJ写出输出逻辑表达式为:

F,=A㊉B㊉CF2=AB+BC+AC

列写真值表为:

Fi

该电路构成了一个全加器。

3.5写出图P3.5所示电路的逻辑函数表达式,其中以S3、S2、S】、So作为控制信号,A,B

作为数据输入,列表说明输出Y在S?

〜S。

作用下与A、B的关系。

S?

S3

SiSo

图P3.5

题3.5解:

由逻辑图可写出Y的逻辑表达式为:

Y=S/B+S2AB㊉S}B+S()B+A

图小的S3、S2、S|、So作为控制信号,用以选通待传送数据A、B,两类信号作用不同,

分析中应区别开来,否则得不出正确结果。

山于S3、S2、S】、S。

共有16种取值组合,因此输出Y和A、BZ间应有16种函数关系。

列表如下:

S品S。

Y

逻辑功能

S3S2SlS0

0000

缭A函数

1000

AB

禁止A函数

0001

A+B

或函数

1001

A@B

异或函數

0010

A+E

比较函数

1010

否B函数

0011

常】西数

1011

与非函效

0100

与函数1

1100

席0函数

0101

等B函数

1101

荣止B函数

0)10

AOB

同或函数

1110

或非函数

0111

比较函數

1111

否A函数

3.7设计一个含三台设备工作的故障显示器。

要求如下:

三台设备都正常工作时,绿灯亮;

仅一台设备发牛故障时,黄灯亮;

两台或两台以上设备同时发住故障时,红灯亮。

题3.7解:

设三台设备为A、B、C,正常工作时为1,岀现故障时为0;

F1为绿灯、F2为黄灯、F3为红灯,灯亮为1,灯灭为0。

根据题意可列写真值表为:

-ABC~~FiF2F3~

求得Fl、F2、F3的逻辑表达式分别为:

片=ABC\F2=ABC+ABC+ABC\F3=AB+BC+AC

根据逻辑表达式可画出电路图(图略)。

3.9设计一个组合逻辑电路,该电路有-三个输入信号ABC,三个输出信号XYZ,输入和输出

信号均代表一个三位的二进制数。

电路完成如下功能:

当输入信号的数值为0,1,2,3时,输出是一个比输入人1的数值;

当输入信号的数值为4,5,6,7时,输出是一个比输入小1的数值。

题3.9解:

XYZ

写出逻辑表达式为:

X=AB+BC+ACY=A㊉B㊉CZ=C

3.11试用与非门设计一个组合电路,该电路的输入X及输出Y均为三位二进制数,要求:

当0WXW3时,Y二X;

当4WXW6时,Y=X+1,且X>

6o

题3.11解:

因为X和Y均为三位二进制数,所以设X为x2x}x{),Y为y2y}y{),其屮花和

九为高位。

根据题意可以列写真值表如下:

兀2

兀0

『2

X

儿

化简后得到汕儿分别为

))=兀]+兀2兀()儿=勺兀()+兀2兀0

因为要用与非门电路实现,所以将匕兀儿写成与非一与非式:

y2=兀2

X=%1+-v2x0=x1-x2%0

=x2X()+x2X()=兀o•x2x0•x2•x2x0

根据逻辑表达式可曲出电路图(图略)。

3.13设A和B分别为一个2位二进制数,试川门电路设计一个可以实现Y=AXB的算术运算

电路。

题3.13解:

根据题意设A=aiao;

B=b1b0;

Y=y3Y2Y1Yo>歹U出真值表为

aia()

bi

bo

ys

Y2

y>

y()

a】ao

yi

分别求出y3』2,yi,yo的表达式为:

儿=ag)叭

y2=aibia()bQ

o=Mo

3.15判断逻辑函数F=JBD+B万+屈农十A万X,当输入变量ABCD按

0110->

1100,1111T1010,0011T()11()变化时,是否存在静态功能冒险。

题3.15解:

画出逻辑函数F的卡诺图如图所示:

00

00011110

01

11

(1)可以看出当输入变量ABCD从0110变化到1100时会经丿力两条途径,即0110T1110T1100和0110T0100T1100,由于变化前、后稳态输出相同,都为1,而且对应中间状态的输出也为1,故此变化不存在静态功能冒险。

(2)同理从1111到1010经历的两条途径1111^1110^1010存在1冒险;

而1111T1011T1010不存在静态功能冒险。

(3)从0011到0110经历的两条途径0011T0010T0110和0011^0111^0110,都会产牛0冒险。

第4章习题及解答

4.1用门电路设计一个4线一2线二进制优先编码器。

编码器输入为I3A2A1A),忑优先级最高,Ao优先级最低,输入信号低电平有效。

输出为YiYo,反码输出。

电路要求加一G输出端,以指示最低优先级信号兔o输入有效。

题4.1解:

根据题意,可列出真值表,求表达式,画出电路图。

其真值表.表达式和电路

图如图题解4・1所示。

由真值表可知6=忑忑石入。

A3A2A1Ao

YiYoG

000

00()

0010

0110

010

1001

1100

C1

1"

01

11

AiA()

、00011110

(a)真值表

Yo=A3A2+A3Ai

(b)求输出农达式

(c)编码器电路图

图题解4」

4.3试川3线一8线译码器74138扩展为5线一32线译码器。

译码器74138逻辑符号如图

4.16(a)所示。

题4.3解:

5线一32线译码器电路如图题解4.3所示。

图题解4.3

4.5写出图P4.5所示电路输出片和F2的授简逻辑表达式。

译码器74138功能表如表4.6所

图P4.5

题4.5解:

由题图可得:

Fi(C,5A)=》>

(0,2,4,6)=^

的(C,B,A)=J>

(1,3,5,7)=A

4.7试用一片4线一16线译码器74154和与非门设计能将8421BCD码转换为格雷码的代码

转换器。

译码器74154的逻辑符号如图4.17所示。

解:

设4位二进制码为,4位格雷码为R3R2R}R{)o根据两码Z间的关系可得:

他(B3,B2,d,B())=》>

(8〜15)=B3

7?

2(爲,爲,久禺)=工加(4〜11)=加4加5加6mi加9m\Qinw

=2^m(2~5」0〜13)=m21114m\\mnm\y

/?

()(鸟4,坊,竝)=2>

(1,2,5,6,9,10,13,14)=m\m2msmg加]()m\3加]4

则将译码器74154使能端均接低电平,码输入端从高位到低位分别接尿、禺、色B°

根据上述表达式,在译码器后加3个8输入端与非门,可得/?

2、&

,R。

尼可直接输出。

(图略)

4.9试用8选1数据选择器74151实现下列逻辑函数。

74151逻辑符号如图4.37(a)所示。

⑴F(A,B,C)=J>

(2,4,5,7)

(2)F(A,B,C)=[[M(0,6,7)

(3)F(A,B,C)=(A+B)(B+C)

(4)F(A,B,C,Z))=BC+ACD+ACD+~ABCD+4万C万

(5)F(4,B,C,D)=工m(0,2,3,5,6,7,&

9)+工d(1015)

题4.9解:

如将4、BC按高低位顺序分别连接到数据选择器74151的地址码输入端,将数据选择器的输出作为函数值Fo则对各题,数据选择器的数据输入端信号分别为:

(注意,数据选择器的选通控制端丽必须接有效电平,图略)

(1)D°

=D\=D3=2=0,D2=D4=D5=D7=}

(2)Do=£

6=£

7=0,D}=D2=D3=D4=D5=I

(3)D{}=D-,=D,=D6=0,£

)!

=D4=D5=D7=1

⑷DQ=D5=D,D}=D4=D,D2=D6=1,D.=D7=Q

(5)£

)()=£

),D2=D,=D3=D4=1,D5=D6=D7=0或1

4.11图P4.11为4线-2线优先编码器逻辑符号,其功能见图4.3(a)真值表。

试用两个4

线-2线优先编码器、两个2选1数据选择器和一个非门和一个与门,设计一个带无信

号编码输入标总的8线-3线优先编码器。

题4・11解:

由图4.3(a)真值表可见,当编码器无信号输入时,EO=1,因此可以利用EO

的状态来判断扩展电路中哪一个芯片有编码信号输入。

所设计电路如图题解4.11所示,

由电路可见,当高位编码器

(2)的£

0=0时,表示高位编码器

(2)有编码信号输入,

故选通数据选择器的0通道,将高位编码器

(2)的码送到丫必端;

当高位编码器

(2)的

EO=1时,表示高位编码器

(2)无编码信号输入,而低位编码器

(1)有可能有编码信

号输入,也可能无编码信号输入,则将低位编码器

(1)的码送到丫乙端(当无编码信号

输入输入时,孚;

=00)。

编码器输出的最高位码,由高位编码器

(2)的EO信号取反获

得。

山电路可见,EOy=1表示无编码信号输入。