燕大课设 病房呼叫系统程序设计版Word文档下载推荐.docx

《燕大课设 病房呼叫系统程序设计版Word文档下载推荐.docx》由会员分享,可在线阅读,更多相关《燕大课设 病房呼叫系统程序设计版Word文档下载推荐.docx(21页珍藏版)》请在冰豆网上搜索。

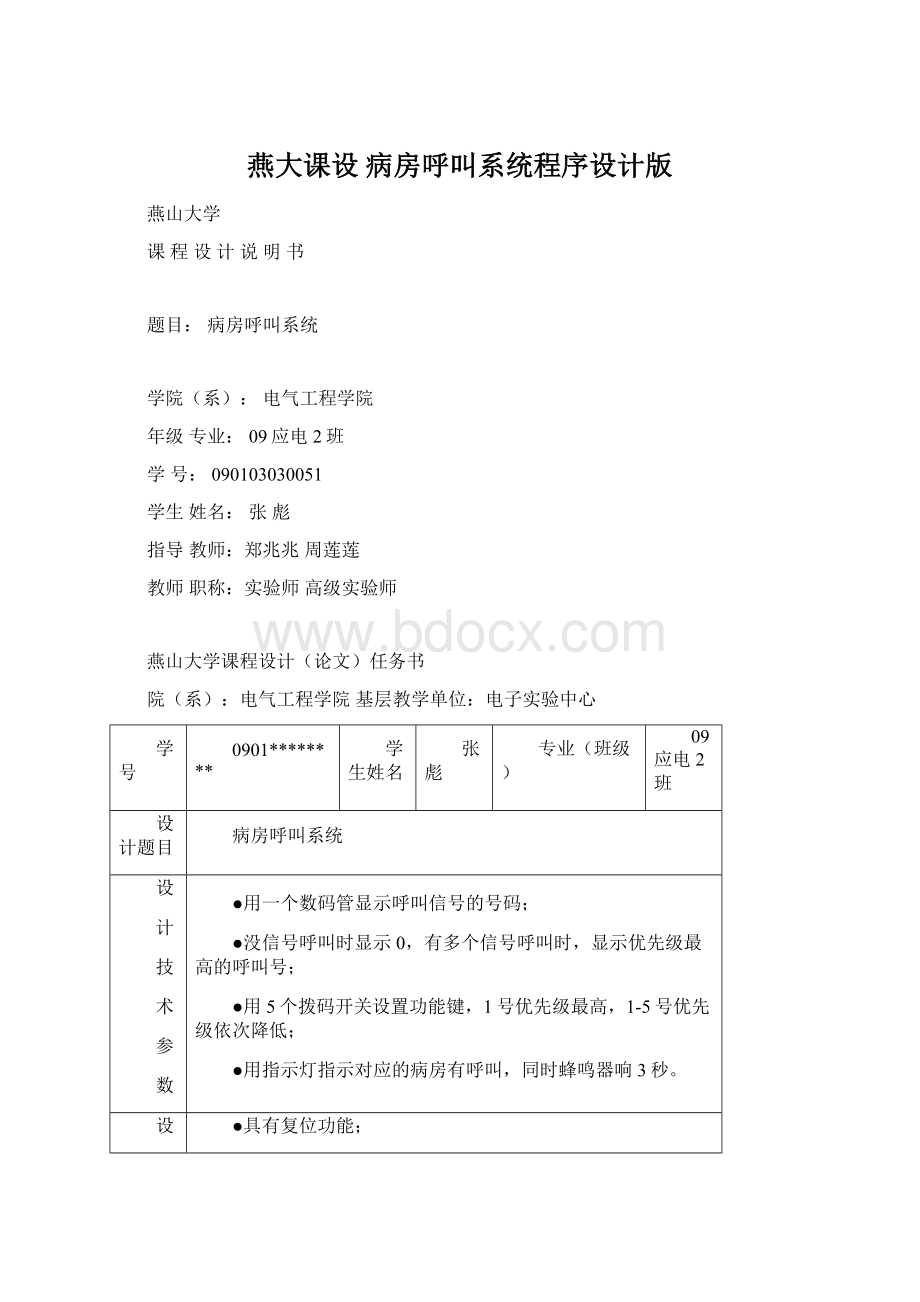

●用5个拨码开关设置功能键,1号优先级最高,1-5号优先级依次降低;

●用指示灯指示对应的病房有呼叫,同时蜂鸣器响3秒。

要

求

●具有复位功能;

●用动态数码管和双色点阵显示呼叫的病房号。

工

作

量

●学会使用Max+PlusII软件、VerilogHDL语言和实验箱;

●独立完成电路设计,编程下载、连接电路和调试;

●参加答辩并书写任务书。

划

1.了解EDA的基本知识,学习使用软件Max+PlusII,下发任务书,开始电路设计;

2.学习VerilogHDL语言,用VerilogHDL进行程序设计

3.学习使用实验箱,继续电路设计;

4.完成电路设计;

5.编程下载、连接电路、调试和验收;

答辩并书写任务书。

考

资

料

《数字电子技术基础》.阎石主编.高等教育出版社.

《EDA课程设计A指导书》.

指导教师签字

基层教学单位主任签字

说明:

此表一式四份,学生、指导教师、基层教学单位、系部各一份。

2011年12月30日

燕山大学课程设计评审意见表

指导教师评语:

①该生学习态度(认真较认真不认真)

②该生迟到、早退现象(有无)

③该生依赖他人进行设计情况(有无)

平时成绩:

指导教师签字:

2012年1月5日

图面及其它成绩:

答辩小组评语:

①设计巧妙,实现设计要求,并有所创新。

②设计合理,实现设计要求。

③实现了大部分设计要求。

④没有完成设计要求,或者只实现了一小部分的设计要求。

答辩成绩:

组长签字:

课程设计综合成绩:

答辩小组成员签字:

2012年1月5日

目录

第1章摘要………………………………………………………………………………1

第2章引言………………………………………………………………………………1

第3章课程设计容………………………………………………………………………1

3.1设计要求及说明……………………………………………………………………1

3.2VerilogHD设计源序………………………………………………………………6

3.3波形仿真图…………………………………………………………………………9

3.4管脚锁定及硬件连线………………………………………………………………11

3.5习题………………………………………………………………………………12

第4章总结………………………………………………………………………………12

参考文献……………………………………………………………………………………13

第一章

摘要

当今社会,随着老龄化的加剧,医院里的病人有增加的趋势,而医务人员的配置则显得原来越来越捉襟见肘。

原本本着服务病人为第一位,但每个床位附带一个医务人员又不现实的。

所以为了更好的服务生病人员,急需要一种紧急呼叫装置,放在床边,在病人需要的时候打开开关,发出紧急呼救信号,召唤不在身边的医生护士。

这样不但病患可以得到的更好的救治,同时也减少了对医护人员数量的需求,减少医院的压力。

第二章

引言

本人设计的为一个小型的紧急呼叫装置,只可以作为一个模型,但却可以完完全全模拟各种现实中的情况。

该呼叫装置有优先级的判断功能,即当不同优先级的开关打开后,只显示其优先级最高的相对应的现象,其他的优先级被屏蔽。

当优先级最高的开关被关掉之后,次优先级被释放,响应端做出相应响应。

第三章

课程设计的内容

3.1设计要求及说明:

3.11设计要求

要求设计一个病房呼叫系统,要求有五个拨码开关设置功能键,要求有置零端。

要求由动态数码管显示呼叫病房号码。

没有呼叫时显示0,还要求有优先功能,1号为最优先,1-5号依次降低。

指示灯也要求在有呼叫时对应的亮起来。

为了提高课设难度还增加了双色点阵与动态晶体管同时显示房间号,而且是八个一起工作。

同时还要求有蜂鸣器在呼叫时响三秒的时间。

3.12设计分析(初步)

①根据要求我们需要R、T1、T2、T3、T4、T5六个输入端。

还要求有双色点阵的响应这包括ROW1-8.LIN1-8,十六个输出端口。

动态晶体管包括位选SS0、SS1、SS2数选Q(1-7)共十个输出端。

再有指示灯的5个输出及一个蜂鸣器的输出,共计38个端口。

进一步分析之后我们发现时钟信号CLK,也是必须的。

②为完成该程序我们需要把任务分成几个部分:

优先编码模块、动态晶体管控制模块、指示灯控制模块、双色点阵控制模块、

蜂鸣器控制模块。

3.13各个模块的逻辑设计与分析

①优先编码模块:

由于只有1-5个拨吗开关,所以实际是5-3优先编码,当然由于有复位功能的要求,所以要求5-3优先编码模块要有复位开关R。

要求T1优先级最高1-5依次次之。

则真知表如下图。

R

T1

T2

T3

T4

T5

C1

C2

C3

1

x

输出信号为C1,C2,C3,值为000-101显示六种状态,数值为0-5,分别表示:

置0态(无优先状态),T1优先态,T2优先态,T3优先态,T4优先态,T5优先态。

②动态晶体管控制电路。

首先必须知道动态晶体管的工作方式,八个动态晶体管公用一组数选输入口,所以在要求所有的晶体管同时工作,这就要求通过位选输入信号端,要有很高的频率来不断地选择这八个动态数码管。

当位选信号分别为000-111时,选中数码管DS8A-DS1A。

为此我们急需要一个八位的计数器重复不断的输出000-111的信号。

在位选的同时,数选输出相应的数字信号。

这又需要对动态数码管进行编译,通过C的六状态写出动态数码管的7位数选信号,真知表见下图。

动态数码管数选信号编译:

Qa

Qb

Qc

Qd

Qe

Qf

Qj

显示

2

3

4

5

动态数码管位选信号编译

W

SS2

SS1

SS0

选中数码管

000

DS8A

001

DS7A

010

DS6A

011

DS5A

100

DS4A

101

DS3A

110

DS2A

111

DS1A

这里的W信号为八进制计数器提供的,由于这八个数不断变化,所以选中的数码管也不断变化,当变化速度足够快时,看起来就是一起工作的了。

③信号灯控制模块。

这一部分很简单,只要C1C2C3的六种不同组合的译出6组五位不同的高电平即可,即3-5译码器。

真值表如下图:

信号灯控制信号编译:

E1

E2

E3

E4

E5

④双色点阵控制模块

首先要了解双色点阵的工作原理,由于设计的要求只使用双的点阵的红色点部分(或绿色点)。

红(绿)灯亮要求这一点所在的这一行必须是低电平,而其所在的列为高电平。

如果要产生图形的话需要不停地轮换的给予1-8行低电平信号,在适时的情况下给予某列高电平。

这跟动态数码管的位选有些相似,不过这次要求的是八个信号,ROW1-8,需要由八位的计数器的输出信号

这个信号同时将对下面的双色点阵显示提供输入扫描信号。

双色矩阵ROW信号编译:

R1

R2

R3

R4

R5

R6

R7

R8

随着8进制计数器的输出信号W的变化,双色点阵依次选中ROW1-ROW8,并提供低电平。

与此同时如果对列施以相应的高电平信号的话,就可以产生想要的图形。

看下图,对LIN信号的编译即可产生0—5。

双色矩阵LIN信号编译:

当C=000,显示图象“0”

L1

L2

L3

L4

L5

L6

L7

L8

当C=001,显示图象“1”

0.

当C=010,显示图象“2”

0

当C=011,显示图象“3”

当C=100,显示图象“4”

当C=101,显示图象“5

⑤蜂鸣器控制模块

蜂鸣器的响应是根据C的变化,由于C的数值为0-5,当C=0时蜂鸣器不响,

开关打开当C第一次大于零,蜂鸣器想响一次,这时有一个优先级,它的大小由C表示,C越大优先级越小。

这时低级优先级,被屏蔽,如果此时有低级优先级被屏蔽,高级优先级被关闭后,次级的应该会被释放显示出来,所以要一直监视C的变化,当C增大时,次级优先级释放,蜂鸣器要再响三秒。

至于蜂鸣器的三秒持续,我们用循环解决,使用1024HZ的频率时钟,计数3072,就可以延时三秒的时间,误差不会超过1ms。

这里蜂鸣模块,没有真值表,功能的实现完全由程序完成。

程序在这里就不再赘述,因为下节将会详细阐明。

3.2VerilogHDL设计源序

以下即为所有程序:

moduleWORK(E,SS,D,ROW,LIN,Q,T,R,CLK);

/**********************初始化标出I/O口及中间变量*************************/

input[1:

5]T;

inputR;

inputCLK;

outputD;

output[1:

5]E;

output[2:

0]SS;

8]ROW;

8]LIN;

7]Q;

regD;

integerA;

integerB;

reg[1:

reg[2:

reg[0:

2]C;

3]W;

3]Q_TIMED;

/********主程序,输出动态?

体管控制信号Q,SS,和指示等信号E,以及控制信C,******/

always@(TorR)

begin

casex({R,T})

'

b1xxxxx:

beginQ='

b1111110;

C='

b000;

E='

b00000;

end

b000000:

b01xxxx:

b0110000;

b001;

b10000;

b001xxx:

b1101101;

b010;

b01000;

b0001xx:

b1111001;

b011;

b00100;

b00001x:

b0110011;

b100;

b00010;

b000001:

b1011011;

b101;

b00001;

endcase

always@(posedgeCLK)

case(W)

b000:

SS='

b001:

b010:

b011:

b100:

b101:

b110:

b110;

b111:

b111;

/******************双色点阵,在C,W控制下实现0—5的图形输出****************/

/************八进制计数程序段,为双色点阵提供扫描信号*************/

if(Q_TIMED<

b111)Q_TIMED=Q_TIMED+1;

elseQ_TIMED='

该处即为八进制计数器的编译程序

W=Q_TIMED;

always@(CorW)

begin

case({C,W})

/********************信号C=0,输出0图象****************************/

beginROW='

b01111111;

LIN='

b00111100;

b10111111;

b01000010;

以下为双色矩阵的程序编译部分

b000010:

b11011111;

b000011:

b11101111;

b000100:

b11110111;

b000101:

b11111011;

b000110:

b11111101;

b000111:

b11111110;

/********************信号C=1,输出1图象****************************/

b001000:

b00001000;

b001001:

b00011000;

b001010:

b00101000;

b001011:

b001100:

b001101:

b001110:

b001111:

/********************信号C=2,输出2图象****************************/

b010000:

b010001:

b010010:

b00000010;

b010011:

b00000100;

b010100:

b010101:

b00010000;

b010110:

b00100000;

b010111:

b01111110;

/*******************信号C=3,输出3图象*****************************/

b011000:

b00111110;

b011001:

b011010:

b011011:

b011100:

b011101:

b011110:

b011111:

b00000000;

/*******************信号C=4,输出4图象*****************************/

b100000:

b100001:

b00001100;

b10