SSI接口Word格式文档下载.docx

《SSI接口Word格式文档下载.docx》由会员分享,可在线阅读,更多相关《SSI接口Word格式文档下载.docx(7页珍藏版)》请在冰豆网上搜索。

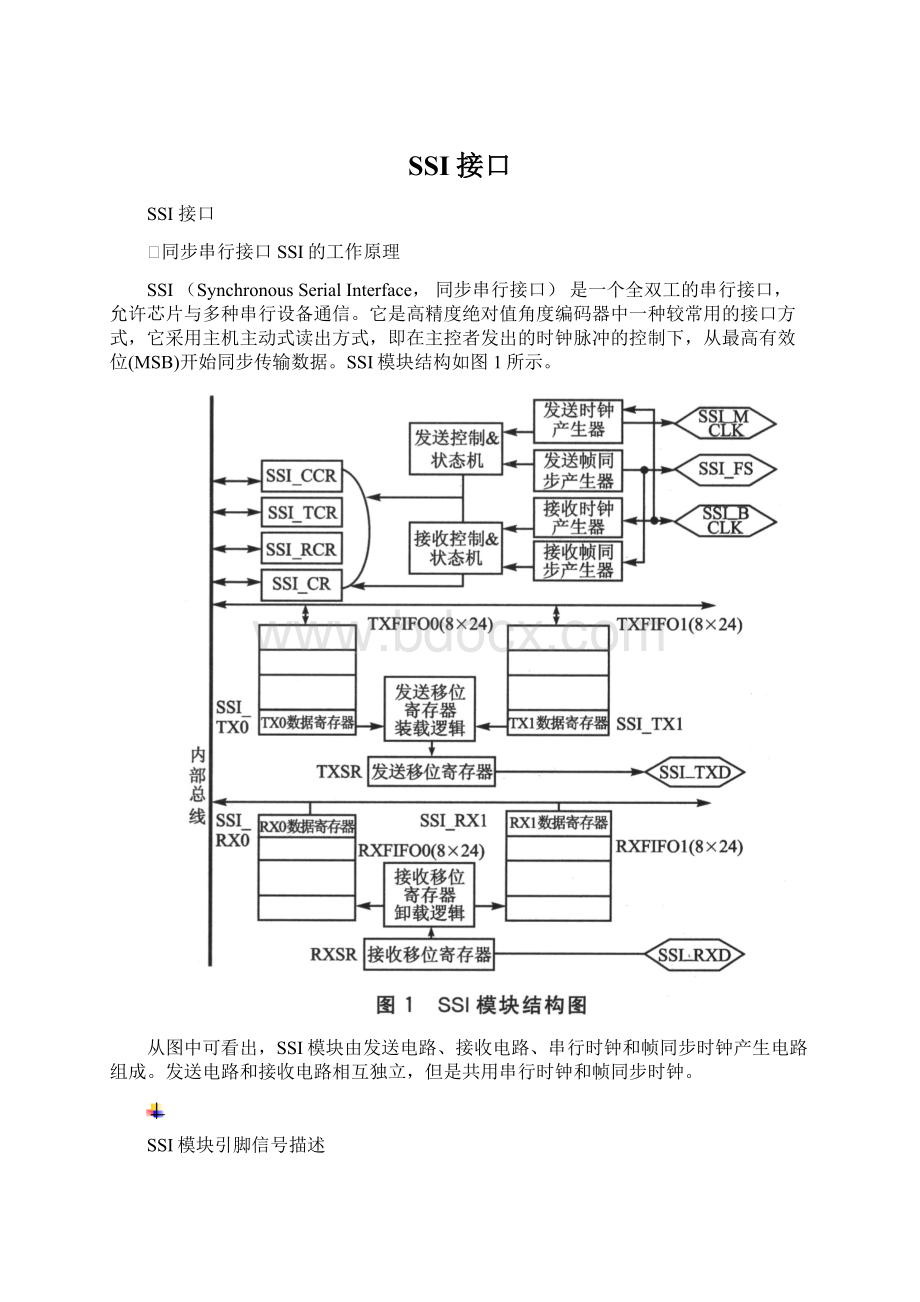

发送电路和接收电路相互独立,但是共用串行时钟和帧同步时钟。

SSI模块引脚信号描述

SSICLKIN:

SSI时钟输入信号。

SSI_BCLK:

SSI串行比特时钟。

SSI_MCLK:

SSI串行主时钟信号,在SSI主模式下,

该信号也作为过采样时钟信号。

SSI_FS:

SSI串行帧同步信号。

SSL_RXD:

SSI串行接收数据信号。

SSI_TXD:

SSI串行发送数据信号。

SSI的操作模式

SSI有3种基本同步操作模式:

普通模式、网络模式和门时钟模式。

普通模式是最简单的模式,一帧内只能传输一个字,而且每一帧都需要帧同步信号来控制同步;

网络模式主要用于多时隙的情况下,一帧内可以传输2个字到32个字不等;

门时钟SSI_BCLK模式下,串行比特时钟SSI_BCLK指示了发送引脚或接收引脚上的有效数据,所以不需要帧同步信号。

除了上述3种基本模式外,针对音频上的应用,SSI还支持两种衍生模式——I2S模式和AC97模式,分别用于传输I2S和AC97音频格式数据。

SSI的初始化

初始化SSI模块的正确顺序:

①上电或重启SSI(SSI_CR[SSI_EN]=0),即关闭SSI模块功能。

②配置SSI模块。

涉及的寄存器包括控制寄存器SSI_CR、中断允许寄存器SSI_IER、发送配置寄存器SSI_TCR、接收配置寄存器SSI_RCR和时钟控制寄存器SSI_CCR。

③通过SSI_IER寄存器设置必要的中断或DMA。

④设置SSI_CR[SSI_EN]=1允许SSI模块功能。

⑤设置SSI_CR[TE/RE],开始发送/接收数据。

SSI的工作过程

(1)发送数据

单通道时,数据从串行发送数据寄存器SSI_TX0中传到发送移位寄存器TXSR中,再通过串行发送引脚SSI_TXD发送出去,然后根据用户设置情况决定是否产生发送中断。

如果发送缓冲区TXFIFOO被允许,则SSI_TX0继续从TXFIFOO中取数据,直到TXFIFOO中的数据全部被发送,再通过用户设置情况决定是否产生发送中断。

双通道时,发送移位寄存器TXSR交替从SSI_TX0和SSI_TXl中取出数据。

(2)接收数据

单通道时,数据从串行接收引脚SSI_RXD进来,由接收移位寄存器RXSR传输给接收数据寄存器SSI_RX0,再根据用户设置情况决定是否产生接收中断。

如果接收缓冲区RXFIFOO被允许,则SSI_RX0将数据写入RXFIFOO,并继续从接收移位寄存器中获取数据。

双通道时,接收移位寄存器RXSR交替将数据传输给SSI_RX0和SSI_RXl。

SynchronousSerialInterface(SSI)isawidelyusedserialinterfacestandardforindustrialapplicationsbetweenamaster(e.g.controller)andaslave(e.g.sensor).SSIisbasedonRS422[1]standardsandhasahighprotocolefficiencyinadditiontoitsimplementationovervarioushardwareplatforms,makingitverypopularamongsensormanufacturers.SSIwasoriginallydevelopedbyMaxStegmannGMBHin1984fortransmittingthepositiondataofabsoluteencoders-forthisreason,someservo/driveequipmentmanufacturersrefertotheirSSIportasa"

StegmannInterface"

.ItwasformerlycoveredbytheGermanpatentDE3445617whichexpiredin1990.Itisverysuitableforapplicationsdemandingreliabilityandrobustnessinmeasurementsundervaryingindustrialenvironments.

Introduction

SSIisasynchronous,pointtopoint,serialcommunicationchannelfordigitaldatatransmission.Synchronousdatatransmissionisoneinwhich,thedataistransmittedbysynchronizingthetransmissionatthereceivingandsendingendsusingacommonclocksignal.Sincestartandstopbitsarenotpresent,thisallowstheuseoftransmissionbandwidthformoremessagebitsandmakesthewholetransmissionprocesssimplerandeasier.

Figure1-SSIPointtoPointCommunication

Ingeneral,asmentionedearlieritisapointtopointconnectionfromamaster(e.g.PLC,Microcontroller)toaslave(e.g.Rotaryencoders).Themastercontrolstheclocksequenceandtheslavetransmitsthecurrentdata/valuethroughashiftregister.Wheninvokedbythemaster,thedataisclockedoutfromtheshiftregister.Themasterandslavearesynchronizedbythecommonclockofthecontroller.

TheCLOCKandDATAsignalsaretransmittedaccordingtoRS-422standards.RS-422,alsoknownasANSI/TIA/EIA-422-B,isatechnicalstandardthatspecifiestheelectricalcharacteristicsofthebalancedvoltagedigitalinterfacecircuit.Dataistransmittedusingbalancedordifferentialsignallingi.e.theCLOCKandDATAlinesarebasicallytwistedpaircables.

Inputscanuseanopto-couplerforgalvanicisolation(Formoredetailssee[1])thatcanbedrivenbyRS-422/485levels.TheDATAoutputofthesensorisdrivenbyaRS-422/485linedriver.Differentialsignallingimprovestheresistancetoelectromagneticinterference(EMI),hencemakingitareliablecommunicationchanneloverlongtransmissionlengthsandharshexternalenvironments.

SSIDesign

Theinterfacehasaverysimpledesignasillustratedintheabovefigure.Itconsistsof2pairsofwires,onefortransmittingtheclocksignalsfromthemasterandtheotherfortransmittingthedatafromtheslave.Theclocksequencesaretriggeredbythemasterwhenneedarises.Differentclockfrequenciescanbeusedrangingfrom100kHzto2MHzandthenumberofclockpulsesdependsonthenumberofdatabitstobetransmitted.

ThesimplestSSIslaveinterfaceusesaretriggerablemonostablemultivibrator(monoflop)tofreezethecurrentvalueofthesensor.ThecurrentfrozenvaluesoftheslavearestoredinShiftregisters.Thesevaluesareclockedoutsequentiallywheninitiatedbythecontroller.Thedesignisbeingrevolutionizedwiththeintegrationofmicrocontrollers,FPGAsandASICsintotheinterface.

Thedataformatisdesignedinsuchawaytoensurepropercommunicationofdata.Theprotocolforthedatatransmissionisbasedonthreedifferentsubsequentparts(Leading-”1"

->

Data-Bits->

Trailing-"

0"

).Themainsignificanceofthistypeofformatistoensuretheproperworkingoftheinterfaceandhencesecuredatatransmissionfreefromanyhardwareorsoftwareerrors.

InidlestatetheCLOCKisonhighlevelandalsothesensoroutputisonhighlevel,sothatitcanbeusedfordetectinganybrokenwirecontacts.Thishelpsinobservingtheproperworkingconditionoftheinterface.

Aftern-CLOCKpulses(risingedges)thedataiscompletelytransmitted.WiththenextCLOCKpulse(risingedgen+1)thesensoroutputgoestolowlevelwhichcanbeusedtodetectashortcircuitinthecable.Ifitishighevenaftern+1risingedgesthenitmeansthattheinterfacehasashortcircuit.

Readingsfrommultipleslaves(upto3)canbeenabledatthesametimebyconnectingthemtoacommonclock.However,toavoidgroundloopsandelectricallyisolatetheslave,completegalvanicisolationbyopto-couplersisneeded.

SSITimingandTransmission

ThefollowingkeywordswillbeusefulinunderstandingtheSSIdatatransmissionprocedure.

‘tm’representsthetransfertimeout(Monofloptime).Itistheminimumtimerequiredbytheslavetorealisethatthedatatransmissioniscomplete.Aftertm,thedatalinegoestoidleandtheslavestartsupdatingitsdataintheshiftregister.

‘tp’representsthepausetime.Itisthetimedelaybetweentwoconsecutiveclocksequencesfromthemaster.

‘tw’representstherepetitiontime.Itistheminimumtimeelapsedbetweenretransmissionsofthesamedataandisalwayslessthantm.

‘T’representsthewidthofeachclockcycle.Itisthetimetakenbetweentwofallingortworisingedgesinacontinuousclocksequence.

MSB:

Mostsignificantbit

LSB:

Leastsignificantbit

SingleTransmission

SingleTransmissionoftheSSIInterface:

1.Freezingofthedata.2.TransmissionofthefirstDatabit.3.Endoftransmission.4.afterthepausetimetheSSIwentbacktoidlestate-isreadyfornewtransmission.

ThediagramillustratesthesingledatatransmissionusingSSIprotocol:

TheSSIisinitiallyintheidlemode,whereboththedataandclocklinesstayHIGHandtheslavekeepsupdatingitscurrentdata.

Thetransmissionmodeisevokedwhenthemasterinitiatesatrainofclockpulses.Oncetheslavereceivesthebeginningoftheclocksignal

(1),itautomaticallyfreezesitscurrentdata.Withthefirstrisingedge

(2)oftheclocksequence,theMSBofthesensor’svalueistransmittedandwithconsequentrisingedges,thebitsaresequentiallytransmittedtotheoutput.

Afterthetransmissionofcompletedataword(3)(i.e.LSBistransmitted),anadditionalrisingedgeoftheclocksetstheclocklineHIGH.ThedatalineissettoLOWandremainsthereforaperiodoftime,tm,torecognizethetransfertimeout.Ifaclocksignal(data-outputrequest)isreceivedwithinthattime,thesamedatawillbetransmittedagain(multipletransmission).

TheslavestartsupdatingitsvalueandthedatalineissettoHIGH(idlemode)iftherearenoclockpulseswithintime,tm.Thismarkstheendofsingletransmissionofthedataword.Oncetheslavereceivesaclocksignalatatime,tp(>

=tm),theupdatedpositionvalueisfrozenandthetransmissionofthevaluebeginsasdescribedearlier.

MultipleTransmissions

Multipletransmission

Multipletransmissionsofthesamedatahappensonlyifthereiscontinuousclockingevenafterthetransmissionoftheleastsignificantbiti.e.theclockpulsesdoesnotallowthemonofloptogotosteadystate.Thisisillustratedbelow.

Theinitialsequencesarethesameasthatofthesingletransmission.IntheidlestatetheCLOCKandDATAlinesarehighbutwiththearrivalofthefirstfallingedgethetransmissionmodeisevokedandthesimilarlythedatabitsaretransmittedsequentiallystartingwiththeMSBwitheveryrisingedge.ThetransmissionoftheLSBmeansthatthetransmissionofthedataiscompleted.AnadditionalrisingedgepushesthedatalinetoLOWsignifyingtheendoftransmissionoftheparticulardata.

But,iftherearecontinuousclockpulsesevenafterthen(i.e.thenextclockpulsescomesintimetw(<

tm))thevalueoftheslaveisnotupdated.Thisisbecausethemonoflopisstillunsteadyandthevalueintheshiftregisterstillcontainsthesamevalueasbefore.Sowiththenextrisingedge,i.e.afterthen+1risingedge,thetransmissionofthesamedatacontinuesandtheMSBofdatatransmittedearlierisre-transmittedattheendoftw.

Then,itfollowsthesameprocedureasearliertransmissions,leadingtomultipletransmissionsofthesamedata.Thevalueoftheslaveisupdatedonlywhenthetimingbetweentwoclockpulsesismorethanthetransfertimeout,tm.

Multipletransmissionisusedtocheckthedataintegrity.Thetwoconsecutivereceivedvaluesarecompared,transmissionfailuresareindicatedbydifferencesbetweenthetwovalues.

InterruptingTransmission

Thetransmissionofdataiscontrolledbythemasterandthetransmissioncanbeinterruptedatanyt