Modelsim 教程.docx

《Modelsim 教程.docx》由会员分享,可在线阅读,更多相关《Modelsim 教程.docx(16页珍藏版)》请在冰豆网上搜索。

Modelsim教程

Modelsim教程(转)

快速上手四部曲:

建立Project、引進HDLFiles、Compile、模擬(Simulate/LoadingandRun)

1.建立一個新的Project

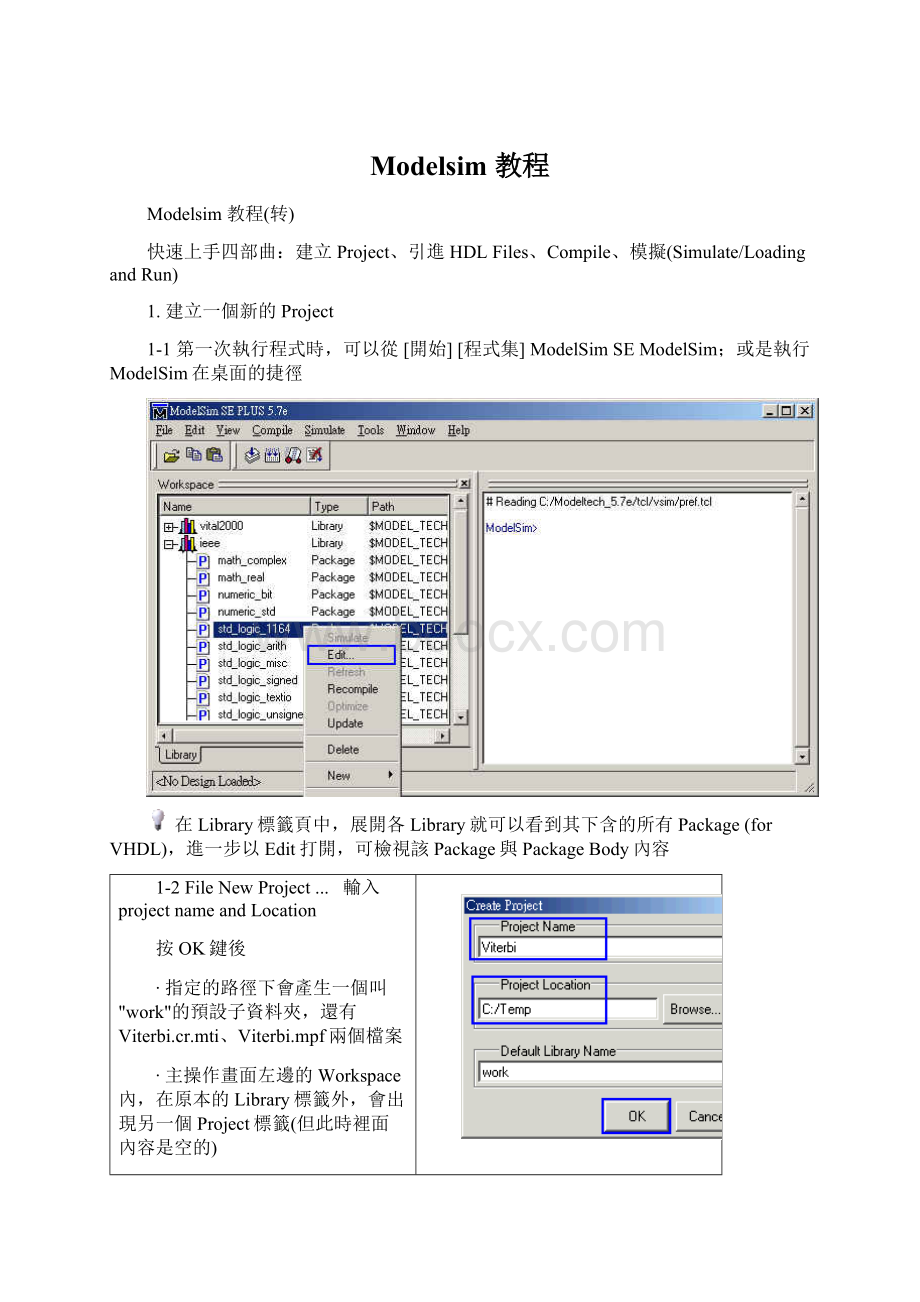

1-1第一次執行程式時,可以從 [開始][程式集]ModelSimSEModelSim;或是執行ModelSim在桌面的捷徑

在Library標籤頁中,展開各Library就可以看到其下含的所有Package(forVHDL),進一步以Edit打開,可檢視該Package與PackageBody內容

1-2 File New Project... 輸入projectnameandLocation

按OK鍵後

∙指定的路徑下會產生一個叫"work"的預設子資料夾,還有Viterbi.cr.mti、Viterbi.mpf兩個檔案

∙主操作畫面左邊的Workspace內,在原本的Library標籤外,會出現另一個Project標籤(但此時裡面內容是空的)

∙還會蹦出另一個"AdditemstotheProject"視窗

.mpf檔儲存的是此project的相關資料,下次要開啟此project就是利用File Open Project... 開啟此.mpf

若要移除之前建立的project,請從 FileDelete Project... 移除

2.載入Project的HDLsourcecodes

按"AdditemstotheProject"視窗中的"AddExistingFile" (或是從File Addto Project ExistingFiles...)

HDLfiles擺放的位置,路徑名稱不能有中文,否則軟體會抓不到files

關掉"AdditemstotheProject"視窗,此時的Project下出現了HDLFile,一堆問號表示這些檔案都還沒compile。

如果要對project新增或移除HDLFile:

在Workspace內按滑鼠右鍵,選擇 AddtoProjectExistingFile... (新增)

RemovefromProject (移除)

3.Compile

在Project標籤頁內,選定任一檔案,按滑鼠右鍵選擇 CompileCompile All 或是直接按icon

CompileOut-of-Data只重新compile有修改過的檔案(比較節省時間,故也較常用)

此刻只做Compile還沒做Simulate,而ModelSim必須要作完Simulate(Loading)後才會把所有檔案link起來。

如果compiler的結果出現有errors或warnings的訊息,直接在該訊息上雙擊,即可進一步帶出詳細的訊息說明。

如果您處理的是VHDLproject,那在做Compile前,先在Project標籤頁內,選定所有檔案,按滑鼠右鍵選擇"Properties"做如下設定:

3.Simulate(Loading)

切換到Library標籤頁,展開"work"目錄,其下可以看到此project包含的所有檔案,檔案前的符號"M",表示這些檔案的性質是"Module";如果你寫的是VHDL程式那檔案前所看到的符號會變成"E"(Entity)and"A"(Architecture)。

如果compiler完,work目錄底下仍然看不到東西,無法展開,請稍等5~10秒(等程式update最新狀態),或是按滑鼠右鍵選擇"Update"重新整理

4-1直接以滑鼠左鍵雙擊要Simulate的檔案,或是按滑鼠右鍵選擇Simulate。

此處選擇要Simulate(Loading)的檔案不一定要是top-levelfile,但如果你選的不是top-levelfile,project中的sub-ciricuit必須一個一個load,比較麻煩。

請注意,這裡的"Simulate"並沒有真的做模擬,只是把程式"Loading"進來,並將sub-module彼此間link起來

Loading要simulate的檔案的動作,也可以按Simulateicon 來完成

執行以上動作時,如果再附加一個設定步驟:

到Options標籤頁下,核選"Enablesourcefilecoverage",即可在模擬的程序中,附帶幫你檢查testbench對於if/caseconditionalstatement的模擬涵蓋率。

執行完Simulate(Load)的動作後,程式會自動再跳出兩個標籤頁Sim與Files,此時在Sim下可以看到整個Project的Hierarchy關係

要編輯HDLfile,可以從Project(顯示檔案的狀態)或File標籤頁內雙擊HDL檔案以開啟編輯視窗(editwindow)。

sim標籤頁內雖然也有列出所有HDL檔案,但雙擊HDL檔案開啟的是來源視窗(sourcewindow),不能edit。

檔案編輯(修改)完成(存檔)後,回到Project標籤頁內看該檔案的狀態時,會發現它變成未compile的問號,要重新對它做compile,把目前的Simulate關掉(SimulateEndSimulation...),再重新load一次,才能對新的程式做模擬。

若要查看此project架構,必須切換到Sim標籤頁;不像VeriLoggerPro只要Compiler完,就可以在同一個Project畫面下看到整個projectstructure/hierarchy。

Sim標籤頁另外一個有趣的功能是:

在Sim標籤頁內選定哪一個module,其相對的內容會自動update於signals、source、edit...等window(如果你有開啟這些視窗的話)。

另外,source與editwindow兩者都可用來查看模擬時的某一個變數值或設定中斷點,但前者不可編輯。

∙Project標籤頁用以顯示HDL檔案的狀態(也可以開啟其編輯視窗)

∙Library 標籤頁用以選定要Simulate的檔案

∙Sim標籤頁用以查看projectstructure與開啟某module的來源視窗

∙File標籤頁用以開啟某HDL檔案的編輯視窗

==> 四個功能拆成四個設定頁,這是ModelSim比較耍寶的地方。

以下,我們接著要把想觀察的訊號引出來,然後"Run" simulation...

4-2在Sim標籤頁內選定top-levelfile(system.v),打開signalswindow:

ViewSignals 就可以看到top-levelfile的所有I/Osignal。

4-3在signalswindow的左半邊欄位內選定想看的訊號(如orig_bit_s1、y1_s1、y2_s1、decoded_coulmn_s1),按滑鼠右鍵 AddtoWave SelectedSignals,會跳出另一個"wavewindow"並把您想觀察的訊號都列出來

直接把signalswindow的訊號拖曳到wavewindow也可以(訊號的排列次序也可以用左鍵拖曳搬移)。

訊號的排列次序,可以直接用滑鼠拖曳調整。

如果要看的是module/sub-module所有訊號,4-2~4-3步驟可以一次完成:

4-4切回主視窗,Simulate Run Run100ns --> 預設Runlength=100ns(一次跑100ns;可以更改)

Simulate RunRun-All --> 跑到按"Break" 才暫停

--> 按"ContinueRun" 則繼續

Simulate Run Step --> 單步執行程式(fordebugging)

Simulate RunRestart --> 重新執行模擬

程式執行暫停或是跑到中斷點時,要查看任一訊號或變數的數值,方法有三種

∙從wavewindow查看

∙游標指到sourceoredit視窗內的該變數,即會顯示該變數當時的數值

∙View Variables

模擬結果如下

如果想要看所有波形的範圍:

View ZoomZoom Full

以滑鼠左鍵在波形顯示區域點一下,就會出現黃色的垂直座標線(cursor,參閱step5-4)。

直接在訊號波形上雙擊,會帶出Dataflowwindow(step5-3);如果你是在紅色的(unknown)線上雙擊,還可以進一步的在Dataflowwindow內選定該unknownsignal的wire,按滑鼠右鍵選擇 TraceX 協助你debug

如果訊號不想以預設的二進位表示,可以在wavewindow內選定該訊號名稱,按滑鼠右鍵選擇SignalProperties...,然後選擇表示方法(如十進位表示Decimal)。

5.Dataflowwindow (fordebuggingandtracing)

"Dataflowwindow"可用來檢視所設計的電路,其訊號的實際連接情況(Drivers/Receivers),也就是顯示訊號在執行模擬的過程中,經過哪些程序(process),開啟的方法有兩個:

∙直接雙擊wavewindow的訊號波形,會自動跳出dataflowwindow,其中顯示該訊號的連接情況;以這種方法帶出dataflowwindow會在下方同時顯示waveviewer,不需要的話可以從ViewShow Wave取消。

∙從ModelSim主視窗中的ViewDataflow開啟視窗,從signalswindow將要看的訊號"拖曳"到Dataflowwindow

5-1 假設我們要看的是orig_del_bit_s1訊號,此時Dataflowwindow顯示如下:

5-2 如果想進一步察看此訊號的Receiver,選定其輸出連線(redhighlight),按 (expandnettoallreaders,ie.dow-streamcircuit)就會顯示如下結果:

(直接以滑鼠左鍵雙擊redhighlightedline也有同樣效果)

同理,可以使用 查看訊號的Drivers(ie.up-streamcircuit)、使用 查看訊號的DriversandReceivers。

(EraseAll):

清除dataflowwindow

5-3 從dataflow視窗的ViewShow Wave,打開embeddedwaveviewer

選定dataflow視窗內的元件#ASSIGN#104,此時會看到wave視窗內列出該元