数字频率计课程设计实习报告Word文档下载推荐.docx

《数字频率计课程设计实习报告Word文档下载推荐.docx》由会员分享,可在线阅读,更多相关《数字频率计课程设计实习报告Word文档下载推荐.docx(18页珍藏版)》请在冰豆网上搜索。

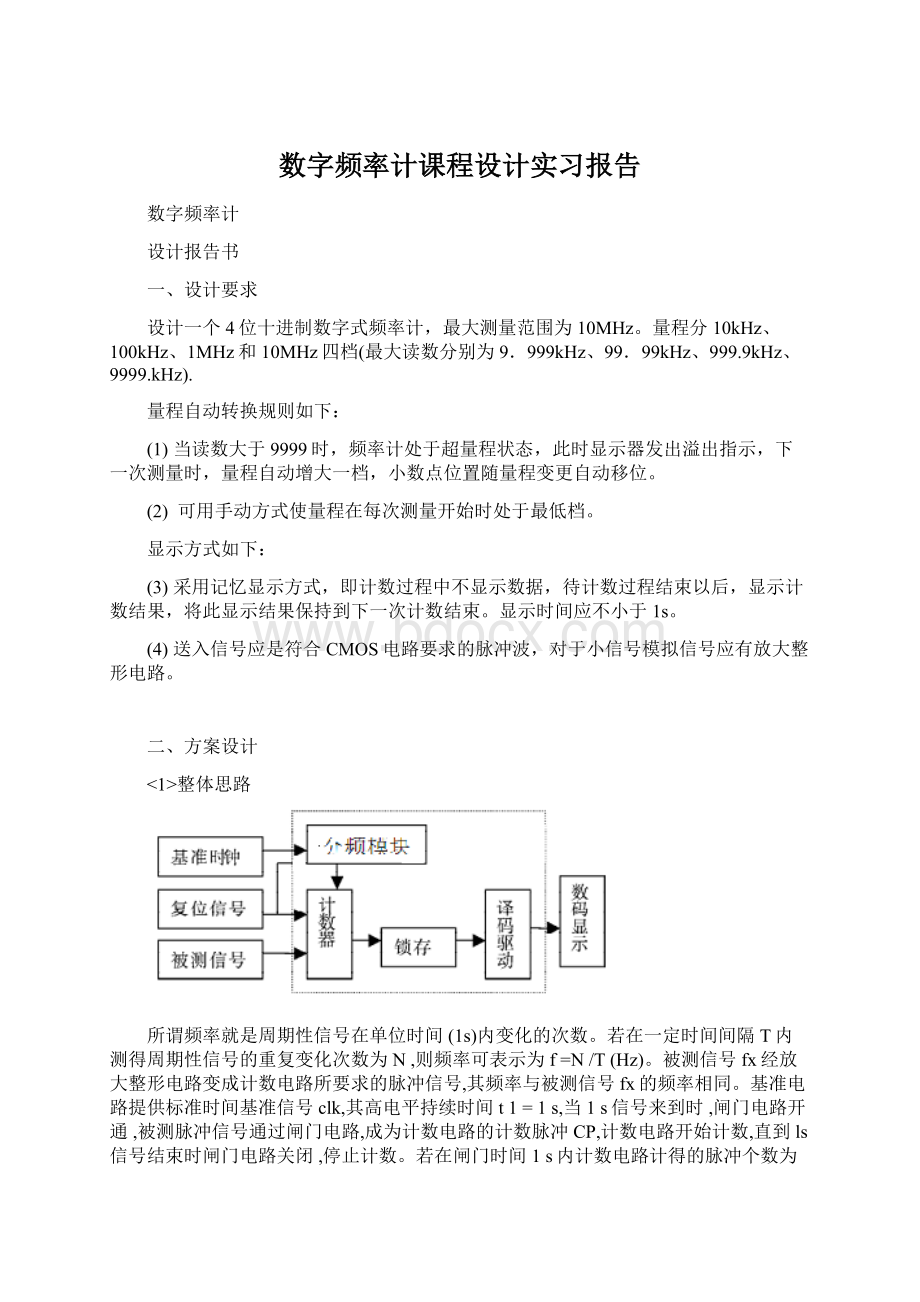

3>

整形电路的选择

整形电路中可以用运算放大器LM311组成电压选择器实现,以下是关于此芯片的资料:

引脚功能:

GROUND/GND接地

INPUT+

正向输入端

INPUT-

反向输入端

OUTPUT

输出端

BALANCE

平衡

BALANCE/STROBE平衡/选通

V+

电源正

V-

电源负

NC

空脚

LM311引脚图

由于LM311过于复杂且此次设计要求精度不高,整形电路可以改为如下电路:

这样产生稳定3.3V为幅值的信号送入EPM570中,对芯片起到保护作用。

设计所用核心芯片资料及其原理

所用核心芯片为CPLD器件EPM570T100C5。

基本设计方法是借助集成开发软件平台quartusII6.0,用原理图、硬件描述语言(VerilogHDL)等方法,生成相应的目标文件,通过下载电缆(“在系统”编程)将代码传送到目标芯片中,实现设计的数字系统。

EPM570引脚图:

在QuartusII6.0中设定的引脚分布如下:

4>

计数译码原理图:

5>

分频选择器原理图:

6>

数码管引脚图:

通过VerilogHDL语言设计程序,实现上述原理图功能,最终所测信号频率以四位共阴极数码管显示,单位为KHz。

三、调试

1、按照分频计、计数器、锁存器、选择器、译码器模块分别进行编程调试、仿真;

2、建立工程,把五个模块连接,调试。

针对错误模块进行修改,重新建立工程、连接模块;

3、将程序下载到EMP570中,利用数电实验板以及数码管进行调试;

4、将各种器件焊接到万用板上,连接电源进行实际调试。

程序代码

1.modulessss(b,base);

inputb;

outputregbase;

reg[23:

0]q;

always@(posedgeb)

if(q<

5999999)

q<

=q+1;

else

begin

base<

=!

base;

q<

=0;

end

Endmodule

2

moduleFen6M(b,base);

q<

base<

3.

modulectrl(clk,Counter_EN,Latch_EN,Counter_Clr);

inputclk;

outputCounter_EN,Latch_EN,Counter_Clr;

regwire_1=0,wire_2=0;

always@(posedgeclk)

wire_1<

=!

wire_1;

always@(negedgeclk)

wire_2<

=wire_1;

assignCounter_EN=wire_1;

assignLatch_EN=(!

Counter_EN)&

wire_2;

assignCounter_Clr=(!

(!

Latch_EN)&

wire_2);

endmodule

4.

modulecounter(clk,clr,en,q,ql);

inputclk,en,clr;

outputreg[3:

0]q;

outputql;

assignql=en&

(q==9);

always@(posedgeclk,posedgeclr)

if(clr)q<

if(en)

if(q<

9)q<

elseq<

5.

modulelatcher(d1,d2,en,clk,q1,q2);

input[3:

0]d1,d2;

inputclk,en;

outputreg[3:

0]q1,q2;

always@(posedgeclk)

if(~en)

q1<

=d1;

q2<

=d2;

6.

moduleover_select(IN,SELECT,OUT);

0]IN;

inputSELECT;

0]OUT;

always@(SELECT)

case(SELECT)

0:

OUT<

=IN;

1:

=10;

endcase

7.

moduledecode4to7(incode,outcode);

0]incode;

output[6:

0]outcode;

reg[6:

always@(incode)

case(incode)

4'

b0000:

outcode=7'

b1111110;

b0001:

b0110000;

b0010:

b1101101;

b0011:

b1111001;

b0100:

b0110011;

b0101:

b1011011;

b0110:

b1011111;

b0111:

b1110000;

b1000:

b1111111;

b1001:

b1110011;

default:

b1000111;

endcase

8.

moduleHalf_freq(CLK_in,CLK_out);

inputCLK_in;

outputCLK_out;

regCLK_out;

always@(posedgeCLK_in)

CLK_out=~CLK_out;

9.

modulefenpin(clk,fout10,fout100,fout1000);

outputfout10,fout100,fout1000;

reg[3:

0]q1,q2,q3;

assignfout10=(q1==9);

assignfout100=fout10&

(q2==9);

assignfout1000=fout100&

(q3==9);

if(q1<

9)q1<

=q1+1;

elseq1<

always@(negedgefout10)

if(q2<

9)q2<

=q2+1;

elseq2<

always@(negedgefout100)

if(q3<

9)q3<

=q3+1;

elseq3<

10.

moduledecode2to4(incode,outcode);

input[1:

integeri;

always@(incode)

case(incode)

2'

b00:

outcode=4'

b1000;

b01:

b0100;

b10:

b0010;

b11:

b0001;

11.

moduledecode4to7(incode,outcode,in);

inputin;

output[7:

reg[7:

case(incode)

outcode[6:

0]=7'

endcase

if(in==1)outcode[7]=1'

b1;

elseoutcode[7]=1'

b0;

12.

modulemux4_1(a,b,c,d,s,out);

inputa,b,c,d;

input[1:

0]s;

outputregout;

always@(s)

case(s)

2'

out=a;

out=b;

out=c;

out=d;

13.

modulerenge_counter(clk,clr,q,ql);

inputclk,clr;

outputreg[2:

outputql;

assignql=(q==4);

always@(posedgeclk,posedgeclr)

if(clr)

elseif(q<

4)

elseq<

总体电路图

四、测试数据与实验结果

组号

准确数据

实验数据

1

3

4

5

6

7

五、心得体会

我们小组的实习题目是数字式频率计。

该项目主要是通过verilog语言编程后进行焊接完成。

我们在十七十八号两天对verilogHDL语言设计进行了学习与巩固,从十九号正式开始数字式频率计的设计,二十一号编程验收通过,开始处理外部信号的测试,即稳压工作。

之后进行PCB图的制作。

从二十四号开始焊接电路板,于二十七号完成所有工作。

在刚开始编程的时候,对于verilogHDL语言这种新知识要花一段时间来消化,所以在编写频率计的代码时遇到很多问题,但是经过我们查找资料和激烈的讨论后终于解决了问题。

通过自我学习以及其他方式我们了解到了计数器分频器译码器等模块的编译方式,学到了很多Verilog的有用的知识点。

从二十四号开始的焊接由于之前电子工艺实习时焊接过几百个点,所以最后的焊接工作还比较顺利。

同时经过这几天的焊接,在某种程度上又锻炼了我们的动手能力。

通过这十几天的学习与实践,我们完成了数字频率计的设计以及制作,我们才发现自己只学书本上的知识是远远不够的,还是要靠动手来提高自己的能力。

这次实习一方面提高了自己的学习与思考的能力,另一方面在动手能力方面也有了较大的提高,所以这次的电子工艺实习对我们来说是收获颇多的。

当然,我们在这一方面还有许多的不足之处,我们会在今后的学习生涯中继续努力争取继续提高。