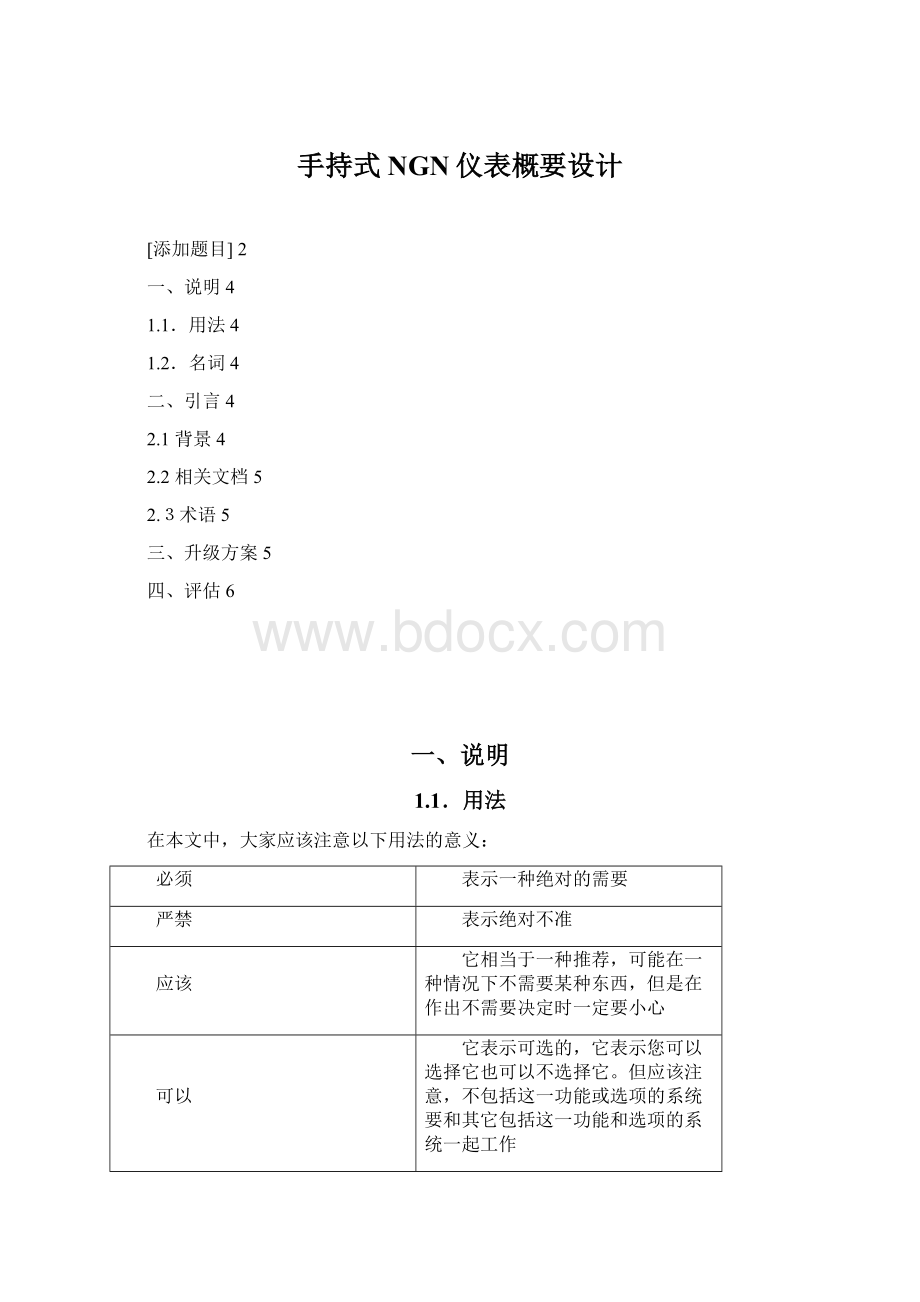

手持式NGN仪表概要设计Word下载.docx

《手持式NGN仪表概要设计Word下载.docx》由会员分享,可在线阅读,更多相关《手持式NGN仪表概要设计Word下载.docx(18页珍藏版)》请在冰豆网上搜索。

《手持式NGN仪表总体设计方案》

2.3术语

三、项目需求

3.1手持式NGN仪表主要功能

1.适合城域传送网中的以太网业务,包括专线网和数据承载网业务。

同时可快速、高效地进行各种电路的第一层(物理层)和第二层(数据链路层)比特误码率(BER)测试;

2.特别适合于电信/IT运营商的传输运维部或基础网络部使用,进行网络/业务日常维护、故障诊断和业务开通测试。

3.2主要计划达到的性能指标

1.满足RFC2544基准测试要求网络互联设备例如路由器性能测试。

应当包括下列指标:

Ø

吞吐量

时延

丢包率

背靠背帧数

系统恢复时间

2.支持802.3标准10/100/1000BASE-T铜缆和1000BASE-SX/LX/ZX千兆以太网SFP光接口

3.具有双端口流量发送能力,同时能够全线速流量发送10/100/1000Mbps以太网(Ethernet)业务流量;

4.实现在城域传送网中各种网络/业务日常维护与测试及以太网业务开通所必需的测试功能-即各种网络电路的第一层(物理层)和第二层(数据链路层)的比特误码率(BER)测试;

5.VLAN协议验证和流量优先次序测试;

6.IPPING发生和对网络连通性验证的响应;

7.用户可编辑加载各种类型流量,包括constant/bursty/ramp帧、带宽利用率、帧速率、帧长及VLAN标识帧等,以测量、验证以太网链路的真实性能;

8.IP和MAC环回,测量第二层(MAC)或第三层(IP)精确的双向时延;

9.自动测试电子邮件、网络、文件、DNS、DHCP、IPXl、FTP、交换机和路由器的性能指标。

四、项目总体方案

4.1总体方案

由项目需求可以看到,本项目主要完成通信网络L1~L3三层网络的性能测试,测试需求的1~5条主要是完成物理层和数据链路层的测试,6~9条主要完成网络层的测试完成物理层和数据链路层的测试只需要对以太网帧进行测试即可完成,而网络层性能测试需要对IP包进行解析。

据此,我们给出项目总体设计方案如图1所示。

整个系统由硬件部分和软件部分两部分组成,硬件部分主要完成以太网帧的解包和组装、IP包的解包和组装、MAC地址和IP地址过滤等功能,软件部分主要完成系统控制、数据分析统计、图形显示、流量仿真、TCP/IP协议支持、异常处理等功能。

图1项目总体功能模块图

硬件部分中主要包括线路接口及物理层模块、MAC层模块、FPGA模块、微处理器模块、外围电路模块、电源模块等。

各模块结构和功能分别为:

线路处理模块:

本项目采用基于5类线或六类线的RJ45接口提供支持802.3标准的10/100/1000BASE-T铜缆接口,采用可以热插拔的SFP光模块提供支持802.3标准的1000BASE-SX/LX/ZX千兆以太网光接口;

物理层模块:

就是一个支持802.3标准的10/100/1000BASE-T铜缆接口的PHY芯片,本项目设计中采用美国国家半导体公司的低功耗的DP83865芯片;

MAC层模块:

采用PMC公司的PM3387芯片。

该芯片内部集成了千兆以太网的光接口的PHY层处理功能,因此光收发模块可以直接和PM3387芯片连接,而RJ45接口则需要通过物理层模块处理PHY层协议,再与PM3387芯片相连。

本模块基本上可以完成对以太网帧的处理,对RFC2544中提到的几种测试指标均可以通过ARM微处理器对PM3387芯片内部寄存器的访问和配置得到需要的结果。

FPGA模块:

本模块主要完成对IP包的处理。

本模块对IP包地址进行解析,通过与我们设置的IP地址过滤条件对IP包进行筛选,符合要求的IP包送到FIFO中等待上层软件调用和处理;

双端口FIFO:

FPGA与ARM之间数据传送的buffer,可以从FPGA和ARM两边的接口进行访问,根据我们需要处理的数据量大小决定是采用集成在FPGA中的FIFO还是使用外置的存储芯片作为FIFO;

ARM处理器:

整个系统中的核心控制模块,整个软件运行的基础

外围电路:

包括USB接口、CF卡接口、LCD及触摸屏、数据输入输出接口、存储单元、语音接口、通信接口、JTAG接口等电路模块和接口

电源模块:

提供整个设备的电源供应,包括电池供电和外接电源供电两种方式。

由于是手持式设备,电源模块的设计十分重要,采用电池供电时,整个设备应该能待机5个小时、正常工作2个小时以上。

软件部分主要包括实时嵌入式操作系统、图形界面、初始化程序、应用程序等部分,下面分别介绍:

实时嵌入式操作系统:

可以选用嵌入式Linux和WindowsCE等实时操作系统,根据本项目开发需要,我们选用windowsCE.net5.0;

初始化程序:

启动时完成对硬件部分各模块的初始化工作,包括寄存器配置、模块驱动、程序下载等工作;

图形界面:

显示给用户看到的信息,包括操作系统界面、应用程序界面等。

4.2硬件部分设计方案

硬件部分主要包括线路接口及物理层模块、MAC层模块、FPGA模块、微处理器模块、外围电路模块、电源模块等。

主要完成对以太网帧的识别、解析和过滤,对IP包的解析和过滤、流量生成,图形显示、通信、供电等功能。

下面主要介绍几个重要模块的设计:

4.2.1MAC层模块

MAC层模块使用PMC公司的PM3387作为双通道千兆以太网控制器,MAC层的强大的统计功能实现MAC层的管理.MAC层的统计在发送方向上和接收方向上为:

收发的正确帧数、收发的BYTE数、因内部收发错误丢失的帧、收发的单播帧、收发正确的单播帧、收发的多播帧、收发正确的多播帧、收发的广播帧、收发正确的广播帧、收发的PAUSE帧、和收发按帧长度范围的统计、线路利用率。

微处理器读取相应的统计寄存器得到统计计数值,就可以了解当前的网络状况,并且可以随时清零重新计数。

MAC层的流控实现了自动产生PAUSE帧、手动设置产生PAUSE帧和自动协商的使能、不使能设置.手动设置产生PAUSE帧可以设置源MAC地址、PAUSE计数器以及产生PAUSE帧的频率。

千兆以太网接口板提供了双通道的千兆以太网接口.提供双通道的标准的IEEE802.3GigabitEthernetMAC,提供POSPHYLEVEL3的接口,支持ETHERNET2.0,IEEE820.3LLC和IEEE802.3SNAP/LLC编码格式,支持VLAN。

图2千兆以太网MAC芯片数据处理流程图

千兆以太网MAC芯片数据处理流程如图2所示,POSPHYLEVEL3接口给FPGA模块提供输入接口。

千兆以太网MAC控制器支持标准长度为1518BYTE的以太网帧,还支持带VLAN标志的长度为1522BYTE的以太网帧。

编码解码器是8B/10B编码解码。

串并转换和并串转换接收10BIT宽的并行码流,串行化成高速的串行码流,流控/自动协商和统计单元模块分别实现流控、自动协商和统计计数。

千兆以太网接口板提供两个通道的完全独立的控制和统计,例如:

流控、自动协商、环回、以及各种统计。

PAUSE流控按照IEEE802.3x实现,当检测到缓冲区中的拥塞时,例如超过了预定的缓冲区阈值,将构造一个PAUSE帧并把它插入到端口的的发送FIFO。

4.2.2FPGA模块

FPGA模块主要完成对IP包的过滤功能,针对千兆以太网高速输入的数据流和嵌入式处理器及操作系统之间的处理能力的矛盾,采用FPGA对MAC层经过POSPHY接口输入的以太网帧进行过滤,对满足条件的协议或IP地址进行过滤,符合条件的送给FIFO,不符合条件的数据丢弃。

该处理过程如图3所示

发送数据时,特别作RFC2544的吞吐量测试时,需产生千兆线速的流量,而ARM嵌入式处理器不能达到这个要求,需要由FPGA产生。

整个FPGA的数据处理流程由图4所示。

图3FPGA数据处理流程图

图4FPGA数据处理流程图

4.2.3ARM微处理器

ARM处理器是整个硬件处理的核心单元,完成对各个硬件单元模块的、初始化、控制及管理功能。

由于项目涉及的数据速率较高,对处理器的处理能力也有很高的要求,主要体现在以下几个方面:

能处理大量的高速的数据;

有较高的实时性;

很强的图形显示支持能力;

低功耗、支持电源管理;

主流芯片、价格合理。

根据上面的条件和项目具体需求,我们可以选择ARM9及以上的ARM微处理器。

经过初步调研,SamsungS3C2440和IntelXscalePXA270可以满足项目的需要。

下面对这两款芯片作个对比:

基本参数

SamsungS3C2440

16/32bitARM920T内核,标称工作频率:

400MHz,运算能力:

450MIPS(最高工作频率:

533MHz)

系统时钟:

内部PLL产生400~533MHzCPU内核工作频率,外部总线频率:

100~133MHz

LCD控制器:

CPU内置STN/CSTN/TFTLCD控制器,支持1024*768分辨率以下的各种液晶

触摸屏控制器:

CPU内置4线制电阻式触摸屏控制器

USB1.1主机控制器:

2通道;

SD/MMC卡控制器:

CPU内置

IIS数字音频输入/输出接口:

CPU内置IIS控制器

电源:

高效率DC/DC开关电源

支持的操作系统:

WINCE/Linux/uCOS-II

IntelXscalePXA270

标称工作频率:

520MHz,最高工作频率:

624MHz

内部PLL产生104~624MHzCPU内核工作频率,外部总线频率上至104MHz

SM501:

硬件2D图形加速器(扩展)

12V外部直流电源

USB接口:

2个USBHOST,一个USBDEVICE

SD/MMC控制器:

音频控制器:

通过AC97外扩(耳机接口、麦克风接口)

外扩

LCD接口:

一个CPU内置LVTTL接口、2个SM501外扩(一个LVTTL接口和一个LVDS接口)

WINCE/Linux

开发板参数分析

S3C2440采用ARM920T内核,是ARM9系列中高性能的嵌入式CPU,它是目前嵌入式市场中利用比较频繁的ARM9微处理器,由于它的价格比较低廉(各个公司的报价有所不同),且支持的操作系统比较广泛,在许多工控产品以及手持式设备中有较好的市场。

S3C2440开发板提供的接口比较丰富,包括调试所用的串口、JTAG口,以及USBHost,网口都是比较全面的,此外从产品的需求来讲,我们所需要的音频接口,外置存储卡的支持,LED,以及触摸屏和LCD,2440都能支持。

且在显示方面可以支持到我们所需要的640×

480分辨率。

目前根据各地厂商的报价,基本上在2500元左右(包括320×

2403.5英寸TFTLCD以及触摸屏),如果配置调试工具和6寸以上的TFTLCD,价格会有所增加。

PXA270开发板是Intel公司针对日益增长的多媒体应用而设计的嵌入式开发板,开发板采用的是ARMV5TE内核,该开发板主要用于多媒体要求比较高的场合,因为其支持的视频音频性能出色,并且附带摄像头设备,所以价格颇高。

但是由于CPU的性能良好,而且功耗较低,支持常用的操作系统,在PDA市场里有一定的市场份额。

支持的接口丰富,除了满足项目所需要的各种接口之外,在音频和视频方面都有良好的表现,但是考虑到我们的产品对多媒体方面的要求比较低,所以这方面是有些资源浪费。

IntelPXA270电源功耗管理性能出色,当其工作在标准频率时,功耗大约为400mw,而在空闲时,可以达到100mw。

最大性能地节省了电能。

PXA270开发板相对比较贵,从英蓓特公司获得的报价获知,一套PXA270开发板大概需要14000元(包括LCD和触摸屏)。

也有比较便宜的开发板,部分小型开发板供应商给出的报价为5200元(不含仿真器和LCD)。

选择和分析

我们研发的是一个基于千兆网络的测试仪表,从功能的角度来说,两款CPU前者可以达到400MHz,后者可以达到520MHz。

而且两款都提供了对电路扩展以及外置存储、高性能显示的支持。

从手持式设备的要求来讲,我们希望节省更多的电能来获得更长的工作时间,PXA270要比2440更加出色,因为在CPU设计中,其芯片采用了电源管理单元,更大程度地合理分配电能损耗。

从接口方面来讲,两款开发板都支持嵌入式开发所需要的各个单元和接口,两款开发板都对嵌入式操作系统提供了良好的支持,目前两款开发板都提供了对Linux和WindowsCE.net4.2的支持,提供了操作系统的BSP以及开发文档,对操作系统的移植和裁减有很大的帮助,可以缩短开发时间。

从成本的角度来讲,2440比PXA270要便宜很多,一方面后者的CPU的性能要比前者强,另一方面由于后者对多媒体性能的支持很强,所以有一定的价格差异。

而且2440是一块市场上使用量很大的芯片,相关的开发做得很多,芯片价格也要便宜很多。

从目前的市场上提供的开发板资源看,由于2440开发板没有提供对WindowsCE5.0BSP的支持,如果要是选择了这款开发板,需要对WindowsCE4.2BSP进行修改,按照有经验的开发人员来说,编写和调试一个成熟的BSP需要几个月的时间,如果BSP不成熟将对系统稳定有很大的威胁。

如果采用WindowsCE4.2,由于该操作系统对某些组件的支持不够完善,譬如USB接口,SNMP协议等等,这些需要自己去编写硬件驱动以及上层软件。

而PXA270针对这点没有这个问题,英蓓特公司将在本月末提供WindowsCE5.0的BSP,如果不考虑成本的原因,这款比较合适。

根据以前的经验来说,操作系统移植和裁减这部分是比较简单的,但是,如果提供了BSP的支持,可以在一个月之内把系统移植完毕。

最新的消息是目前已经有开发板生产商提供对2440芯片的WindowsCE.net5.0的BSP包的支持。

根据上面的分析,我们方案建议购买S3C2440开发板,直接利用WindowsCE5.0的BSP进行开发。

4.3软件部分设计方案

4.3.1RFC2544基准测试实现

Throughput测试:

测试描述

以特定速率向DUT(待测设备)发送指定数量的帧。

降低发送速率,直到DUT发送出来的帧等于此DUT接收到的帧。

(因此测试仪必须记录发送和接收到的帧数)。

测试结果:

结果以图表的形式展示。

图表定义:

1.x----帧长,y----帧速率;

2.至少包括两条曲线:

一条为特定介质里的理论计算曲线;

一条为实际测得曲线;

(附:

可以根据数据流的不同形式增加其他曲线)

3.图表的文本说明应包括:

协议(),数据流格式()和介质类型。

性能描述中应包括:

1.测得的最大帧速率(即throughput);

2.测试使用的帧长;

3.采用该帧长情况下,理论计算介质的最大帧速率;

4.协议类型。

latency测试:

测试描述:

基于throughput测试,且此throughput测试应基于各种帧长。

向DUT发送由特定长度的帧组成的帧流(持续时间至少120秒);

在60秒后的一帧中增加一个识别标志(用以识别该特定帧的发送和到达,标志形式待定);

时间戳分别位于该帧的发送和到达时间点,在此分别记为timestampA和timestampB。

latency的计算方法:

B-A。

20次测试平均值。

测试结果应以表格形式呈现,其中row为不同帧长,column为测试时采用的不同帧速率。

测试实现细节考虑:

1.timestamp的实现方式----可参考stm-1卡;

2.测试方式:

外接DUT的外环回测试。

3.framelossrate测试:

以特定帧速率和帧长向DUT发送一定数量(记为input_count)的帧,测试由该DUT转发的帧数量(记为output_count)。

计算方法((input_count-output_count)*100)/input_count;

测试要点:

每次测试,帧速率减小步进值小于等于throughput(最大帧速率)的10%;

测试结束条件:

连续两次测试(即两次减小帧速率过后),帧丢失率等于0;

测试结果以图表形式呈现,其中:

x----帧速率(以相对于最大帧速率throughput的百分数表示),y----帧丢失率;

可以用不同的曲线表示不同帧长、不同协议及不同数据格式情况下的测试结果。

back-to-backframes测试:

以最小inter-framegaps向DUT发送一突发帧组,测试该DUT转发的帧数量。

最终测试的背靠背帧数为无帧丢失情况下的测试帧数。

最小inter-framegaps;

增大和减小burstofframe的条件:

如果测得的帧数量小于发送帧数量,减小突发帧组长度(即包含的帧数);

如果测得的帧数量大于发送帧数量,增大突发帧组长度;

测试时间大于等于2sec;

50次平均值。

测试结果以表格形式呈现,其中:

row----帧长,column----数据流类型。

实现形式类似throughput测试并基于framelossrate测试;

最小inter-framegaps值来源();

数据流类型定义;

确定测试使用的突发帧组、帧长和测试时间三者的关系。

systemrecovery测试:

以throughputrate与“介质允许的最大速率”(maximumrateforthemedia)的较小者的110%向DUT发送帧流,持续时间至少60秒。

测试中涉及两个时间戳,在此记为timestampA和timestampB。

时间戳定位:

timestampA:

在此时刻将以上描述的初始发送帧速率减半;

timestampB:

最后一个丢失帧时刻。

systemrecovery计算方法:

B-A。

测试多次,取平均值。

110%ofthroughputrate与“介质允许的最大速率”(maximumrateforthemedia)中的较小者;

timestampA和timestampB。

表格形式呈现,其中:

row----帧长,column----测试使用数据流类型。

测试方式类似于throughput;

可调发送帧速率;

最后一个丢失帧时刻的确定。

4.3.2VLAN协议测试部分

1.协议介绍

VLAN为虚拟局域网,逻辑上把网络资源和网络用户按照一定的原则进行划分,把一个物理上实际的网络划分成多个小的逻辑的网络。

这些小的逻辑的网络形成各自的广播域,也就是虚拟局域网VLAN。

IEEE802.1Q规定了VLAN的帧格式,图5是VLAN与IEEE802.3(以太网帧格式)的比较,可以看到VLAN帧比以太网帧多出了4个字节。

图5VLAN与IEEE802.3帧结构比较

先看TCI部分,分为VLANID、CFI和priority三部分。

ID共有12位,标明VLAN域,共可以配置4096个VLAN,而CFI是用于总线型的以太网与FDDI、令牌环网交换数据是使用的帧格式。

有三位优先级位,可以表示八种状态,用于当网络阻塞时,优先发送哪个数据包。

我们所做的就是配置12位的ID以及3位的priority,看似象实现交换机的功能。

(因此需要硬件支持,能给以太网帧添加VLAN标签)

2.测试部分

协议验证和流量优先次序测试

这部分主要做协议验证,我们可以通过检验以太网帧格式就可以判断,此外流量优先次序关系到优先级的标志位,可以根据3位状态码来区分。

4.3.3IP层测试

1.测试内容:

DHCPDNSPINGIP路由跟踪(ROUTETRACERT)以及SNMP查询、自动测试电子邮件、网络、文件、DNS、DHCP、WNS、Novell、打印、FTP、一级DC、二级DC服务器、交换机和路由器的性能指标。

2.实现方式:

WindowsCE.net支持IP层的各种协议,包括IPv4、IPv6等等协议,而其他的协议功能,操作系统可以简单实现,但是检测电子邮件、网络、文件以及设备性能指标需要进行编程。

4.3.4操作系统移植

本项目采用嵌入式操作系统windowsCE.net,根据前面的分析,我们采用WindowsCE.NET5.0版本。

具体开发工具为平台定制工具PlatformBuilder,以及应用程序开发工具EmbeddedvisualC++。

操作系统的开发分为以下几个部分:

1.平台组件选择以及定制,包括编写BSP以及驱动开发

2.根据需要对内核进行裁减,选择合适的内核进行调试下载

3.生成SDK,导入EVC,进行上层应用程序设计

具体的步骤如下图所示:

图6操作系统移植步骤

4.3.5图形界面设计

图形界面主要对项目测试内容进行分类显示,设计重点是良好的人机界面、友好的操作按键功能设置、完整的测试信息的显示,界面不必要求很花哨华丽,但是功能一定要齐备。

显示界面中的模块分类和实际测试中的功能分类模块相互独立又相互联系。

根据这个原则,我们项目的图形界面设计基本考虑如图7所示。

图7图形界面模块结构

模块说明:

1.测试仪本身网络状态的显示和配置

用户可以选择通过手动或者DHCP实现测试仪自身的网络配置。

显示和配置可以整合为一个功能单位,即配置网络属性,可参考windows系统下的传统网络配置界面,如图8所示。

如果需要单独显示测试仪网络配置属性,则显示出来的信息应当包括以上配置中所含属性。

另外,还可考虑在“操作系统网络监测工具调用”中兼容ipconfig选项功能。

图8网络属性配置参考

2.网络发现、设备发现

可以考虑将网络发现和设备发现功能分开(例如特别的测试