基于CPLD控制的水电机组在线监测系统数据采集卡设计.docx

《基于CPLD控制的水电机组在线监测系统数据采集卡设计.docx》由会员分享,可在线阅读,更多相关《基于CPLD控制的水电机组在线监测系统数据采集卡设计.docx(7页珍藏版)》请在冰豆网上搜索。

基于CPLD控制的水电机组在线监测系统数据采集卡设计

基于CPLD控制的水电机组在线监测系统数据采集卡设计

张伟,韩亮,陈斌,张俊华

(清华大学机械工程系清华大学先进成型制造重点实验室)

摘要:

本文介绍了一款可实现无限长时段采样的A/D板,该板基于复杂可编程逻辑器件(CPLD)控制的水电机组在线监测系统采集卡设计。

采集卡具有多通道、板载CPLD器件EPM7256AEQC208-10和基于ISA总线控制技术的特点。

采集卡使用交替存储的控制技术,能够实现对信号的连续采集和存储,以确保发电机组运行过程瞬态特征数据不丢失。

关键词:

CPLDISA在线监测连续采集SRAM

1引言

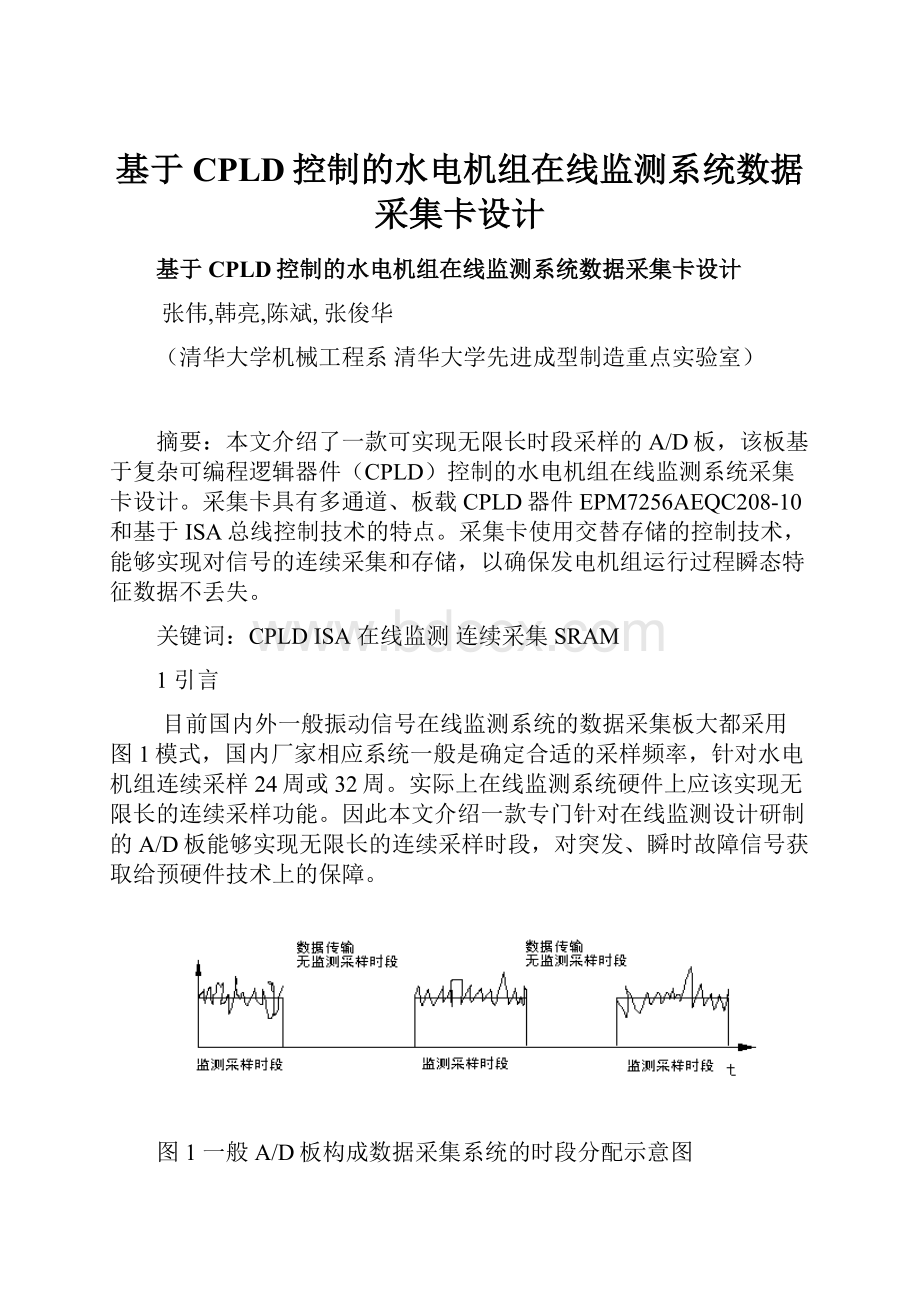

目前国内外一般振动信号在线监测系统的数据采集板大都采用图1模式,国内厂家相应系统一般是确定合适的采样频率,针对水电机组连续采样24周或32周。

实际上在线监测系统硬件上应该实现无限长的连续采样功能。

因此本文介绍一款专门针对在线监测设计研制的A/D板能够实现无限长的连续采样时段,对突发、瞬时故障信号获取给预硬件技术上的保障。

图1一般A/D板构成数据采集系统的时段分配示意图

图2在线监测系统专用A/D板无限长数据采集时段示意图

由于水电机组设备庞大,结构复杂,诱发故障原因多,且故障停机造成的间接损失大,因此,为实现机组安全可靠运行,对发电机组的振动、摆度、温度、压力等重要的工况参数进行实时监测十分必要。

发电机组在运行过程中随时存在大量的瞬态特征数据,这些数据对机组故障原因的分析具有重要意义,因此为了保证状态参量信号中包含的大量重要信息不被丢失,数据采集系统应该具备连续采样和存储的功能。

一般发电机组(包括汽轮机和水轮机)的重要特征频率一般都在1kHz以下[1],本文介绍的数据采集卡单通道最大采样频率为50kHz,能够满足机组监测的一般需求。

并且针对不同机组转速不同,特征频率范围不同的特点,采集卡的采样频率分为8个档,可以通过驱动程序由上位机软件灵活设置。

板卡具有8个信号采集通道,通过ALTERA公司CPLD器件EPM7256AEQC208-10控制AD采集、通道选取、数据存储、数据读取、中断控制和读写端口等功能,并且完成采集卡ISA总线与上位PC机进行通讯的功能。

板卡采用双SRAM交替存储数据,实现了对信号的连续采集和存储的功能。

2采集卡原理

采集卡的原理如图1所示,其设计思想是:

采用两块12bit,最大采样频率200K的A/D芯片,每块A/D芯片负责采集4个通道的信号,通过4选1模拟开关交替选取不同通道轮流采集。

采集的数据交替的存储至两片SRAM中,采集完成后发出中断信号,通知计算机总线,由计算机ISA总线选择读取不同SRAM中存储的AD转换后的数字信号。

整个过程由CPLD器件控制协调完成。

2.1A/D转化

A/D转化器是美国ANALOG公司的AD678[2]。

它是一种高性能的12bit,200kHz的AD转化器,具有75DB信噪比和0.5DB非线性误差,可以直接转换0V至10V,或-5V至+5V电压信号,可以满足发电机组监测系统的需求。

2.2SRAM交替存储机制

AD转换的结果一般采用FIFO、双口RAM和SRAM,FIFO、双口RAM的特点是接口方便,特别是双口RAM在实时连续采集系统应用广泛,但是其容量较小,大容量价格比较昂贵,因此,采集卡的数据存储采用价格相对低廉的SRAM。

SRAM只有一套地址线和数据线,对其存储和读取的过程是互斥的。

为了实现对信号连续采集和存储的功能,采集卡使用交替存储机制,即同一AD芯片使用两块SRAM存储数据,当第一块SRAM存满AD转换的数据后,立刻让AD向第二块SRAM存储数据,这一过程通过CPLD控制锁存器1_1和锁存器1_2完成,与此同时,让计算机总线通过CPLD控制接管第一块SRAM的地址总线和数据总线,如图1所示,通过计算机ISA总线系统读取该SRAM中的数据值并完成上位机显示和画图等功能,这样通过两块SRAM交替存储数据,保证信号在采集存储过程中的连续性和完整性,为事后利用各种方法分析存储的信号,以确定机组运行状态和故障类型提供前提保障。

图1基于CPLD控制的发电机组在线监测系统数据采集卡原理图

3CPLD控制逻辑设计

采集卡数字部分芯片数量多,并且需要控制的信号线、地址总线和数据总线较多,因此选取具有208管腿的CPLD器件EPM7256AEQC208-10控制协调采集卡整个工作过程。

该CPLD器件属于Altera公司7000系列,该系列是以第二代多阵列结构为基础,高性能的CMOS器件,其引脚到引脚的时延5ns,计数器工作频率178.6MHz,片内逻辑程序可以重复烧写,方便系统升级。

CPLD片内逻辑程序分为:

采样频率分档单元、寄存器逻辑控制单元、总线双向读写单元和SRAM交替存储控制单元四大部分组成,每一部分均采用VHDL语言和原理图结合设计的方法实现,最后将四大模块联结成整体程序固化到CPLD芯片内。

3.1采样频率分档

采样频率分档原理如图2所示,该模块通过控制寄存器5将外部晶振信号分频,寄存器5的数值不同对应分频后不同频率的信号,该分频信号接入两片AD芯片的SC模数转换启动引脚,用以控制AD芯片进行采样,同时接入SRAM地址总线计数器和模拟开关地址

图2采样频率分档单元原理图

计数器的时钟引脚,在AD转换的同时,由Qn_2控制模拟开关地址总线选择不同通道的模拟信号,并通过Qn_1控制SRAM的地址总线,将转换的结果存入SRAM中。

当SRAM所有单元写满后,由中断产生模块发出信号至ISA总线中断引脚,通知总线读取SRAM数据,并且发送清零信号至SRAM地址计数器,重新开始下一轮采样过程。

3.2寄存器逻辑控制单元表1CPLD各个寄存器功能表

寄存器

功能

Reg1

SRAM片选

Reg2

AD启动/停止采样控制

Reg3

端口读/写设置

Reg4

计数器控制

Reg5

采样频率设定

Reg6

SRAM交替存储标志

Reg7

SRAM选择读取标志

主要完成在CPLD内部配置各个寄存器的功能,本文研究的采集卡逻辑控制环节较多,因此,在CPLD内部设置了7个不同的寄存器,各个寄存器分别负责控制板卡上的不同芯片。

其对应功能如表1所示,Reg1负责片选所有SRAM;Reg2负责AD芯片启动/停止采样控制;Reg3负责端口读/写控制;Reg4是计数器控制清零/计数控制寄存器,同时控制SRAM地址总线计数器和模拟开关地址计数器;Reg5控制采样频率;Reg6和Reg7用于SRAM交替存储机制的控制,将在3.4节详细介绍。

3.3总线双向读写单元

为满足总线既能向板卡端口(即CPLD控制寄存器)写数据,又能够从端口和SRAM中读取数据的要求,采集卡ISA数据总线D0至D15直接连接至CPLD程序内部的双向总线端口上,通过ISA端口读写控制信号IOR和IOW,以及内存读写控制信号SMEMR设置CPLD内部双向总线的不同工作状态。

如图3所示,ISA总线的I/O读信号IOR、I/O写信号IOW和内存读信号MEMR信号线接入译码器电路输入端,由译码电路控制16位三态总线的双向总线ISA_SD[15..0],设置其状态为“高阻”或“输出”,当双向总线处于“高阻”状态时,ISA总线数据线可以将数据写入CPLD寄存器,当其处于“输出”状态时,ISA总线只能读取CPLD寄存器或SRAM中的数据。

采集卡设置寄存器Reg6为可读寄存器,Reg6和SRAM的数据总线均接入多路选择器,由译码器信号SEL控制多路选择器的输出值为Reg6的数值或者为SRAM的数值,输出信号直接通过16位三态总线送至ISA总线数据线。

实际系统需要安装多块采集卡,因此ISA总线在读取某块采集卡数据时,其他采集卡的ISA总线应该处于“高阻”状态,这样才能避免总线冲突,在CPLD内部通过寄存器Reg3设置BIDIR_CON信号实现这一功能。

计算机ISA总线在对某块板卡进行读取操作时,令Reg3=1,该板卡的双向总线为“输出”状态,同时令其余的板卡的Reg3=0,使其余板卡的双向总线为“高阻”状态,避免总线冲突。

图3双向总线读写控制框图

3.4SRAM交替存储控制

SRAM交替存储通过寄存器Reg6和Reg7控制实现,每块AD芯片对应两片SRAM,实现交替存储模数转换后的数据。

当Reg6=1时,两片AD分别向各自的第一块SRAM中存储转换数据,一旦第一片SRAM写满,令Reg6=2,AD立即开始向第二片SRAM存储转换后的数据。

计算机总线在读取SRAM数据之前,首先读入端口Reg6的数值,以判断已经完成数据存储的SRAM,如此交替循环存储,实现连续采样。

计算机ISA总线通过Reg7控制选择读取不同的SRAM的数据,如图4所示。

图4SRAM交替存储控制原理图

4结论

基于CPLD控制的发电机组在线监测系统数据采集卡采集通道多,满足发电机组结构复杂,工况测点数量多的要求;连续采样存储的特点保障重要瞬态特征数据不丢失。

利用可编程逻辑器件CPLD技术,简化了电路板的设计和开发,CPLD内部程序可重复烧写,方便电路板调试和升级。

ISA总线系统设计可扩展性强,只需增加相同的板卡,就可以构成功能强大的监测系统。

参考文献

[1]张正松.旋转机械振动监测及故障诊断[M].北京:

机械工业出版社,1991:

1–26.

[2]AD678Datasheet.AnalogDevices,Inc.2000:

1-12.

[3]AlteraMAX7000ProgrammableLogicFamilydatasheet.Altera,Inc.1999:

1–41.

[4]杨品,巴林风.接口技术[M].北京:

清华大学出版社,2001:

70–83.

[5]张伟,张正松.300MW抽水蓄能机组振动状态监测、分析、诊断系统的研究[J].

清华大学学报(自然科学版),1998,(4):

108-112.