XilinxISE利用入门文档格式.docx

《XilinxISE利用入门文档格式.docx》由会员分享,可在线阅读,更多相关《XilinxISE利用入门文档格式.docx(27页珍藏版)》请在冰豆网上搜索。

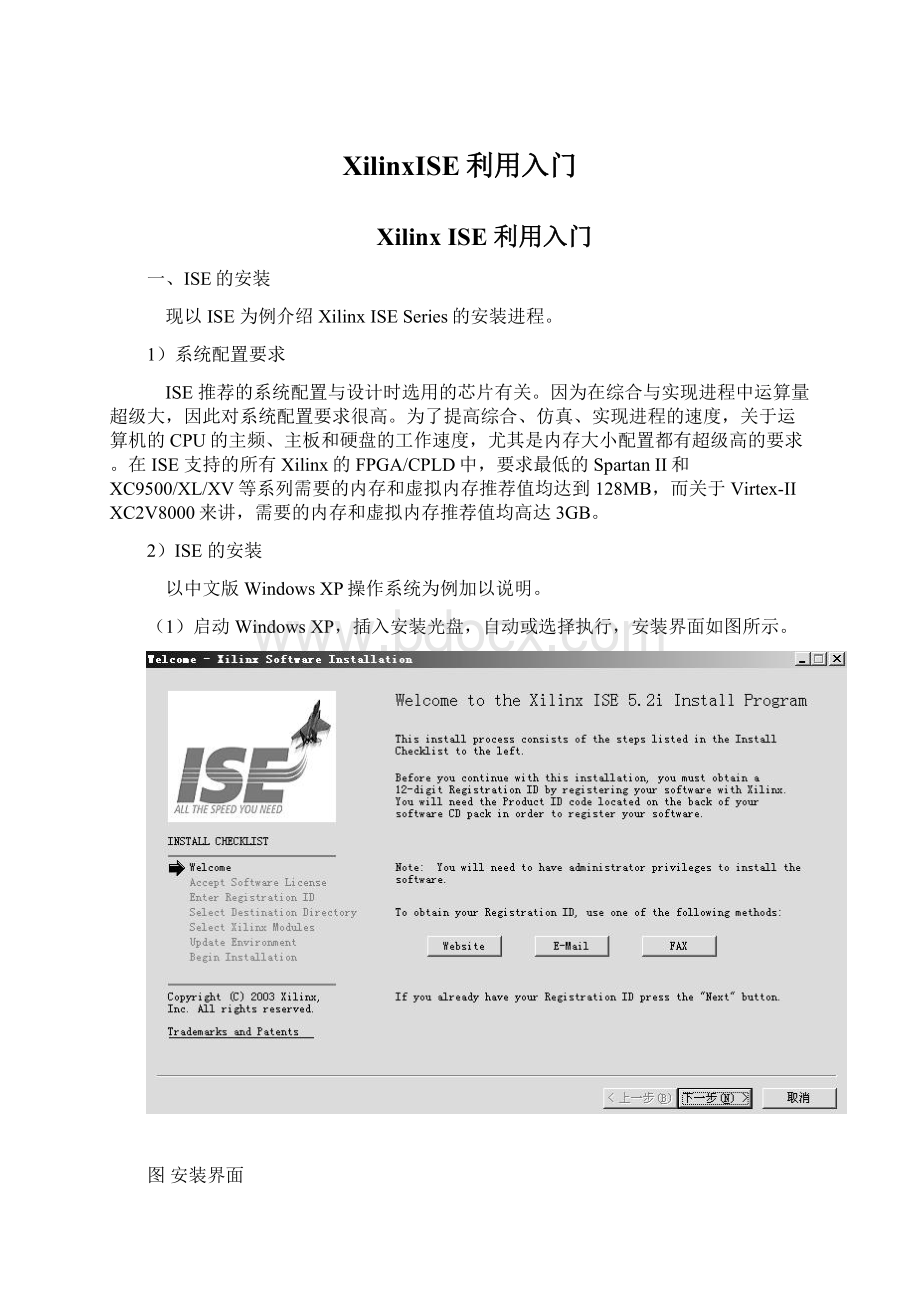

若操作系统是WindowsNT/2000/XP,选择开始->

控制面板->

系统->

选项->

高级->

环境变量,在环境变量中加入:

变量名:

Xilinx

变量值:

C:

Xilinx(即安装路径)

具体设置如图所示。

图环境变量设置操作图

3)安装第三方软件

在PC上安装完ISE以后,还需要安装第三方仿真软件,如ModelSim等。

2ISE工程设计流程

下面要紧概述ISE的大体开发流程和在开发进程中的各个时期需要用到的工具软件。

图说明了利用Xilinx公司的ISE开发设计软件的工程设计流程,具体分为五个步骤:

即输入(DesignEntry)、综合(Synthesis)、实现(Implementation)、验证(Verification)、下载(Download)。

图ISE的工程设计流程

1)图形或文本输入(DesignEntry)

图形或文本输入包括原理图、状态机、波形图、硬件描述语言(HDL),是工程设计的第一步,ISE集成的设计工具要紧包括HDL编辑器(HDLEditor)、状态机编辑器(StateCAD)、原理图编辑器(ECS)、IP核生成器(CoreGenerator)和测试鼓励生成器(HDLBencher)等。

常用的设计输入方法是硬件描述语言(HDL)和原理图设计输入方法。

原理图输入是一种常用的基本的输入方法,其是利用元件库的图形符号和连接线在ISE软件的图形编辑器中作出设计原理图,ISE中设置了具有各种电路元件的元件库,包括各种门电路、触发器、锁存器、计数器、各种中规模电路、各种功能较强的宏功能块等用户只要点击这些器件就能调入图形编辑器中。

这种方法的优点是直观、便于理解、元件库资源丰富。

但是在大型设计中,这种方法的可维护性差,不利于模块建设与重用。

更主要的缺点是:

当所选用芯片升级换代后,所有的原理图都要作相应的改动。

故在ISE软件中一般不利用此种方法。

为了克服原理图输入方法的缺点,目前在大型工程设计中,在ISE软件中常用的设计方法是HDL设计输入法,其中影响最为广泛的HDL语言是VHDL和VerilogHDL。

它们的共同优点是利于由顶向下设计,利于模块的划分与复用,可移植性好,通用性强,设计不因芯片的工艺和结构的变化而变化,更利于向ASIC的移植,故在ISE软件中推荐使用HDL设计输入法。

波形输入及状态机输入方法是两种最常用的辅助设计输入方法,使用波形输入法时,只要绘制出激励波形的输出波形,ISE软件就能自动地根据响应关系进行设计;

而使用状态机输入时,只需设计者画出状态转移图,ISE软件就能生成相应的HDL代码或者原理图,使用十分方便。

其中ISE工具包中的StateCAD就能完成状态机输入的功能。

但是需要指出的是,后两种设计方法只能在某些特殊情况下缓解设计者的工作量,并不适合所有的设计。

2)综合(Synthesis)

综合是将行为和功能层次表达的电子系统转化为低层次模块的组合。

一样来讲,综合是针对VHDL来讲的,即将VHDL描述的模型、算法、行为和功能描述转换为FPGA/CPLD大体结构相对应的网表文件,即组成对应的映射关系。

在XilinxISE中,综合工具主要有Synplicity公司的Synplify/SynplifyPro,Synopsys公司的FPGACompilerII/Express,ExemplarLogic公司的LeonardoSpectrum和XilinxISE中的XST等,它们是指将HDL语言、原理图等设计输入翻译成由与、或、非门,RAM,寄存器等基本逻辑单元组成的逻辑连接(网表),并根据目标与要求优化所形成的逻辑连接,输出edf和edn等文件,供CPLD/FPGA厂家的布局布线器进行实现。

3)实现(Implementation)

实现是依照所选的芯片的型号将综合输出的逻辑网表适配到具体器件上。

XilinxISE的实现进程分为:

翻译(Translate)、映射(Map)、布局布线(Place&

Route)等3个步骤。

ISE集成的实现工具主要有约束编辑器(ConstraintsEditor)、引脚与区域约束编辑器(PACE)、时序分析器(TimingAnalyzer)、FPGA底层编辑器(FGPAEditor)、芯片观察窗(ChipViewer)和布局规划器(Floorplanner)等。

4)验证(Verification)

验证(Verification)包括综合后仿真和功能仿真(Simulation)等。

功能仿真确实是对设计电路的逻辑功能进行模拟测试,看其是不是知足设计要求,一般是通过波形图直观地显示输入信号与输出信号之间的关系。

综合后仿真在针对目标器件进行适配之后进行,综合后仿真接近真实器件的特性进行,能精确给出输入与输出之间的信号延时数据。

ISE可结合第三方软件进行仿真,常用的工具如ModelTech公司的仿真工具ModelSim和测试激励生成器HDLBencher,Synopsys公司的VCS等。

通过仿真能及时发现设计中的错误,加快设计中的错误,加快设计进度,提高设计的可靠性。

每个仿真步骤如果出现问题,就需要根据错误的定位返回到相应的步骤更改或者重新设计。

5)下载(Download)

下载(Download)即编程(Program)设计开发的最后步骤确实是将已经仿真实现的程序下载到开发板上,进行在线调试或说将生成的配置文件写入芯片中进行测试。

在ISE中对应的工具是iMPACT。

3VHDL设计操作指南

第一进入ISE工程治理器(ProjectNavigator)界面,如下图。

ProjectNavigator是ISE所用集成工具的连接纽带,通过利用ProjectNavigator,设计者能够创建、组织和治理自己的设计。

图ISE工程管理器界面

ISE提供了许多示例工程,这些工程都存放在ISE文件当中,可以通过File->

OpenExample来打开。

ISE为我们提供了一个很有特色的工具,那就是语言辅助模板(LanguageTemplates)。

点击Edit->

LanguageTemplates,可以调用语言辅助模板,其界面如图所示。

图ISE语言辅助模板示意图

在语言模板中存放了很多HDL语言的通用语法结构和使用范例,特别是许多根据Xilinx器件IP核与硬件原语编写的实例化程序。

使用语言模板,可以方便地把这些语法结构和范例插入到设计者自己的代码文件中,大大方便了程序的编写,提高了工作效率。

语言模板按照ABEL、COREGEN、UCF、Verilog和VHDL的顺序存放在模板视窗中。

其中COREGEN的UCF是ISE新增辅助模板。

COREGEN模板由两个目录组成,分别存放当前工程中生成的IP核的Verilog和VHDL实例化文件,基内容与IP核生成器生成IP核时自动生成的实例化文件(.veo,.vho)相同。

UCF模板也分成两个目录,依次存放CPLD和FPGA的用户约束文件(.ucf)的约束范例。

这个模板使手工编辑UCF文件更加容易。

ABEL、Verilog和VHDL三大语言模板大致可以分为下列4个项目:

(1)器件例化(ComponentInstantiation):

该模板仅存在于Verilog和VHDL中,给出了块RAM(BlockRAM)、数字时钟延迟锁相环(ClockDLL)、数字时钟管理单元(DCM)、分布式RAM/ROM(DistributedRAM/ROM)、全局时钟缓冲(GlobalClockBuffer)、查找表(LUT)、基于查找表的移位寄存组(SRLUT)、I/O器件、乘法器和选择器(MUX)等器件模块的实例化范例。

(2)语法模板(LanguageTemplates):

该模板给出了基本语法规则和应用范例。

(3)综合模板(SynthesisTemplates):

该模板给出了可综合实现的一些基本单元模块的范例,如乘法器、计数器和触发器等。

(4)用户模板(UserTemplates):

该模板存放用户自己创建的特定结构,是语言模板的功能扩展。

4ISE综合利用实例

在NBA篮球竞赛中有一个24秒进攻规那么,即从获取球权到投篮击中篮板、篮框、命中或投篮被侵犯,其有效时刻合计不能超过24秒,不然被判违例,将失去球权。

在此进程中,设置24秒、启动倒计时、暂停倒计时或半途终止24秒(即球权归对方)均由裁判操纵。

本实例确实是设计一个用于篮球竞赛的24秒倒计时器,而且为了模拟现场竞赛情形,系统中设置了24秒预设键K一、倒计时启动键K2和倒计时暂停键K3,并将计时精度设置为秒。

各按键具体功能如下:

K1键按下,LED灯显示24秒;

K2键按下,倒计时;

K3键按下,计时停止。

1)新建一个工程(Project)

选择File/NewProject命令,在图所示对话框中输入工程名和工程目录,并设置器件参数。

本设计利用的器件为Spartan2,xc2s100,tq144,-5。

利用VHDL硬件描述语言编程。

点击OK按钮确认。

图新建工程对话框

2)成立和编辑VHDL源文件

选中工程,点右键选NewSource选项(如下图),添加文件,,(如下图)。

并在文件中输入相应的VHDL程序。

图添加文件对话框

图新建VHDL文件对话框

本设计中将要用到的VHDL源程序如下:

3)逻辑综合(Synthesize)

选中Synthesize选项,点

进行参数设置,

能够对任何操作进行参数设置。

设置完成后,双击Synthesize选项,或右键选择Run选项。

对其他两个VHDL程序进行一样的操作。

图综合参数设置示意图

图综合完成后界面

4)设计中的有关仿真

(1)创建Testbench波形源文件

在工程项窗口ProjectWindow的源文件中选中,用鼠标右点,在弹出的窗口中选择NewSource(如图所示),出现New对话框,再选择TestBenchWaveform文件类型,并输入文件名wave_1,点击下一步,再点击下一步,完成创建并进行初始化时间设置(如图所示)。

图选中源文件并创建Testbench波形文件

图创建Testbench波形文件的初始化时间设置

(2)设置输入信号初始值

根据被仿真模块的设计要求,对各个输入信号进行初始化设置(如图所示)。

初始化设置完毕后将testbench文件存盘,这时HDLBencher会提示我们设置希望仿真的时钟周期数(默认值为1),设置完毕后点击OK退出HDLBencher。

图输入信号的初始设置

(3)生成预期的输出响应

由于系统时钟为50MHz,要分频实现1Hz时钟波形过长,因此,下面以为例介绍仿真。

选择对应的仿真波形文件,执行GenerateExpectedSimulationResults操作(如图所示),即可得到预期的输出响应波形(如图所示),从图中可以看出,输出响应的波形满足设计要求。

点击

,可查看测试鼓励的覆盖率(如下图)。

图生成预期的输出响应操作示意图

图生成预期的输出响应

图测试激励的覆盖率示意图

(4)使用ModelSim进行仿真

根据HDLBencher中产生的预期结果,接着就可以使用Modelsim进行仿真(Simulate)Modelsim进行仿真可分为行为仿真(亦即功能仿真)和布局布线后仿真(时序仿真)。

我们先进行行为仿真。

选择,执行SimulateBehavioralVHDLModel(行为仿真)操作(如图所示),可得到如图所示的行为仿真结果,从仿真波形可以看出,仿真结果是正确的。

仿真完后关闭Modelsim主窗口退出Modelsim。

图行为仿真操作示意图

图行为仿真波形图

再进行时序仿真:

选择,执行SimulatePost-Place&

RouteVHDLModel(布局布线后仿真,即时序仿真)操作(如图所示),可得到如图所示的时序仿真结果,从仿真波形可以看出,仿真结果是正确的,并且从输入到产生输出,有一定的时间延迟。

图时序仿真操作示意图

图时序仿真波形图

依照上述的操作步骤,分别对其他程序进行有关的仿真及分析。

5)成立和编辑顶层原理图文件

关于顶层文件,即可利用VHDL文本输入方式,也可利用原理图输入方式。

那个地址咱们将利用原理图的输入方式来成立顶层文件。

(1)原理图形符号的生成(Symbol)

为了在原理图的设计中利用前面已使用VHDL进行有关设计的成果,我们先要将经过编译后的VHDL程序生成可供原理图设计中直接调用的原理图形符号。

选择,执行CreateSchematicSymbol操作(如图所示),即可生成可供原理图设计中直接调用的原理图形符号count_t。

同理,对其他两个文件执行相同的操作。

图原理图形符号的创建操作

(2)顶层原理图文件的创建

选中工程,鼠标右点,在弹出的窗口中选择NewSource(如图所示),再在弹出的窗口中选择文件的类型为Schematic,并输入文件名pic_top后,执行”下一步”,即完成了原理图文件的创建,进入原理图的编辑状态。

图原理图的创建操作

(3)原理图的编辑

①放置元件(Symbols):

在Symbols的e:

/xilinx/bin/24sec当选中所需元件的原理图符号,并在右边的图中期望的位置点左键进行放置,如下图。

假设位置不适合,可进行移动调整。

图在原理图中放置元件的操作

②元件间的连线:

点

,进行连线操作。

③放置I/O端口并编辑端口名:

,放置I/O端口。

选中端口,点右键,在弹出的对话框当选择“RenamePort”后,再在弹出的对话框中输入系统设定的端口名。

或双击端口,在弹出的对话框中输入系统设定的端口名。

④原理图的保留:

原理图编辑好后(如下图),应执行存盘操作,将原理图进行保留。

图编辑好的顶层原理图

⑤原理图错误的检查:

为了检查原理图是不是有错,可执行原理图的检错操作。

假设有错,那么更正,直到完全正确为止。

⑥原理图的逻辑综合:

假设原理图通过检查没有错误,可进行逻辑综合。

6)设计ucf文件

第一选中pic_top,按右键在弹出的窗口当选择NewSource,再在弹出的新建文件窗口当选择ImplementationConstraintsFile,并输入文件名(如下图)。

接着执行“下一步”,即进入ucf文件的编辑操作,这时咱们可依照系统的输入输出要求并参照下载板的用户手册,对系统的端口进行管脚锁定(如下图)。

管脚全数锁定并检查无误后应进行存盘操作。

图ucf文件的建立操作示意图

图本设计的ucf文件

7)设计实现

运行设计实现(ImplementDesign):

选中pic_top,运行ImplementDesign,如下图。

图运行设计实现操作图

在FloorPlanner中查看设计布局:

展开Place&

Route,运行View/EditPlacedDesign(FloorPlanner),即可查看设计布局,如图所示。

图在FloorPlanner中查看设计布局操作图

8)系统的时序仿真

在完成任务上述步骤后,咱们能够依照前面已经介绍的方式,对系统(顶层文件)进行时序仿真。

9)系统的配置和硬件验证

第一选中pic_top,执行GenerateProgrammeFile,生成配置文件,如下图。

图配置文件生成示意图

接着双击ConfigureDevice(iMPACT),启动iMPACT进行配置。

设置配置方式选为SlaveSerialMode(如图所示),对应的下载板上拨码开关也设置成SlaveSerialMode模式,即M0,M1,M2,PROG,JTAG,SV_SrI对应的状态为OFF,OFF,X,ON,OFF,ON。

单击完成,运行后弹出AddDevice对话框,选中(如图所示),点击打开按钮,这时窗口中会出现芯片图样(如图所示),点右键,选Program,即执行编程下载功能。

执行完毕后出现ProgrammingSucceeded(如图所示),则表示下载成功。

下载成功后,即可根据系统的设计要求在EDA实验开发系统上进行硬件验证。

图配置方式选择示意图

图下载文件选择示意图

图下载操作示意图

图下载成功示意图