ALU37Word格式文档下载.docx

《ALU37Word格式文档下载.docx》由会员分享,可在线阅读,更多相关《ALU37Word格式文档下载.docx(11页珍藏版)》请在冰豆网上搜索。

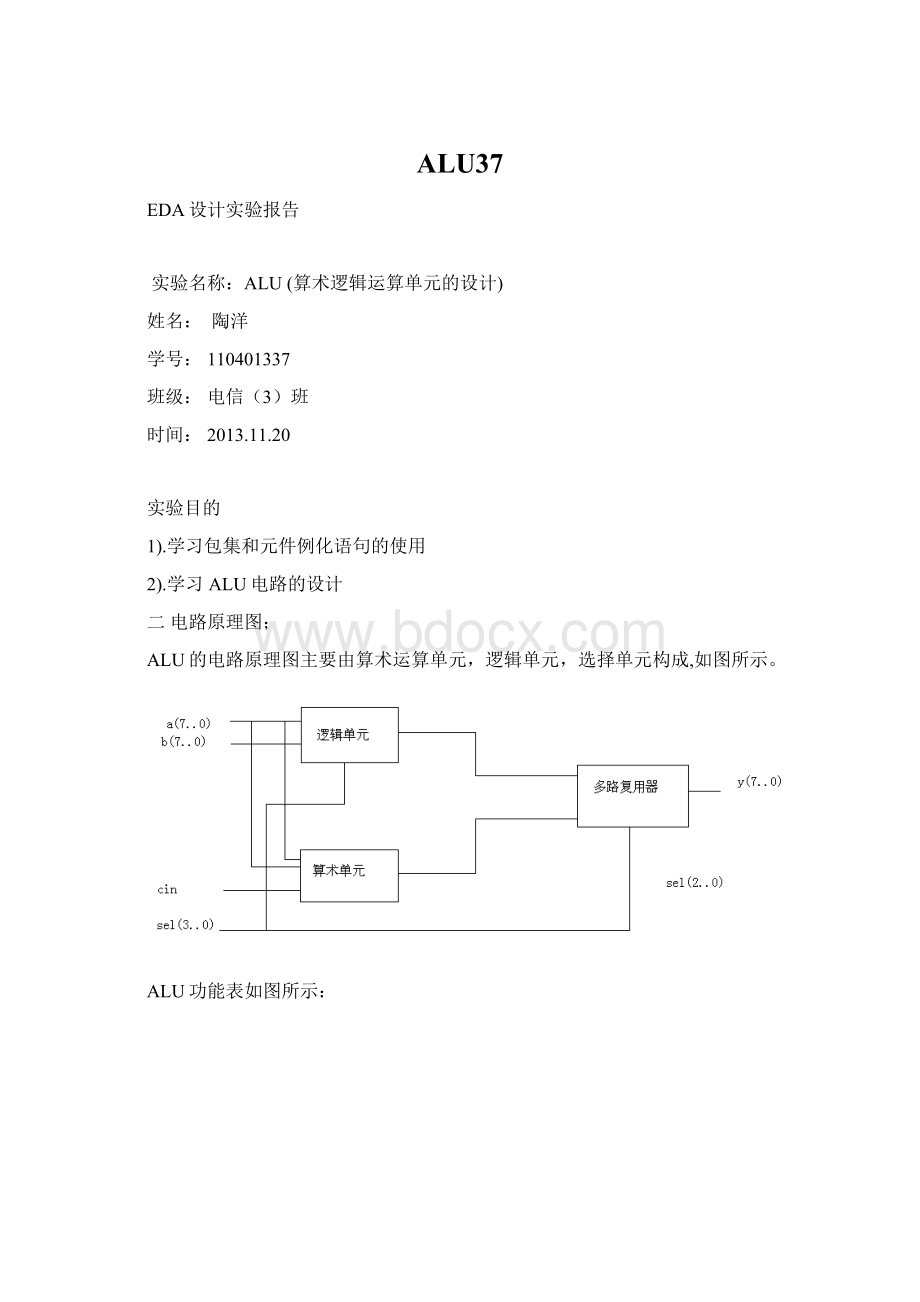

而以上三个模块是由相应的VHDL代码产生的,在VHDL输入方式下,如果要将三个模块连接起来,就要用到元件例化语句。

元件例化语句分为元件声明和元件例化。

(1)元件声明

在VHDL代码中要引入设计好的模块,首先要在结构体的说明部分对要引入的模块进行说明。

然后使用元件例化语句引入模块。

元件声明语句格式:

Component引入的元件(或模块)名

Port(端口说明);

EndComponent;

注意:

元件说明语句要放在“architecture”和“begin”之间。

(2)元件例化语句

为将引入的元件正确地嵌入到高一层的结构体描述中,就必须将被引用的元件端口信号与结构体相应端口信号正确地连接起来,元件例化语句可以实现该功能。

元件例化语句格式:

标号名:

元件名(模块名)Portmap(端口映射);

标号名是元件例化语句的唯一标识,且结构体中的标识必须是唯一的;

端口映射分为:

位置映射、名称映射。

位置映射是指Portmap中世纪信号的书写顺序与component中端口说明中的信号书写顺序一致,位置映射对书写顺序要求很严格,不能颠倒;

名称映射指Portmap中将引用的元件的端口信号名称赋予结构体中要使用元件的各个信号,名称映射的说书写要求不严格,顺序可以颠倒。

(3)包集

在实体及结构体中定义的对象、数据类型,对另外代码的实体是不能使用的。

但是在同一工程的不同VHDL文件中,有些对象、数据类型、子程序等常常被重复使用。

为方便VHDL代码的编写,简化电路设计故引入包集。

包集主要由两部分组成:

程序包说明和程序包体。

其中,程序包体是可选的,一般程序包说明列出所有项的名称,而程序包体给出各项的细节。

程序包说明中包含的内容很多,只要是通过的全局量,都可以在程序包中加以说明。

主要内容如下:

对象(常量、变量、信号)的数据类型说明。

对象(常量、变量、信号)子类型的数值范围说明。

函数与过程说明。

元件语句说明。

程序包说明书写格式如下:

Package程序包名1is

说明语句;

End程序包名;

程序包名:

设计者自定义便于记忆的标识符。

说明语句;

包括各种类型的说明语句。

程序包体书写格式如下:

Packagebody程序包名is

顺序语句;

注意:

程序包定义的内容不是自动可见的,不是自动被使用。

若摸个实体及结构体设计需要使用程序包,可以使用use语句制定要使用的程序包。

代码,要增加注释;

ALU的VHDL代码如下:

alu_unit_37_38

libraryieee;

useieee.std_logic_1164.all;

--调用1164包

usework.alu_37_38.all;

entityalu_unit_37_38is

port(a,b:

instd_logic_vector(7downto0);

--a,b为8位的逻辑矢量输入类型

clk:

instd_logic;

--clk为逻辑量输入

cin:

--cin为逻辑量输入

selout:

outstd_logic_vector(3downto0);

--selout为4位的逻辑矢量输出类型

y:

outstd_logic_vector(7downto0));

--y为8位的逻辑矢量输出类型

end;

architecturerhgofalu_unit_37_38is

signalx1,x2:

std_logic_vector(7downto0);

signalx3:

std_logic_vector(3downto0);

begin

u1:

arith_37_38portmap(a,b,x3,cin,x1);

--与元件arith_27_28的端口映射

u2:

logic_37_38portmap(a,b,x3,x2);

--与元件logic_unit_27_28的端口映射

u3:

sel_37_38portmap(x3,x1,x2,y);

--与元件sel_27_28的端口映射

u4:

clk_37_38portmap(clk,x3);

--与元件clk_27_28的端口映射

selout<

=x3;

end;

arith_37_38

useieee.std_logic_unsigned.all;

entityarith_37_38is

--将a,b定义为8位的逻辑矢量输入类型

sel:

instd_logic_vector(3downto0);

--定义为4位的逻辑矢量输入类型

cin:

x:

architecturerhgofarith_37_38is

begin

withselselect--选择信号赋值语句

x<

=awhen"

0000"

--当sel为"

时,将a的值赋给x

a+1when"

0001"

a-1when"

0010"

bwhen"

0011"

b-1when"

0101"

a+bwhen"

0110"

a+b+cinwhen"

0111"

--当sel为"

时,将a+b+cin的值赋给x

"

00000000"

whenothers;

endrhg;

logic_37_38

entitylogic_37_38is

--将sel定义为4位的逻辑矢量输入类型

--将x定义为8位的逻辑矢量输出类型

architecturerhgoflogic_37_38is

=notawhen"

1000"

时,将a非的值赋给x

notbwhen"

1001"

aandbwhen"

1010"

anandbwhen"

1100"

anorbwhen"

1101"

axorbwhen"

1110"

not(axorb)when"

1111"

时,将a异或b的非的值赋给x

sel_37_38

entitysel_37_38is

port(sel:

--定义sel数据类型为逻辑矢量,宽度为4位

arith:

--定义arith为逻辑矢量,宽度为8位

logic:

--定义logic为逻辑矢量,宽度为8位

y:

--定义y为逻辑矢量,宽度为8位

architecturerhgofsel_37_38is

withsel(3)select--信号赋值语句

y<

=arithwhen'

0'

--当sel的最高位为0时,将arith的值赋给y

logicwhenothers;

--当sel的最高位不为0时,将logic的值赋给y

clk_37_38

entityclk_37_38is

port(clk:

bufferstd_logic_vector(3downto0));

--将y定义为buffer的4位逻辑矢量

architecturerhgofclk_37_38is

process(clk)--clk作为敏感信号

variables:

begin

ifclk'

eventandclk='

1'

then

ifs="

s:

="

;

else

=s+1;

endif;

endif;

=s;

endprocess;

end;

packagealu_37_38

packagealu_37_38is

componentarith_37_38

--cin为逻辑矢量输入类型

--x为8位的逻辑矢量输出类型

endcomponent;

componentlogic_37_38

--sel为4位的逻辑矢量输入类型

componentsel_37_38

arith:

--arith为8位的逻辑矢量输入类型

--logic为8位的逻辑矢量输入类型

componentclk_37_38

--y定义为buffer的4位逻辑矢量

endalu_37_38;

仿真波形图,对波形进行分析;

1)算术单元仿真波

2)逻辑单元仿真波形

3)Sel仿真波形

4)Alu仿真波形

总结与体会

通过这次试验掌握了ALU的设计,并对结构体的说明部分对要引入的模块进行说明,说明语句要放在“architecture”和“begin”之间。

还有就是注意程序包定义的内容不是自动可见的,不是自动被使用。

学的时间感觉不会的东西越多,如果课前不准备感觉在有限的时间内很难做出老师的要求,上电看到正确的现象我一点都不觉得累,感觉时间过得好快啊。