彩灯控制电路设计与实现VHDL编程Word文件下载.docx

《彩灯控制电路设计与实现VHDL编程Word文件下载.docx》由会员分享,可在线阅读,更多相关《彩灯控制电路设计与实现VHDL编程Word文件下载.docx(10页珍藏版)》请在冰豆网上搜索。

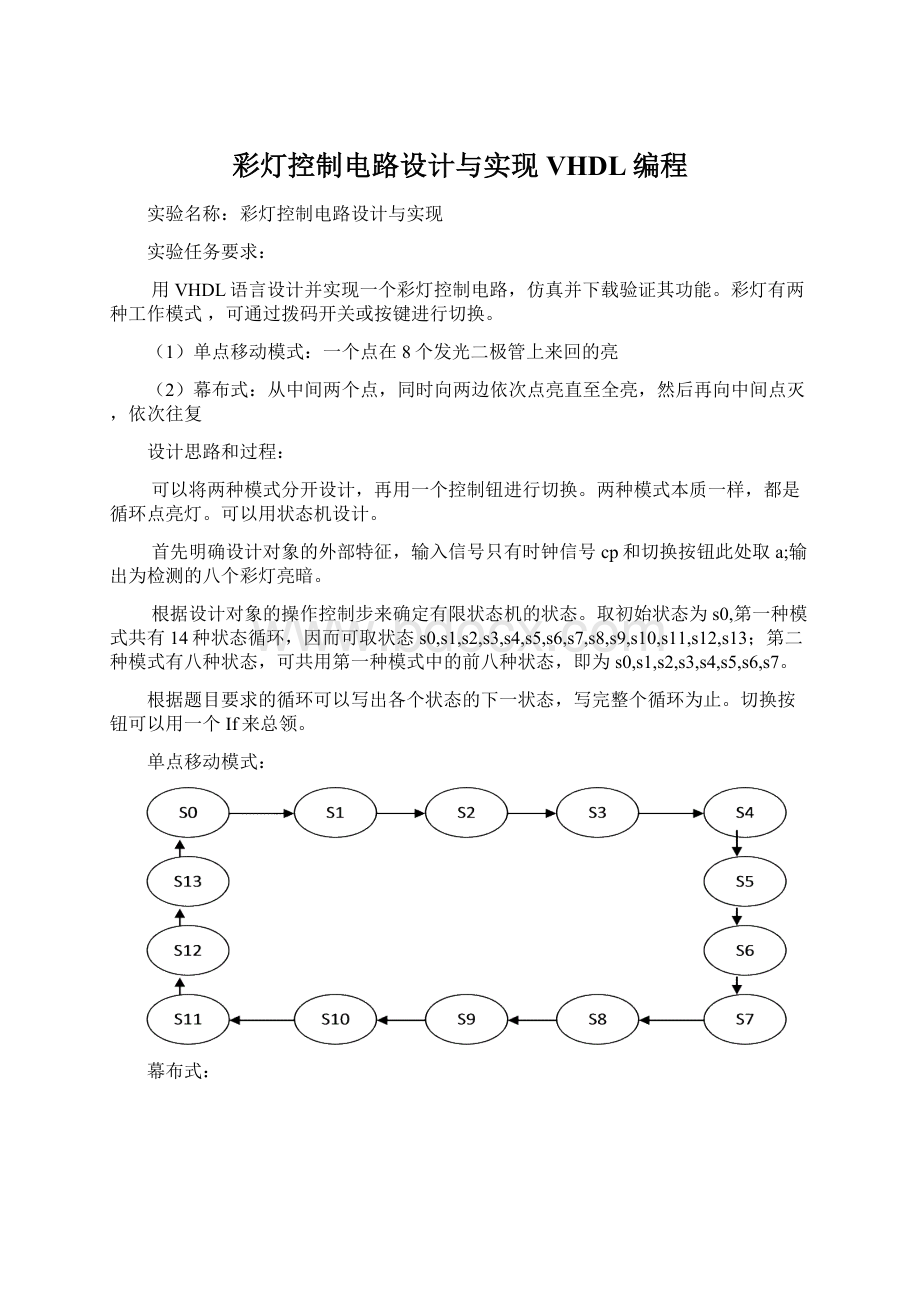

根据设计对象的操作控制步来确定有限状态机的状态。

取初始状态为s0,第一种模式共有14种状态循环,因而可取状态s0,s1,s2,s3,s4,s5,s6,s7,s8,s9,s10,s11,s12,s13;

第二种模式有八种状态,可共用第一种模式中的前八种状态,即为s0,s1,s2,s3,s4,s5,s6,s7。

根据题目要求的循环可以写出各个状态的下一状态,写完整个循环为止。

切换按钮可以用一个If来总领。

单点移动模式:

幕布式:

流程图:

彩灯电路设计语言:

libraryieee;

useieee.std_logic_1164.all;

entitypmdis

port(

a,cp:

instd_logic;

%输入信号

deng:

outstd_logic_vector(7downto0)%输出灯信号

);

endpmd;

architecturearchofpmdis

typeall_stateis(s0,s1,s2,s3,s4,s5,s6,s7,s8,s9,s10,s11,s12,s13);

%枚举状态机状态

signalstate:

all_state;

%状态转换符号

begin%开始程序

process(cp)

begin

if(cp'

eventandcp='

1'

)then%时钟信号开始计数

if(a='

)then%单点循环模式

casestateis

whens0=>

state<

=s1;

deng<

="

00000001"

;

%状态循环

whens1=>

=s2;

00000010"

whens2=>

=s3;

00000100"

whens3=>

=s4;

00001000"

whens4=>

=s5;

00010000"

whens5=>

=s6;

00100000"

whens6=>

=s7;

01000000"

whens7=>

=s8;

10000000"

whens8=>

=s9;

whens9=>

=s10;

whens10=>

=s11;

whens11=>

=s12;

whens12=>

=s13;

whens13=>

=s0;

whenothers=>

state<

00000000"

endcase;

Else%切换为幕布式

00011000"

00111100"

01111110"

11111111"

endif;

endprocess;

endarch;

输入波形:

添加五十分频后的仿真程序:

entitycdis

a,clk:

q:

outstd_logic_vector(7downto0)

endcd;

architectureaofcdis

signalcnt:

integerrange0to24999999;

%50分频状态

signalclk_tmp:

std_logic;

begin

process(clk)

Begin%开始运行分频信号

if(clk'

eventandclk='

)then

ifcnt=24999999then

cnt<

=0;

clk_tmp<

=notclk_tmp;

else

=cnt+1;

endif;

endif;

if(clk_tmp'

eventandclk_tmp='

)then%分频后运行彩灯程序

)then

q<

else

enda;

useieee.std_logic_arith.all;

useieee.std_logic_unsigned.all;

process(clk)

if(clk'

故障及问题分析:

1.编写这个程序时,很自然地想到用一个输入信号控制两种模式的切换,但把这个输入放在哪里,如何放,开始出现了几种想法。

先是用when来引出a=0&

a=1两种模式,结果出现了错误,后改用if……if来总领,感觉太罗嗦,但可行,最后定为if……else……,这样比较清晰的表达了分组的目的,取得了较好的效果。

2.在确定有限状态机的状态个数时,一开始只是用了8个状态,第一种工作模式循环出现了混乱(虽然第一种模式只有8种状态),古尔改采用14个状态表示,第二种模式共用第一种模式的前八种状态,虽然看上去比较罗嗦,但这样使得整个程序运行比较顺畅,看起来也相对比较明了。

3.在验收虽然本程序得到了通过,但是state描述两个或多个状态时可能会发生锁存器错误,产生记忆效应,因而可以将state改命名为state_1和state_2,这样看起来就不会混乱了。

总结和结论:

《数字电路与逻辑设计实验》这门课总共虽然只有四次课堂实验,但是我还是学到了很多东西。

第一次和第二次实验都是实验板的接线。

第一次是集成门电路电压参数的测量,让我熟悉了TTL电路和COMS电路的使用规则,掌握了集成门电路的电路外特性参数的测量方法及其物理意义,并熟悉了实验板的结构和使用方法,为下面的实验打好了基础。

第二次是组合逻辑电路冒险的研究和消除,在第一次实验的经验基础上可以较顺利地完成此次实验,这次试验将课本中学关于冒险的理论充分应用到实际中的,让我们清楚地看到了冒险并尝试找到了一些解决冒险的方法,为理论到实践搭建了桥梁。

第三、四次试验都是基于一款在电路中应用十分广泛也是十分重要的软件quartusII的实验。

通过第三次试验熟悉了用quartusII原理图输入法进行电路设计和仿真,熟悉了电路板是使用。

第四次实验是用quartusII文本输入法进行电路设计和仿真,用到了VHDL语言设计组合逻辑电路,让我学习了一种新的设计语言,为以后从事电路设计方面的工作打了个基础,并让我体会到VHDL语言的强大。

通过《数字电路与逻辑设计实验》这门课程的学习,我进一步加深了对数字电路理论课程的理解,并自己动手了解到一些逻辑器件的使用。

通过quartusII软件的使用,懂得了逻辑图的画法,并编写VHDL语言进一步解了各个端口的关系。

这次试验课开阔了我的眼界,加强了我动手能力,相信这些为我以后的在电路方面的学习和工作都提供了莫大的帮助。