微机原理及应用习题库硬件应用设计题Word文件下载.docx

《微机原理及应用习题库硬件应用设计题Word文件下载.docx》由会员分享,可在线阅读,更多相关《微机原理及应用习题库硬件应用设计题Word文件下载.docx(37页珍藏版)》请在冰豆网上搜索。

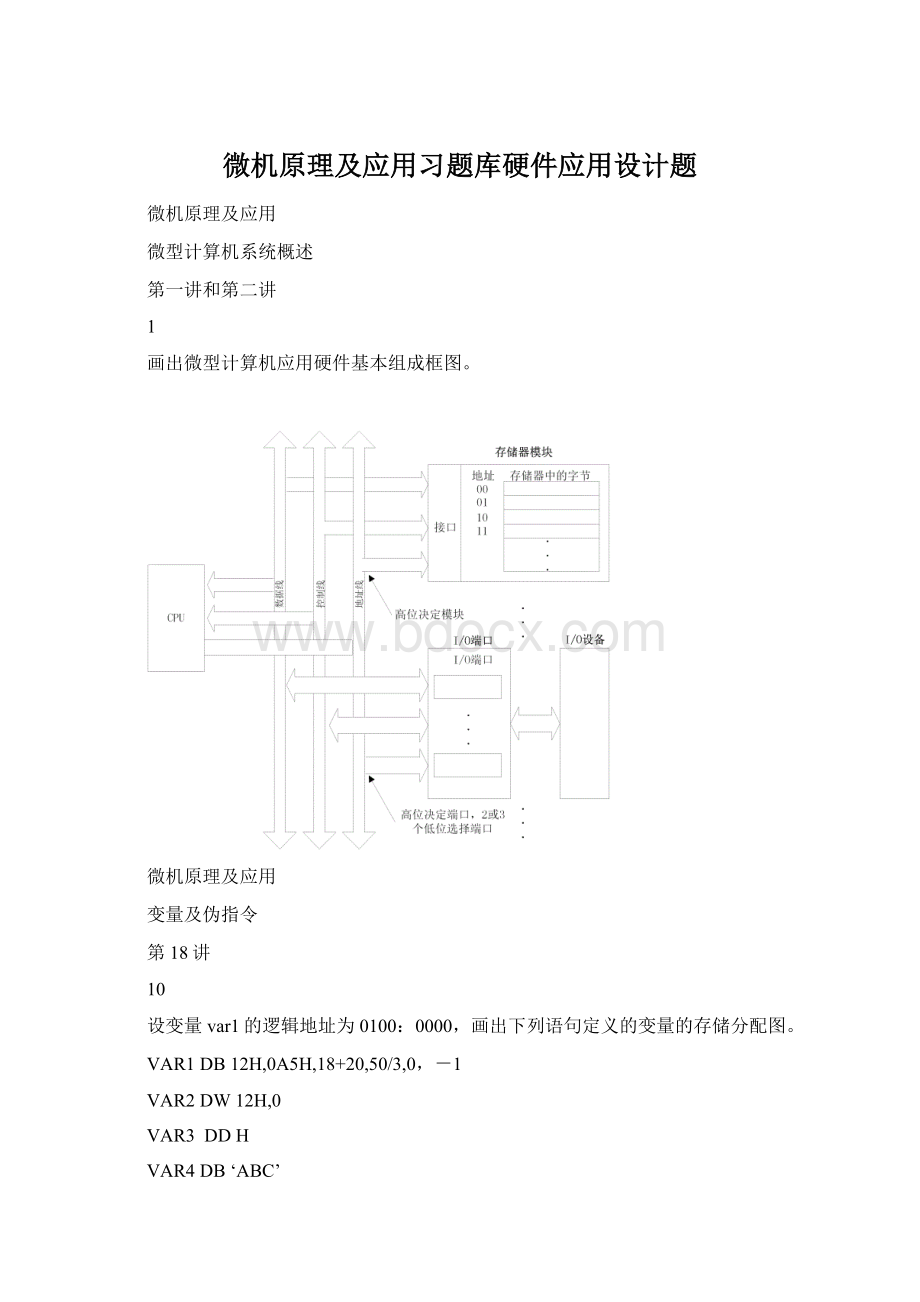

使用的数据引脚

读或写偶地址的一个字

0 0

AD15~AD0

读或写偶地址的一个字节

1 0

AD7~AD0

读或写奇地址的一个字节

01

AD15~AD8

读或写奇地址的一个字

(第1个总线周期放低位数据字节)

AD7~AD0

(第2个总线周期放高位数据字节)

画出8086CPU工作在最大方式时的系统总线读时序图。

15

画出8086CPU工作在最小方式时的系统总线结构。

画出8086CPU工作在最大方式时的系统总线结构。

存储器设计

第47~50讲

说明计算机中内存储器的分类。

在8088CPU工作在最大方式组成的微机应用系统中,扩充设计8kB的SRAM电路,SRAM芯片用Intel6264。

若分配给该SRAM的起始地址为62000H,片选信号(

)为低电平有效。

请用全地址译码方法设计该SRAM存储器的片选信号形成电路。

因为Intel6264的片容量为8k×

8b(8kB),因此只需要1片Intel6264存储器芯片。

由于Intel6264片内地址线有13根,所以8088CPU系统地址总线的低13位A12~A0直接与Intel6264的片内地址引脚A12~A0相连接,作片内寻址,来选择片内具体的存储单元。

由于采用全地址译码,所以8088CPU系统地址总线的高7位A19~A13全部参加译码,其译码输出作为存储器芯片的片选信号

。

当

有效时,对应的存储器地址范围为62000H~63FFFH连续的8kB存储区域。

在8088CPU工作在最小方式组成的微机应用系统中,扩充设计8kB的SRAM电路,SRAM芯片用Intel6264。

若分配给该SRAM的地址范围为00000H~0FFFFH,片选信号(

请用部分地址译码方法设计该SRAM存储器的片选信号形成电路。

而题目给出的地址范围为00000H~0FFFFH,共64kB,说明有8个地址重叠区,即采用部分地址译码时,有3条高位地址线(A15、A14和A13)不参加译码。

由于8088CPU工作在最小方式,所以,

=0要参加译码。

根据以上设计原则设计的SRAM存储器的片选信号(

)形成电路如图所示。

在某8088微处理器系统中,需要用8片6264构成一个64kB的存储器。

其地址分配在00000H~0FFFFH内存空间,地址译码采用全译码方式,用74LS138作译码器,请画出存储器译码电路。

根据题目已知条件和74LS138译码器的功能,设计的存储器译码电路如下图所示。

图中74LS138的每一个输出端均与一块6264芯片的片选端相连,8个输出端分别选通1个8kB的存储空间(即1个6264模块),共占有64kB内存空间。

利用74LS688设计译码电路,输出端

作为Intel62128SRAM的

片选信号,分配给Intel62128的地址范围为74000H~77FFFH。

画出8088CPU工作在最大方式下的译码电路。

由于Intel62128为16kBSRAM,片内寻址的地址引脚为14条,故片外寻址用于参加译码的地址线为A19~A14共6根。

用74LS688进行译码时,将高位地址线A19~A14接在74LS688P边的P5~P0,P边多余的两条线接到固定的高电平(也可以直接接到地上)。

74LS688的Q边通过短路插针,接成所需编码,Q边与P边相对应的多余输入脚接成相同的高电平。

根据Q边插成的二进制编码,Q5和Q1接地(低电平),其余的全接高电平。

在8088CPU工作在最大方式下与系统总线相连的译码电路如下图所示。

18

在8088CPU工作在最大方式组成的微机系统中,扩充设计16kB的SRAM存储器电路,存储器芯片选用Intel6264,起始地址为80000H,且地址是连续的,译码器用74LS138。

(1)此SRAM存储区的最高地址是多少

(2)画出此存储电路与8088系统总线的连接图。

(3)用一种RAM自检方法编写此RAM区的自检程序。

(1)因为Intel6264的片容量为8kB,因此由2片Intel6264构成连续的RAM存储区域的总容量为2×

8kB=16kB。

其可用的最高RAM地址为:

80000H+4000H-1=83FFFH

(2)此存储电路与8088系统总线的连接如下图所示。

(3)RAM上电自检是指检测RAM工作是否正常,即检测RAM读写是否正常、数据线是否有“粘连”故障、地址线是否有“链桥”故障等。

在实际的工程应用中,RAM自检常采用55H和AAH数据图案检测、谷(峰)值检测、数据图案平移检测等方法。

采用55H和AAH数据图案检测的原理是给要检测的RAM存储区的每个地址单元分别写入55H和AAH数据,并将写入的数据读出比较,如与写入的数据一致,表明该地址单元数据读写正常,否则表明工作不正常,应作出相应的出错报警提示。

用55H和AAH数据图案进行RAM检测的参考程序如下:

MOVAX,8000H

MOVDS,AX

MOVSI,0

MOVCX,16*1024

MOVAL,55H

NEXT1:

MOV[SI],AL

MOVBL,[SI]

CMPBL,AL

JNEERROR

INCSI

LOOPNEXT1

MOVAL,0AAH

NEXT2:

LOOPNEXT2

ERROR:

画出8086对应的1MB字节的存储器组成原理框图。

在8086最小方式系统中,利用2片Intel6264构成连续的RAM存储区域,起始地址为00000H,求可用的最高RAM地址,并利用74LS155设计译码电路,画出此RAM电路与8086最小方式系统的连接图。

Intel6264的存储容量为8k×

8,因此由2片Intel6264构成连续的RAM存储区域的总容量为2×

8kB=16kB=04000H,其可用的最高RAM地址为:

00000H+04000H-1=03FFFH

由于8086系统有16位数据总线,因此应将存储器模块分成两组:

奇片和偶片,然后通过译码电路产生片选信号。

在8086最小方式下,若系统要求16kB的ROM和16kB的RAM,ROM区的地址为FC000H~FFFFFH,RAM区地址为00000H~03FFFH,ROM采用两片2764(8k×

8)EPROM芯片,RAM采用两片6264(8k×

8)SRAM芯片。

试画出此存储电路与8086最小方式下系统总线的连接图。

8086最小方式系统与存储器读写操作有关的信号线有:

地址总线A0~A19,数据总线D0~D15,控制信号

,

简单I/O设计

第55~56讲

画出一个基本的I/O接口逻辑的组成框图。

画出无条件传送方式下数据输入端口的典型结构组成框图。

画出无条件传送方式下数据输出端口的典型结构组成框图。

画出程序查询输入/输出方式的程序处理流程图。

画出对多个设备的程序查询输入/输出方式的程序处理流程图。

在PC/XT系统总线上扩充设计一个数据输出端口,分配给该端口的地址为280H,输出端口芯片用74LS374,输出设备为8个LED发光二极管。

(1)画出此输出端口与PC/XT系统总线以及与LED发光二极管的连接图。

(2)编写使8个LED发光二极管每间隔一段时间交替亮灭的功能段程序。

74LS374的功能和74LS373相同,都是8位数据输出锁存器,不同之处是使能信号的有效形式,74LS374的使能信号CP为上升沿有效。

LED发光二极管导通时流过的电流应

20mA,否则会损坏器件。

设计的此输出端口与PC/XT系统总线以及与LED发光二极管的连接图如下图所示。

编写使8个LED发光二极管每间隔一段时间交替亮灭的功能段程序如下:

MOVDX,280H

LOP:

MOVAL,0FFH

OUTDX,AL;

使8个LED发光二极管亮

CALLDELAY1S;

调用1秒延时子程序

MOVAL,00H

使8个LED发光二极管灭

JMPLOP

在8086CPU工作在最小方式组成的微机系统中,扩充设计一个数据输入端口,分配给该端口的地址为8001H,输入端口芯片用74LS245,输入设备为8个乒乓开关。

(1)画出此输入端口与8086系统总线以及与输入设备的连接图。

(2)编写程序检测K0开关,若K0断开,程序转向PROG1;

K0闭合,程序转向PROG2。

由于为8086系统,且端口地址8001H为奇地址,所以使用高8位数据线,且在I/O端口地址译码中,

=0要参加译码。

设计的此输入端口与8086系统总线以及与输入设备的连接图如下图所示。

若K0开关断开程序转向PROG1,K0闭合程序转向PROG2的程序如下:

MOVDX,8001H

INAL,DX

TESTAL,01H

JZPROG2

PROG1:

PROG2:

某一输出设备的工作时序如图A所示。

当它不忙时,其状态信号BUSY=0,CPU可经接口向外设输出数据,而当数据加到外设上时,必须利用

负脉冲将数据锁存于外设,并命令外设接收该数据。

图A外设工作时序

试将其外设连接到8088系统总线上。

编程序实现将内存40000H开始的连续50个字节单元的数据,利用查询法输出给该设备。

选用两片74LS273分别作数据输出和

命令输出端口寄存器,利用1片74LS244作BUSY状态输入端口寄存器,译码器用74LS138。

设数据输出端口地址为02F8H,命令输出端口地址为02F9H,状态输入端口地址为02FAH,则设计的用查询方式实现的接口电路如图B所示。

图B用查询方式实现的接口电路

将内存40000H开始的连续50个字节单元的数据,利用查询法输出给该设备的程序如下:

MOVAX,4000H

MOVDS,AX

MOVSI,0

MOVCX,50;

初始化

MOVDX,2F9H

MOVAL,01H

OUTDX,AL;

使

=1

GODON:

MOVDX,2FAH

WAIT1:

INAL,DX

TESTAL,80H;

查询外设状态

JNZWAIT1;

若忙,则等待

MOVDX,2F8H

MOVAL,[SI]

输出数据

MOVAL,00H

=0,输出负脉冲

NOP

LOOPGODON

HLT

中断系统

第58~60讲

如果外设2的中断优先权高于外设1,假设8259A工作于完全嵌套方式,试画出中断嵌套过程。

画出8086CPU的内部中断源和外部中断源的示意图。

画出8086CPU的外部可屏蔽中断的响应过程时序图。

简单画出IBMPC/AT机中两片8259A级联的连线图。

在某微机系统中配置了一片8259A可编程中断控制器芯片,且初始化为完全(正常)嵌套方式,即中断优先权的级别是固定的,IR0优先权最高,IR1~IR6逐级次之,IR7最低。

IR0~IR7均未屏蔽,CPU处于开中断状态,在每个中断服务程序开始均排有STI指令。

若在CPU执行程序期间,IR2和IR4同时有中断请求,在IR2服务期间(服务结束前),IR1有中断请求,在IR4服务期间,IR3有中断请求。

试画出完全嵌套方式的中断响应过程示意图。

由于是完全嵌套方式,所以根据题目给出的各中断请求的次序,画出的中断响应篏套过程示意图如下图所示。

若要开发一条INT40H软件中断指令,该指令完成的功能为光标回车换行。

设中断服务程序的入口地址为INTRUP,使编写完成此功能的主程序和中断服务程序。

所要开发的软件中断指令为INT40H,说明该软件中断源的中断类型号为40H,所以要在主程序中将中断向量(中断服务程序的入口地址)建立在中断向量表的40H×

4双字单元中。

;

主程序

…

PUSHDS;

关中断,开始建立中断向量

MOVAX,0

MOVDS,AX;

使DS指向中断向量表的段基址

MOVBX,40H*4;

使BX指向中断向量表的段内40H×

4偏移地址

MOVAX,OFFSETINTRUP

MOV[BX],AX;

将中断向量的偏移地址存入向量表的40H×

4单元

MOVAX,SEGINTRUP

MOV[BX]+2,AX;

将中断向量的段基址存入向量表的40H×

4+2单元

POPDS

INT40H;

40H号软中断调用,使光标回车换行

中断服务程序

INTRUP:

PUSHAX

PUSHBX;

保护现场

MOVAH,02H;

显示回车

MOVDL,0DH

INT21H

显示换行

MOVDL,0AH

POPAX;

恢复现场

POPBX

IRET

以下图中的输入设备为例,使用PC/XT机中的8259A的IR3引脚申请中断,中断类型OBH。

给出一个完整的中断方式输入程序。

设该输入设备的数据端口地址为240H,8259A端口地址为20H、21H。

输入“回车”字符表示结束。

STACKSEGMENTSTACK

DB256DUP()

STACKENDS

DATASEGMENT

IN_BUFFERDB100DUP();

接收缓冲区,假设一次输入不超过100B

IN_POINTERDW;

接收缓冲区指针

INT_IMRDB

DATAENDS

CODEMSEGMENT

ASSUMECS:

CODEM,DS:

DATA,SS:

STACK

START:

MOVAX,SEGIN_INTR;

IN_INTR是中断服务程序入口

LEABX,IN_INTR

MOVAX,250BH;

AH中为功能号,AL中为中断类型

INT21H;

设置中断向量

MOVAX,DATA

装载数据段段基址

MOVIN_POINTER,OFFSETIN_BUFFER;

设置指针初值

INAL,21H;

读8259A的IMR

MOVINT_IMR,AL;

暂存中断屏蔽字

ANDAL,1110111B

OUT21H,AL;

清除IR3的屏蔽位

STI

W:

MOVAH,06H

MOVDL,0FFH

CMPAL,0DH

JNZW;

等待数据输入完成,同时等待中断

MOVAL,INT_IMR;

输入结束,恢复原屏蔽字

OUT21H,AL

…;

结束处理

MOVAX,4C00H

CODEENDS

CODESSEGMENT

ASSUMECS:

CODES

IN_INTRPROCFAR

PUSHAX

PUSHBX

PUSHDX

STI;

开放中断,允许响应更高级中断

MOVBX,IN_POINTER;

装载缓冲区指针

MOVDX,240H

INAL,DX;

从输入设备读取一个数据,同时清除中断请求

MOV[BX],AL;

数据存入缓冲区

INCBX

MOVIN_POINTER,BX;

修改指针,存入单元

EXIT:

CLI;

关闭中断,准备中断返回

MOVAL,20H

OUT20H,AL;

向8259A发中断结束命令

POPDX

POPAX

IRET;

中断返回

IN_INTRENDP

CODESENDS

ENDSTART

可编程并行接口芯片8255A及应用

第61讲和第62讲

画出可编程并行接口芯片8255A的工作方式字的每位的含义。

在8086最小方式系统中,利用8255A某端口输入8位开关量,并通过另一个端送出,以发光二极管指示数据,灯亮表示数据“1”,灯灭表示数据“0”。

8255A的端口地址为280H~287H中的奇地址,设计系统总线与8255A的连接电路,并编程实现。

按照题目要求,可以采用端口A输入开关量(数字量),采用端口B输出数据,而且没有增加联络信号的必要,因此可以采用最简单的方式0。

为了使发光二极管具有足够的亮度,我们采用图示的方法连接,这时,当端口B的某一位为0时,相应的发光二极管亮,这一点可以通过程序进行控制。

8255A与8086最小方式系统的连接关系如下图所示。

8255A的应用程序段如下:

MOVDX,287H;

设置8255A的工作方式

MOVAL,B;

端口A方式0输入,端口B方式0输出

OUTDX,AL

RER1:

MOVDX,281H;

从端口A读取开关量

INAL,DX

NOTAL;

按位取反

MOVDX,283H;

从端口B送出

OUTDX,AL

JMPRER1

在8088最大方式系统中,由一片8255A构成输入输出接口,端口地址为240H~243H,外设准备好的8位数据已送入8255A的某端口,要求将这一数据的低4位取反(高4不变)后,从另一端口送出。

要求:

(1)说明各端口的工作方式;

(2)编写8255初始化及输入输出程序段。

解:

由于题目给定已经将外设准备好的8位数据送入8255A的某端口(可设为端口A),因此A组可以设定为方式1输入。

对输出端口(设为端口B)题目并没有限定,我们可以将B组设定成方式0输出。

8255初始化及输入输出程序段如下:

MOVDX,243H;

设定8255A的工作方式

MOVAL,B

MOVDX,240H;

从端口A读数据

XORAL,0FH;

低4位取反,高4不变

MOVDX,242H;

在8088最大方式系统中,有一片8255A,其端口地址为20H、22H、24H、26H,采用低8位地址总线设计译码电路及与系统总线的连接图,并编程实现使端口A的低4位产生如图C所示的信号(各个信号的节拍不必严格相等)。

图C端口A信号波形

根据8255A在8088最大方式系统中的端口地址,可以画出8255A与系统总线的连接框图,如图D所示。

为使8255A的端口A产生如图所示的信号,可以将端口A设定成方式0输出,端口B和C与本题无关,均设定为方式0输出。

端口A低4位的波形为分频形式,因此,可以通过计数方式实现。

程序段如下:

MOVDX,26H;

MOVAL,10000000B

MOVDX,