基于CPLD的数字锁Word文档下载推荐.docx

《基于CPLD的数字锁Word文档下载推荐.docx》由会员分享,可在线阅读,更多相关《基于CPLD的数字锁Word文档下载推荐.docx(11页珍藏版)》请在冰豆网上搜索。

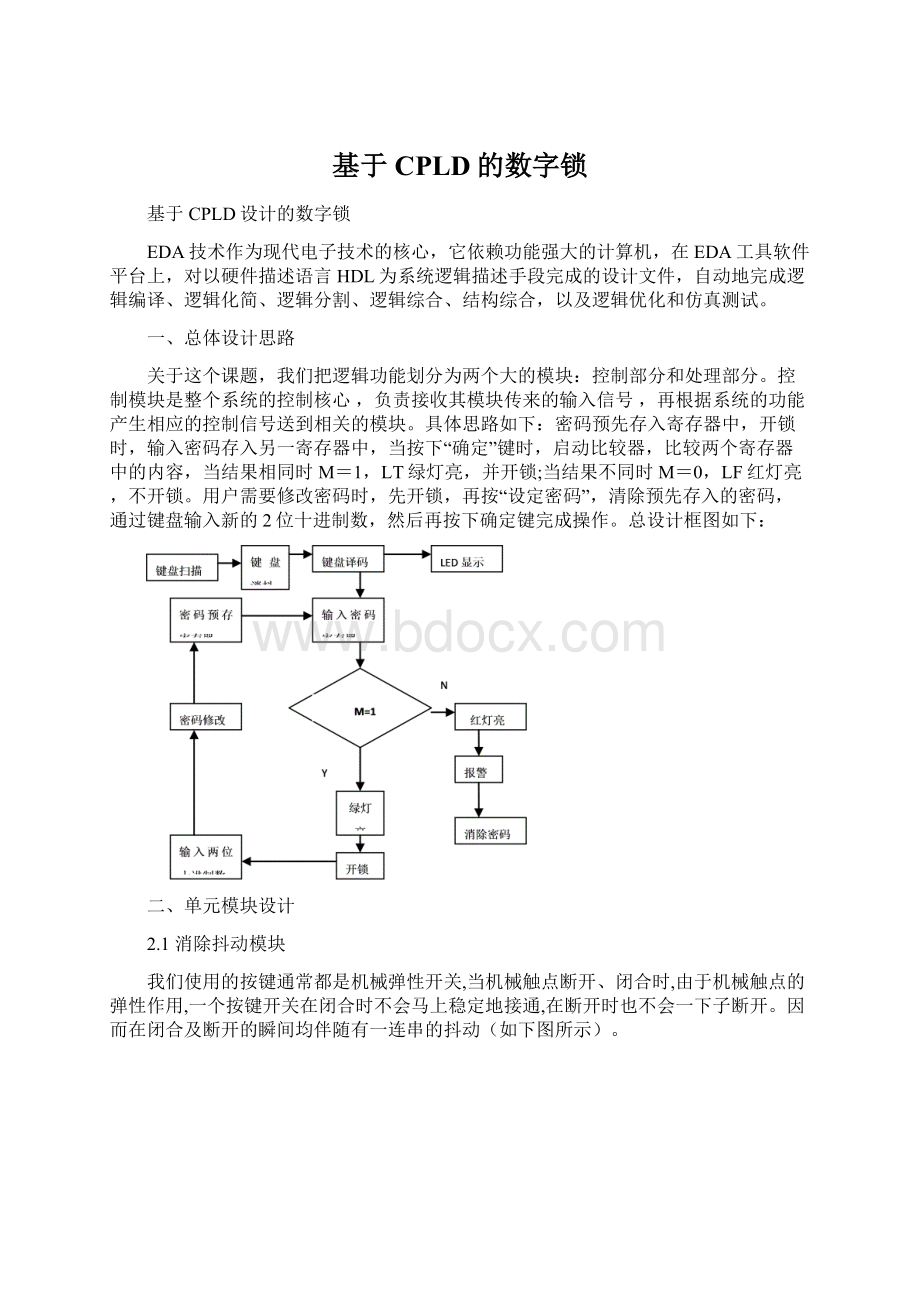

PORT

(CLK,B_IN:

INSTD_LOGIC;

B_OUT:

OUTSTD_LOGIC);

END;

ARCHITECTUREaOFxiaodouIS

signalVcc,INV_B:

std_logic;

signalA0,A1:

signalB0,B1:

BEGIN

Vcc<

='

1'

;

INV_B<

=notB_IN;

dff1:

dffPORTMAP(d=>

Vcc,q=>

A0,clk=>

CLK,prn=>

Vcc,clrn=>

INV_B);

dff2:

A1,clk=>

process(CLK)

begin

ifCLK'

EVENTandCLK='

then

B0<

=notA1;

B1<

=B0;

endif;

endprocess;

B_OUT<

=not(B1andnotB0);

消抖电路的仿真波形图:

2.2键盘扫描模块

我们在键盘的四列输入口中输入一个低电平时钟扫描,当有按键被打下时,对应的行被键接通也呈现低电平状态,然后将此输入输出信号输出到键盘编码就可以进行键盘按键识别了。

键盘扫描封装图如下:

该模块程序如下:

LIBRARYIEEE;

USEIEEE.std_logic_1164.ALL;

USEIEEE.STD_LOGIC_ARITH.ALL;

USEIEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITYSAOMIAOIS

PORT(

CLK:

INSTD_LOGIC;

CLK_SAOMIAO:

OUTSTD_LOGIC_VECTOR(4downto1));

ARCHITECTUREaOFSAOMIAOIS

SignalM:

STD_LOGIC_VECTOR(2DOWNTO1);

SIGNALN:

STD_LOGIC_VECTOR(4DOWNTO1);

Begin

PROCESS(CLK)

IFCLK'

EventANDCLK='

THEN

N<

=N+1;

M<

=N(4DOWNTO3);

ENDIF;

ENDPROCESS;

CLK_SAOMIAO<

="

1110"

WHENM=0ELSE

"

1101"

WHENM=1ELSE

1011"

WHENM=2ELSE

0111"

WHENM=3ELSE

1111"

;

键盘扫描模块仿真图:

2.3七段数码显示电路模块

本模块我们通过串行扫描方式驱动LED数码管,可较少地占用可编程器件资源;

并利用MAXPLUSⅡ对动态扫描LED显示电路进行仿真。

显示电路模块封装图如下:

程序如下:

USEIEEE.STD_LOGIC_1164.ALL;

USEIEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITYSCAN_LEDIS

PORT(A:

INSTD_LOGIC_VECTOR(6DOWNTO0);

B:

E:

OUTSTD_LOGIC_VECTOR(6DOWNTO0);

BT:

OUTSTD_LOGIC_VECTOR(1DOWNTO0));

END;

ARCHITECTUREONEOFSCAN_LEDIS

STD_LOGIC_VECTOR(1DOWNTO0);

BEGIN

PROCESS(N)

CASENIS

WHEN"

00"

=>

BT<

="

01"

E<

=A;

10"

=B;

WHENOTHERS=>

NULL;

ENDCASE;

ENDPROCESS;

PROCESS(CLK)

EVENTANDCLK='

THEN

N<

=N+1;

END;

七段数码显示电路仿真图:

2.4译码电路模块

本模块上接键盘扫描模块,下接七段数码显示电路模块。

主要功能是实现键盘的译码。

该模块封装图如下:

具体程序如下:

LIBRARYIEEE;

ENTITYkeycodeIS

PORT(X:

INSTD_LOGIC_VECTOR(2DOWNTO0);

Y:

INSTD_LOGIC_VECTOR(3DOWNTO0);

XT:

INSTD_LOGIC;

C,D:

OUTSTD_LOGIC_VECTOR(6DOWNTO0):

0111111"

CO:

OUTSTD_LOGIC_VECTOR(3DOWNTO0));

ENDkeycode;

ARCHITECTUREyimaOFkeycodeIS

SIGNALE:

STD_LOGIC_VECTOR(3DOWNTO0);

SIGNALF:

SIGNALS,EN,EN1:

STD_LOGIC;

PROCESS(X,Y)

VARIABLExy:

STD_LOGIC_VECTOR(6DOWNTO0);

xy:

=(X&

Y);

IFXT='

CASExyIS

WHEN"

1101110"

0000"

C(6downto0)<

1101101"

0001"

0000110"

1101011"

0010"

1011011"

1100111"

0011"

1001111"

1011110"

0100"

1100110"

1011101"

0101"

0110"

1111100"

1010111"

0000111"

0111110"

1000"

1111111"

0111101"

1001"

0111011"

CO<

1010"

0110111"

ELSIFXT='

0'

F<

D(6downto0)<

键盘译码电路仿真波形图:

2.5密码控制电路模块

密码控制电路是本次课题设计的核心部分,我们通过密码控制来断定数字锁的开或关。

当密码输入时,按下确定键,输入数字和所存的密码进行比较,若相同则进入开锁状态。

若输入密码不正确则立刻进入报警状态,然后按下清零键,重新输入密码。

密码控制封装图如下:

ENTITYkongzhiIS

PORT(E_IN:

F_IN:

INSTD_LOGIC_VECTOR(3DOWNTO0);

CO_IN:

K,M:

OUTSTD_LOGIC);

ARCHITECTUREluojiOFkongzhiIS

SIGNALG,H:

STD_LOGIC_VECTOR(3DOWNTO0):

=‘0‘;

SIGNALCOUNT1,COUNT2:

STD_LOGIC:

='

SIGNALCO:

PROCESS(CO_IN)

begin

IFCO_IN="

THEN

EN1<

ELSIFCO_IN="

EN<

EN1<

if(S='

)and(en='

)and(count1='

)then

G(3downto0)<

=E_IN(3downto0);

H(3downto0)<

=F_IN(3downto0);

count1<

=not(count1);

endif;

if(en1='

)and(count2='

if(E_IN(3downto0)=G(3downto0)andF_IN(3downto0)=H(3downto0))then

k<

EN<

s<

else

m<

count2<

=not(count2);

ELSif(en='

)and(en1='

count2<

k<

ENDPROCESS;

三、调试下载

1、引脚锁定:

这个过程中特别要注意的是,在锁定引脚后必须再通过MAX+plusⅡ的编译器“Compiler”,对文件重新进行编译一次,以便将引脚信息编入下载文件中。

2、连接线路:

选择主菜单“MAX+plusⅡ”中的“Programmer”选项,改变为适合实验箱的模式,按照引脚锁定连接好线路,打开电源。

3、正式下载:

单击“Configure”按钮,向EP1K30下载配置文件,如果连接无误,将出现报告配置完成的信息提示“ConfigurationComplete”。

总框图如下:

四、心得体会

为期一周的课程设计结束了,刚开始由于对嵌入式系统不熟悉,拿到这个课题时毫无头绪,根本不知道从何处入手,并且在设计过程中遇到了很多的问题,但老师和同学的帮助下,加上自己的努力,终于逐个解决了每一个难题。

在这两周中的学习使我对EDA这门课程有了进一步的了解,使我加强了动手、思考和解决实际问题的能力。

并让我深刻的体会到,嵌入式系统的应用十分广泛,运行硬件描述语言,能很容易地设计出具有严格要求的数字锁。

在做完每一个单元模块后,都要验证它是否能够满足此单元的功能。

有时候就是按照了原理来连接,但就是不能实现预期的功能。

这就需要细心地找问题,是不是哪根线坏了,还是哪块芯片坏了或接触不好,但有时也存在原理上的错误。

在设计过程中,同时也暴露出了自身的许多不足,如自己自主解决问题的能力有所欠缺,这在以后需要更好的加强。

同时在此设计过程中还用到了MAX+PLUSⅡ等软件,我更熟悉了此软件的使用,这对以后的工作和解决实际问题都有了很好的帮助。

我感觉本次课程设计我的收获还是颇多的!

五、参考文献

1.康华光主编.电子技术基础(数字部分),高等教育出版社。

2.彭介华主编,电子技术课程设计指导,高等教育出版社。

3.张原编著,可编程逻辑器件设计及应用,机械工业出版社。

4.MAX+PLUSⅡ入门

5.刘洪喜,陆颖编著.VHDL电路设计实用教程,清华大学出版社

河南机电高等专科学校

EDA课程设计报告

设计题目:

基于CPLD的数字锁

系部:

电子通信工程系

专业:

医用电子仪器与维护

班级:

091

学生姓名:

郭呈芬

学号:

090411102

成绩: