EDA课程设计之八路彩灯控制系统Word文件下载.docx

《EDA课程设计之八路彩灯控制系统Word文件下载.docx》由会员分享,可在线阅读,更多相关《EDA课程设计之八路彩灯控制系统Word文件下载.docx(16页珍藏版)》请在冰豆网上搜索。

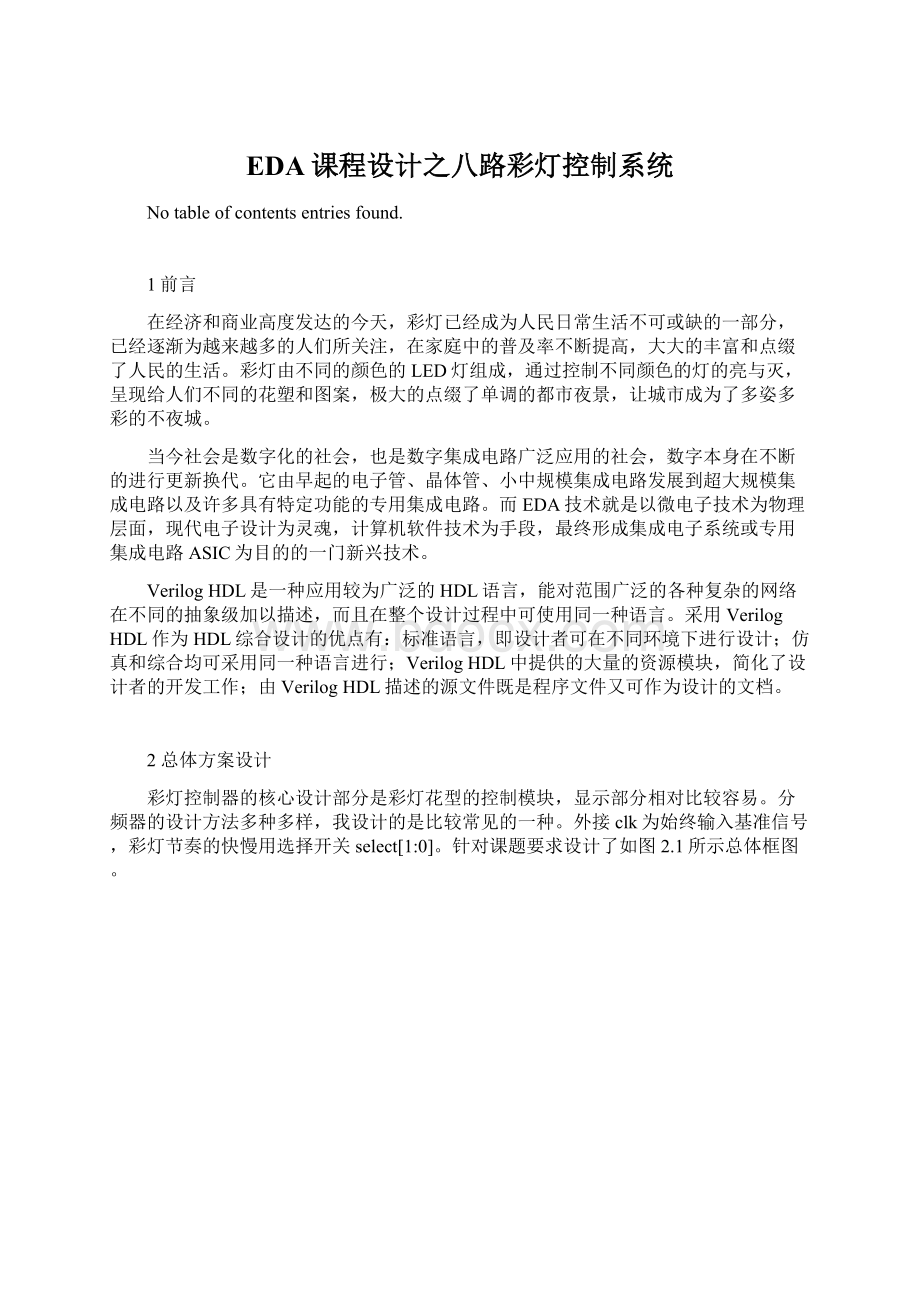

图2.3八路彩灯模块化框图

2.2方案论述

方案一与方案二最大的不同就在,前者将花型控制与节拍控制两种功能融合在一起,是考虑到只要计数器就可以实现其全部功能的原因,且原理相对简单。

这样设计,其优点在于:

设计思想比较简单。

元件种类使用少,且都较熟悉易于组装电路。

缺点则是:

中间单元电路连线过于繁多,容易出错。

且可能出现线与关系。

要避免这些,则势必造成门电路使用过多。

导致电路不稳定,抗干扰能力下降。

而后者则将以上两种功能分开设计,各单元电路只实现一种功能。

其优点在于:

电路设计模块化,易于检查电路,对后面的电路组装及电路调试带来方便。

节拍控制电路采用可编辑逻辑电路,原理相对复杂,不易理解。

花型控制电路简单,花型也比较简单。

2.3方案选择

方案一主要设计过程简单明了,而且花型控制和快慢结合在一起,用一个计数器就能而过轻松地实现功能,但是细节太多容易出错。

方案二虽然多了一个步骤,但是每个模块只完成一个功能,相对更容易上手。

所以基于以上原因,加上为了确保短时间内完成课程设计,我选择了连线少,易于调试的方案二。

3单元模块设计

3.1时钟信号模块

时钟信号控制模块的主要功能是将输出的标准时钟进行分频,以此控制八路彩灯的快慢节奏变化。

时钟信号控制在本设计中起着至关重要的作用,它以彩灯闪动快慢节奏的变化实现了八路彩灯绚丽多彩的花型节奏变化。

时钟控制是整个设计中的一个分模块,它的设计对八路彩灯控制器的顺利完成起着决定性作用。

对时钟控制程序封装如图3.1所示。

图3.1分频器模块

设计的标准时钟输入时50MHz,但是在QuartusⅡ中仿真时由于计数次数太多以至于不能正常得到分频后的波形,所以此处的仿真波形非标准时钟,仅用来表示分频的结果。

图3.2分频仿真时序图

图3.2仿真波形图中,out是对基准时钟的4分频,out1是对基准时钟的8分频,out2是对基准时钟的16分频,out3是对基准时钟的32分频。

3.2节拍快慢控制模块

节拍快慢控制模块即一个4选1数据选择器,它的功能是将分频器分出来的四个时钟信号通过我们外部输入而选择其中一个输出到下一个模块中,这样就可以控制彩灯显示的快慢。

它的真值表如表3.1所示。

表3.14选1数据选择器真值表

select[1:

0]

输出

Out1

1

Out2

Out3

Out4

4选1数据选择器仿真波形和封装模型分别如下:

图3.3数据选择模块

图3.44选1数据选择器仿真图

图3.4数据选择器仿真波形中,输入的选择信号sel是2'

b01即选择输入的第二个波形,所以输出的波形即是第二个波形。

3.3彩灯控花型控制模块

彩灯控制模块是整个设计的核心,彩灯控制模块能够进行彩灯图案的控制,它负责整个设计的输出效果即各种彩灯图案的样式变化。

在仿真时序中高电平代表灯亮,低电平代表灯灭,由高低电平按不同规律组合就代表不同的花型,同时选择不同的频率,从而实现多种图案多种频率的花样功能显示。

此时VerilgHDL硬件描述语言的优势就展现出来,使用者可以按自己的需求改变源程序从而改变显示的花型,而不用更换显示设备,这样不但经济而且环保。

程序封装图及仿真图分别如图所示。

图3.5彩灯控制系统程序封装图

图3.6彩灯控制系统功能仿真图

图3.6中,在第一个上升沿输出8个高电平即8个彩灯全亮,下一个上升沿全部为低电平表示彩灯全部熄灭。

之后隔一个时钟周期产生一个高电平,即彩灯依次点亮。

最后四个高电平和低电平相间,表示8个彩灯亮灭相间。

4软件设计

4.1QuartusⅡ简介

QuartusⅡ可编程逻辑开发软件是Altera公司为其FPGA/CPLD芯片设计的集成化专用开发工具,是Altera最新一代功能更强的集成EDA开发软件。

使用QuartusII可完成从设计输入,综合适配,仿真到下载的整个设计过程。

Max+plusⅡ是Altera公司早期的开发工具,曾经是最优秀的PLD开发平台之一,现在正在逐步被QuartusⅡ代替。

并且Max+plusⅡ已经不再支持Altera公司的新器件,同时,QuartusH也放弃了对少数较老器件的支持。

QuattusII界面友好,具有MAX+PLUSⅡ界面选项,这样MAX的老用户就无须学习新的用户界面就能够充分享用QuartusⅡ软件的优异性能。

所以,无论是初学者,还是Max+plusⅡ的老用户,都能较快的上手。

QuartusⅡ根据设计者需求提供了一个完整的多平台开发环境,它包含蕞个FPGA和CPLD设计阶段的解决方案。

QuarmsⅡ软件提供的完整,操作简易的图形用户界面可以完成整个设计流程中的各个阶段。

QuartusⅡ集成环境包括以下内容:

系统级设计,嵌入式软件开发,可编程逻辑器件(PLD)设计,综合,布局和布线,验证和仿真。

QuartusⅡ也可以直接调用SynplifyPro,LeonardoS~ctmm以及ModelSim等第三方EDA工具来完成设计任务的综合与仿真。

QualtusⅡ与MATLAB和DSPBuilder结合可以进行基于FPGA的DSP系统开发,方便且快捷,还可以与SOPCBuilder结合,实现SOPC系统的开发。

4.2QartusⅡ设计开发流程

QuanusⅡ设计的主要流程有:

创建工程、设计输入、编译、仿真验证、下载,其进行数字电路设计的一般流程如图4.1所示。

图4.1QuartusⅡ设计开发流程

设计输入:

包括原理图输入、HDL文本输入、EDIF网表输入等几种方式。

编译:

先根据设计要求设定编译方式和编译方略,如器件的选择、逻辑综合方式的选择等。

然后根据设定的参数和策略对设计项目进行网表提取,逻辑综合器件适配,并产生报告文件、延时信息文件及编程文件,供分析、仿真和编译使用。

仿真:

仿真包括功能仿真、时序仿真和定时分析,用以验证设计项目的逻辑功能和时序关系是否正确。

编程与验证:

用得到的编程文件通过编程电缆配置PLD,加入实际激励,进行在线测试。

再设计过程中,如果出现错误,则需重新回到设计输入阶段,改正错误或调整电路后重复上述过程。

5系统调试

在进行系统调试时首先要建一个项目,将我们以前设计的各个子模块工程添加到该项目中并且创建模块。

之后新建一个顶层原理图文件,将我们所创建的所有子模块添加进去,再添加相应的输入输出模块,连接好线,编译之后便可以仿真。

具体顶层文件图和仿真图如下所示。

图5.1顶层文件总线图

图5.2彩灯功能仿真图

6系统功能及指标参数

本设计主要是设计一个显示三种花型的八路彩灯控制系统。

它能够通过外部选择调节彩灯显示的快慢,也可以通过更改VerilogHDL源程序改变所要现实的花型,从而获得不同的显示效果。

本设计是基于QuartusⅡ中的EP2S15F672C3芯片,基本完成了课程设计任务书上的所有功能要求,但还是有一些不足的地方,我以后会尽量改进。

7设计总结与体会

通过本次实验的学习和实践,我对DEA这门课程有了感性的认识,并且对仿真软件QuartusII有了深刻的了解和学会运用软件建立工程仿真实验,对硬件描述语言VerilogHDL有了较为基础的了解和认识,深刻体会到该语言方面的设计在生活中应用范围之广泛。

经过本次作业,我体会到设计对设计人员的基本要求:

掌握最基本的知识并且学会灵活运用这些基本知识,大胆创新敢于实践,遵守相关的游戏规则,运用谨慎全面的逻辑思维思考问题、解决问题。

具体而言,对VHDL语言的掌握程度更加的深刻,虽不能独立的设计复杂的产品,但对整个流程有了一定的了解,为以后的工作打下了基础,积累了经验。

本次课程不仅是对基础知识的提升,更是对思维方式的扩展有了相当的帮助,我相信知识是在不断的更新,但从本课程学到的思维方式却是对以后的发展大有裨益。

最后要感谢林老师的悉心指导,课程设计中,遇到了不少问题,多亏了老师的悉心指导才能够顺利、及时地解决问题,使得课题能够顺利完成。

8参考文献

[1]夏宇闻.Verilog数字系统设计教程.北京:

航空航天大学出版社,2008.

[2]吴继华,王诚.AlteraFPGA/CPLD设计.北京:

人民邮电出版社,2005.

[3]常晓明,李媛媛.VerilogHDL工程实践入门.北京:

航空航天大学出版社,2005.

[4]常晓明.VerilogHDL实践与应用系统设计.北京:

航空航天大学出版社,2003.

[5]王金明,杨吉斌.数字系统设计与VerilogHDL.北京:

电子工业出版社.2002.

附录1总设计图及仿真图

附录2VerilogHDL源程序

分频模块程序

modulefenpin3(reset,clkin,clkout,clkout1,clkout2,clkout3);

inputreset,clkin;

outputclkout,clkout1,clkout2,clkout3;

regclkout,clkout1,clkout2,clkout3;

reg[1:

0]cnt,cnt1,cnt2,cnt3;

always@(posedgeresetorposedgeclkin)

if(reset)

begin

cnt<

=0;

clkout<

end

else

=cnt+1'

b1;

if(cnt==1)

=~clkout;

end

always@(posedgeresetorposedgeclkout)

cnt1<

clkout1<

=cnt1+1'

if(cnt1==1)

=~clkout1;

always@(posedgeresetorposedgeclkout1)

cnt2<

clkout2<

=cnt2+1'

if(cnt2==1)

=~clkout2;

always@(posedgeresetorposedgeclkout2)

cnt3<

clkout3<

=cnt3+1'

if(cnt3==1)

=~clkout3;

endmodule

数据选择器程序

modulemux4_1(out,in0,in1,in2,in3,sel);

outputout;

inputin0,in1,in2,in3;

input[1:

0]sel;

regout;

always@(in0orin1orin2orin3orsel)

case(sel)

2'

b00:

out=in0;

b01:

out=in1;

b10:

out=in2;

b11:

out=in3;

default:

out=2'

bx;

endcase

endmodule

彩灯控制程序

modulecaideng(clk,reset,z);

inputreset,clk;

outputreg[7:

0]z;

reg[5:

0]state;

parameters0='

d0,s1='

d1,s2='

d2,s3='

d3,s4='

d4,s5='

d5,s6='

d6,s7='

d7,s8='

d8,s9='

d9,s10='

d10,s11='

d11,s12='

d12,s13='

d13,s14='

d14,s15='

d15,s16='

d16,s17='

d17,s18='

d18,s19='

d19,s20='

d20,s21='

d21,s22='

d22,s23='

d23,s24='

d24,s25='

d25,s26='

d26,s27='

d27,s28='

d28,s29='

d29,s30='

d30,s31='

d31,s32='

d32,s33='

d33,s34='

d34,s35='

d35,s36='

d36,s37='

d37,s38='

d38,s39='

d39,s40='

d40,s41='

d41,

s42='

d42,s43='

d43,s44='

d44,s45='

d45,s46='

d46,s47='

d47,s48='

d48,s49='

d49,s50='

d50,s51='

d51,

s52='

d52;

always@(posedgeclk)

beginif(reset)state<

=s0;

elsecase(state)

s0:

state<

=s1;

s1:

=s2;

s2:

=s3;

s3:

=s4;

s4:

=s5;

s5:

=s6;

s6:

=s7;

s7:

=s8;

s8:

=s9;

s9:

=s10;

s10:

=s11;

s11:

=s12;

s12:

=s13;

s13:

=s14;

s14:

=s15;

s15:

=s16;

s16:

=s17;

s17:

=s18;

s18:

=s19;

s19:

=s20;

s20:

=s21;

s21:

=s22;

s22:

=s23;

s23:

=s24;

s24:

=s25;

s25:

=s26;

s26:

=s27;

s27:

=s28;

s28:

=s29;

s29:

=s30;

s30:

=s31;

s31:

=s32;

s32:

=s33;

s33:

=s34;

s34:

=s35;

s35:

=s36;

s36:

=s37;

s37:

=s38;

s38:

=s39;

s39:

=s40;

s40:

=s41;

s41:

=s42;

s42:

=s43;

s43:

=s44;

s44:

=s45;

s45:

=s46;

s46:

=s47;

s47:

=s48;

s48:

=s49;

s49:

=s50;

s50:

=s51;

s51:

=s52;

s52:

endcase

always@(state)

begincase(state)

z<

=8'

b00000000;

b11111111;

b10000000;

b01000000;

b00100000;

b00010000;

b00001000;

b00000100;

b00000010;

b00000001;

s30:

b01010101;

b10101010;

defaultz<