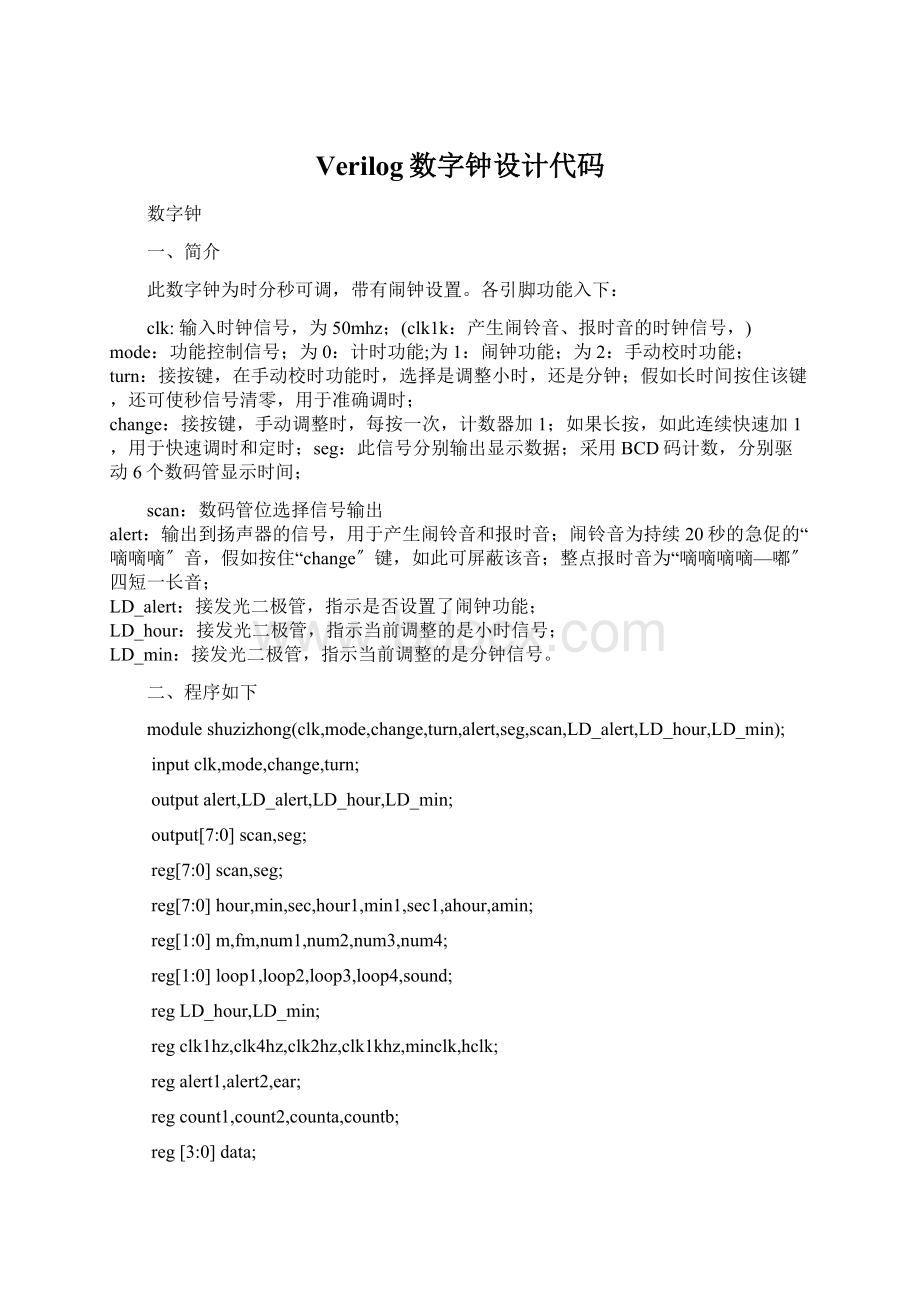

Verilog数字钟设计代码文档格式.docx

《Verilog数字钟设计代码文档格式.docx》由会员分享,可在线阅读,更多相关《Verilog数字钟设计代码文档格式.docx(10页珍藏版)》请在冰豆网上搜索。

接发光二极管,指示当前调整的是分钟信号。

二、程序如下

moduleshuzizhong(clk,mode,change,turn,alert,seg,scan,LD_alert,LD_hour,LD_min);

inputclk,mode,change,turn;

outputalert,LD_alert,LD_hour,LD_min;

output[7:

0]scan,seg;

reg[7:

0]hour,min,sec,hour1,min1,sec1,ahour,amin;

reg[1:

0]m,fm,num1,num2,num3,num4;

0]loop1,loop2,loop3,loop4,sound;

regLD_hour,LD_min;

regclk1hz,clk4hz,clk2hz,clk1khz,minclk,hclk;

regalert1,alert2,ear;

regcount1,count2,counta,countb;

reg[3:

0]data;

reg[2:

0]t8;

reg[14:

0]count3;

reg[6:

0]count4;

wirect1,ct2,cta,ctb,m_clk,h_clk;

//-------------------1khz,2hz--,1hz------------------------------------

always(posedgeclk)

begin

if(count3=='

d25000)

beginclk1khz<

=~clk1khz;

count3<

=0;

end

else

begincount3<

=count3+1'

b1;

end

always(posedgeclk1khz)//4hz

begin

if(count4=='

d125)

beginclk4hz<

=~clk4hz;

count4<

begincount4<

=count4+1'

always(posedgeclk4hz)//2hz

clk2hz<

=~clk2hz;

always(posedgeclk2hz)//1hz

clk1hz<

=~clk1hz;

//-----------------------------------------------------------

always(posedgeclk4hz)

begin

if(sound==3)

beginsound<

ear<

=1;

end

=sound+1'

end

always(negedgemode)

if(m==2)m<

elsem<

=m+1'

end

always(negedgeturn)

fm<

=~fm;

//----------------------------------------------------------------

always

case(m)

2:

beginif(fm)

begincount1<

=change;

{LD_min,LD_hour}<

=2;

else

begincounta<

{count2,countb}<

=2'

b11;

1:

beginif(fm)

begincount2<

elsebegincountb<

{count1,counta}<

default:

{count1,count2,counta,countb,LD_min,LD_hour}<

=6'

b111111;

endcase

end

always(negedgeclk4hz)

if(!

count2)

if(loop1==3)num1<

beginloop1<

=loop1+1'

num1<

end

beginloop1<

always(negedgeclk4hz)

countb)

begin

if(loop2==3)num2<

beginloop2<

=loop2+1'

num2<

end

beginloop2<

count1)

if(loop3==3)num3<

beginloop3<

=loop3+1'

num3<

beginloop3<

counta)

if(loop4==3)num4<

beginloop4<

=loop4+1'

num4<

beginloop4<

assignct1=(num3&

clk)|(!

num3&

m_clk);

assignct2=(num1&

num1&

(!

count2));

assigncta=(num4&

num4&

h_clk);

assignctb=(num2&

num2&

countb));

//-----------------------------------------------------------------------------

always(posedgeclk1hz)

(sec1^8'

h59)|(!

turn)&

m))

beginsec1<

if(!

((!

m)))

minclk<

if(sec1[3:

0]==4'

b1001)

beginsec1[3:

0]<

=4'

b0000;

sec1[7:

4]<

=sec1[7:

4]+1'

elsesec1[3:

=sec1[3:

0]+1'

minclk<

assignm_clk=minclk||(!

count1);

always(posedgect1)

if(min1==8'

h59)

beginmin1<

hclk<

if(min1[3:

0]==9)

beginmin1[3:

min1[7:

=min1[7:

elsemin1[3:

=min1[3:

assignh_clk=hclk||(!

counta);

always(posedgecta)//Ð

¡

Ê

±

¼

Æ

º

Í

Ð

µ

÷

Õ

û

½

ø

³

Ì

if(hour1==8'

h23)hour1<

if(hour1[3:

beginhour1[7:

=hour1[7:

hour1[3:

elsehour1[3:

=hour1[3:

always(posedgect2)

if(amin==8'

h59)amin<

if(amin[3:

beginamin[3:

amin[7:

=amin[7:

elseamin[3:

=amin[3:

always(posedgectb)

if(ahour==8'

h23)ahour<

elseif(ahour[3:

beginahour[3:

ahour[7:

=ahour[7:

end

elseahour[3:

=ahour[3:

//---------------------------------------------------------------------------

if((min1==amin)&

&

(hour1==ahour)&

(amin|ahour)&

(change))

if(sec1<

8'

h20)alert1<

elsealert1<

elsealert1<

always

3'

b00:

beginhour<

=hour1;

min<

=min1;

sec<

=sec1;

b01:

=ahour;

=amin;

=8'

bx;

b10:

default:

assignLD_alert=(ahour|amin)?

1'

b1:

b0;

assignalert=((alert1)?

clk1khz&

clk4hz:

b0)|alert2;

if((min1==8'

h59)&

(sec1>

h54)||(!

(min1|sec1)))

if(sec1>

h54)alert2<

=ear&

clk1khz;

elsealert2<

=!

ear&

elsealert2<

//-------------------------------------------------------------

always(posedgeclk1khz)

t8<

=t8+1'

case(t8[2:

0])

b000:

beginscan<

b01111111;

data[3:

=hour[7:

4];

b001:

b10111111;

=hour[3:

0];

b010:

b11011111;

=min[7:

b011:

b11101111;

=min[3:

b100:

b11110111;

=sec[7:

b101:

b11111011;

=sec[3:

//3'

b110:

='

b11111101;

b1011;

b111:

b11111110;

b1010;

b11111111;

endcase

case(data[3:

4'

b0000:

seg[7:

b11000000;

b0001:

b11111001;

b0010:

b10100100;

b0011:

b10110000;

b0100:

b10011001;

b0101:

b10010010;

b0110:

b10000010;

b0111:

b11111000;

b1000:

b10000000;

b1001:

b10010000;

b1010:

b10001000;

b1011:

b10000011;

b1100:

b11000110;

b1101:

b10100001;

b1110:

b10000110;

b1111:

b10001110;

endmodule

三、框图