哈工大数字电路实验报告实验一Word文件下载.docx

《哈工大数字电路实验报告实验一Word文件下载.docx》由会员分享,可在线阅读,更多相关《哈工大数字电路实验报告实验一Word文件下载.docx(10页珍藏版)》请在冰豆网上搜索。

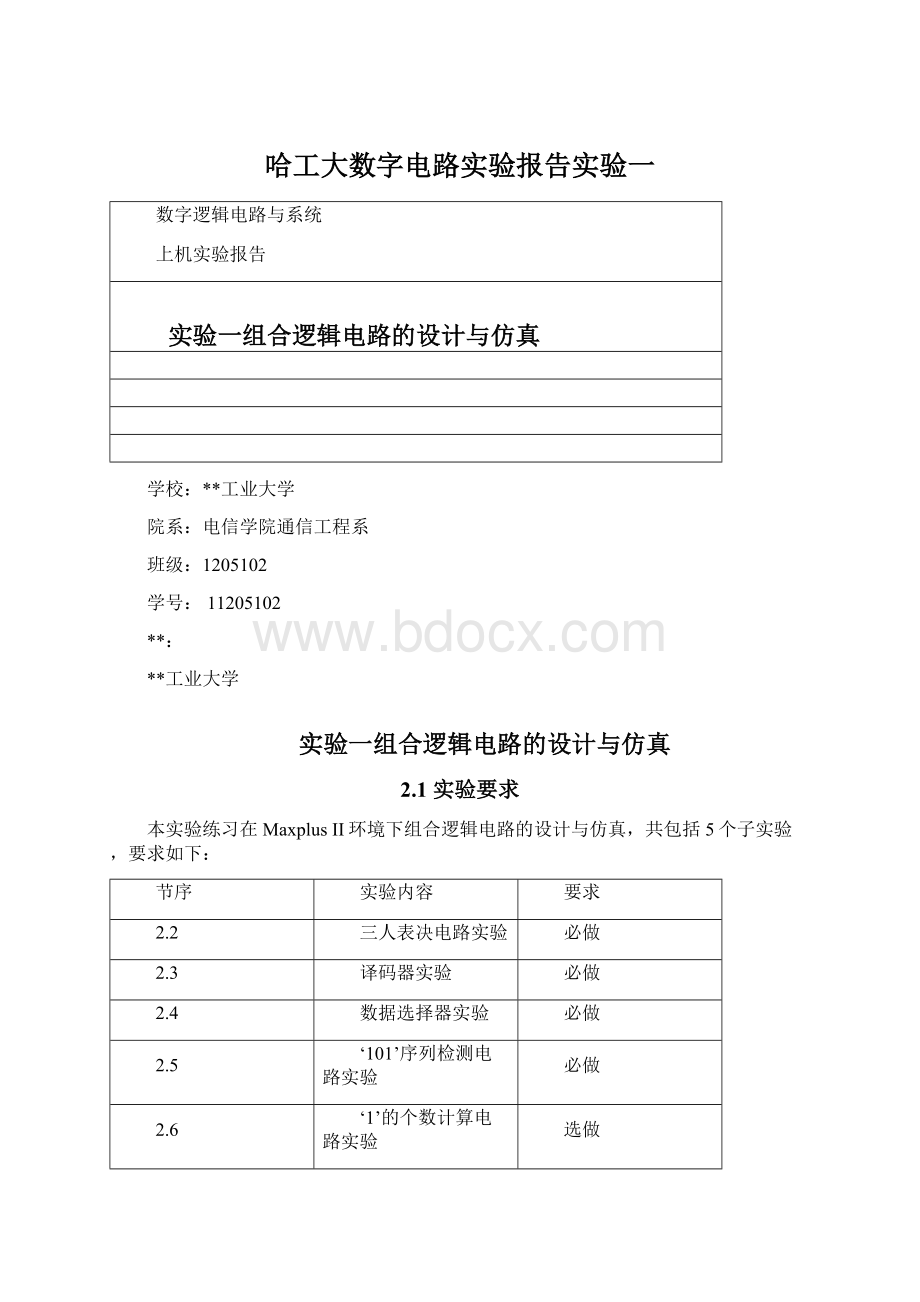

要求

2.2

三人表决电路实验

必做

2.3

译码器实验

2.4

数据选择器实验

2.5

‘101’序列检测电路实验

2.6

‘1’的个数计算电路实验

选做

2.2三人表决电路实验

2.2.1实验目的

1.熟悉MAXPLUSII原理图设计、波形仿真流程

2.练习用门电路实现给定的组合逻辑函数

2.2.2实验预习要求

1.预习教材"

第四章组合逻辑电路"

2.了解本次实验的目的、电路设计要求

2.2.3实验原理

设计三人表决电路,其原理为:

三个人对某个提案进展表决,当多数人同意时,那么提案通过,否那么提案不通过。

输入:

A、B、C,为’1’时表示同意,为’0’时表示不同意;

输出:

F,为’0’时表示提案通过,为’1’时表示提案不通过;

电路的真值表如下:

A

B

C

F

1

要求使用根本的与门、或门、非门在MAXPLUSII环境下完成电路的设计与波形仿真。

2.2.4实验步骤

1.翻开MAXPLUSII,新建一个原理图文件,命名为EXP2_2.gdf。

2.按照实验要求设计电路,将电路原理图填入下表。

三人表决电路原理图

3.新建一个波形仿真文件,命名为EXP2_2.scf,参加所有输入输出信号,并绘制输入信号A、B、C的波形〔真值表中的每种输入情况均需出现〕。

4.运行仿真器得到输出信号F的波形,将完整的仿真波形图〔包括全部输入输出信号〕附于下表。

三人表决电路仿真波形图

2.3译码器实验

2.3.1实验目的

熟悉用译码器设计组合逻辑电路,并练习将多个低位数译码器扩展为一个高位数译码器。

2.3.2实验预习要求

4-2-2译码器"

一节

2.3.3实验原理

译码器是数字电路中的一种多输入多输出的组合逻辑电路,负责将二进制码或BCD码变换成按十进制数排序的输出信息,以驱动对应装置产生合理的逻辑动作。

商品的译码器品种较多,有2-4线、3-8线、4-10线及4-16线等。

本实验练习对双2-4线译码器74LS139的扩展,并用其实现特定的组合逻辑。

74LS139包含两个2-4线译码器,其输入输出如下:

输

入

A1,B1

译码器1的地址输入

G1N

译码器1的使能

A2,B2

译码器2的地址输入

G2N

译码器2的使能

出

Y10N,Y11N,Y12N,Y13N

译码器1的输出端

Y20N,Y21N,Y22N,Y23N

译码器2的输出端

74LS139中译码器1真值表如下:

输入

输出

B1

A1

Y13N

Y12N

Y11N

Y10N

--

74LS139中译码器2真值表如下:

B2

A2

Y23N

Y21N

Y20N

要求使用两片74LS139实现逻辑函数

,在MAXPLUSII环境下完成电路的设计与波形仿真。

2.3.4实验步骤

1.翻开MAXPLUSII,新建一个原理图文件,命名为EXP2_3.gdf。

译码器实现逻辑函数原理图

3.新建一个波形仿真文件,命名为EXP2_3.scf,参加所有输入输出信号,并绘制输入信号A、B、C、D的波形〔每种输入情况均需出现〕。

译码器实现逻辑函数仿真波形图

2.4数据选择器实验

2.4.1实验目的

熟悉用数据选择器设计组合逻辑电路,并练习将多个低位数数据选择器扩展为一个高位数数据选择器。

2.4.2实验预习要求

4-3-1数据选择器"

2.4.3实验原理

数据选择器是一种能从多路平行输入数据中,选择1路作为输出信号的电路,是又一类重要的组合功能电路。

本实验练习对双2-4线译码器74LS153的扩展,并用其实现特定的组合逻辑。

74LS153包含两个2-4线译码器,其输入输出如下:

A,B

数据选择端口

1GN

数据选择器1的使能

1C0,1C1,1C0,1C3

数据选择器1的输入数据

2GN

数据选择器2的使能

2C0,2C1,2C0,2C3

数据选择器2的输入数据

1Y

数据选择器1的输出

2Y

数据选择器2的输出

74LS153的真值表如下:

数据选择端

输入端

输出端

GN

C3

C2

C1

C0

Y

要求使用两片74LS153实现逻辑函数

2.4.4实验步骤

1.翻开MAXPLUSII,新建一个原理图文件,命名为EXP2_4.gdf。

数据选择器实现逻辑函数原理图

3.新建一个波形仿真文件,命名为EXP2_4.scf,参加所有输入输出信号,并绘制输入信号A、B、C、D的波形〔每种输入情况均需出现〕。

数据选择器实现逻辑函数仿真波形图

2.5‘101’序列检测电路实验

2.5.1实验目的

练习灵活运用中规模集成功能组件及根本逻辑门实现功能较复杂的组合逻辑电路。

2.5.2实验预习要求

4-6组合电路的设计"

2.5.3实验原理

设计一个组合逻辑电路,其输入为六位二进制数X5,X4,X3,X2,X1,X0,输出为三位二进制数Y2,Y1,Y0,如以下图所示。

电路的功能为:

在六位输入数据中寻找连续三个比特为’101’的串,输出首个’101’出现的位置(最低位’1’所在的序号);

假设输入序列中不包含’101’,那么输出端全部置1。

例如:

输入为001010时,’101’出现在X3,X2,X1的位置,故输出为001(X1的序号);

输入为101010时,首个’101’出现在X5,X4,X3的位置,故输出为011(X3的序号);

输入为100110时,不包含’101’,此时输出111。

可选用编码器(74LS148)、译码器(74LS139)、数据选择器(74LS153)配适宜当的门电路完成设计。

2.5.4实验步骤

1.翻开MAXPLUSII,新建一个原理图文件,命名为EXP2_5.gdf。

‘101’序列检测电路原理图

3.新建一个波形仿真文件,命名为EXP2_5.scf,参加所有输入输出信号,并绘制输入信号X0-X5的波形〔至少包含001010,101010,100110三种情况〕。

4.运行仿真器得到输出信号Y2,Y1,Y0的波形,将完整的仿真波形图〔包括全部输入输出信号〕附于下表。

‘101’序列检测电路仿真波形图

2.6实验的心得体会

在这次上机实验中,我学到了很多。

特别是是学习和掌握了MAXPLUSII这一软件,这使我知道了在今后的数字电路学习的过程中,如何将理论课上所学的知识运用在仿真实验中,并使之能得到验证。

此外,我还意识到做仿真实验时要多动脑,选出最好的方法,一件事往往有多种解决方法,一个好的方法,不仅能使事情事半功倍,而且往往决定最后的成与败;

还要注意细节,细节决定成败,这句话在这次上机实验中得到了充分的印证。

最后,通过这次上机实验,我复习了很多有关数电组合逻辑电路和时序逻辑电路方面的知识,对数字电路的根本原理有了更深入的了解,复习了根底知识。