VHDL设计方案多功能数字钟文档格式.docx

《VHDL设计方案多功能数字钟文档格式.docx》由会员分享,可在线阅读,更多相关《VHDL设计方案多功能数字钟文档格式.docx(22页珍藏版)》请在冰豆网上搜索。

begin

ifclk_in'

eventandclk_in='

1'

then

cou<

=cou+1。

endif。

endprocess。

process(cou)

clk_out<

=cou(21)。

endarchitecturebehivor。

完成4Mhz到1hz的转换

仿真结果略。

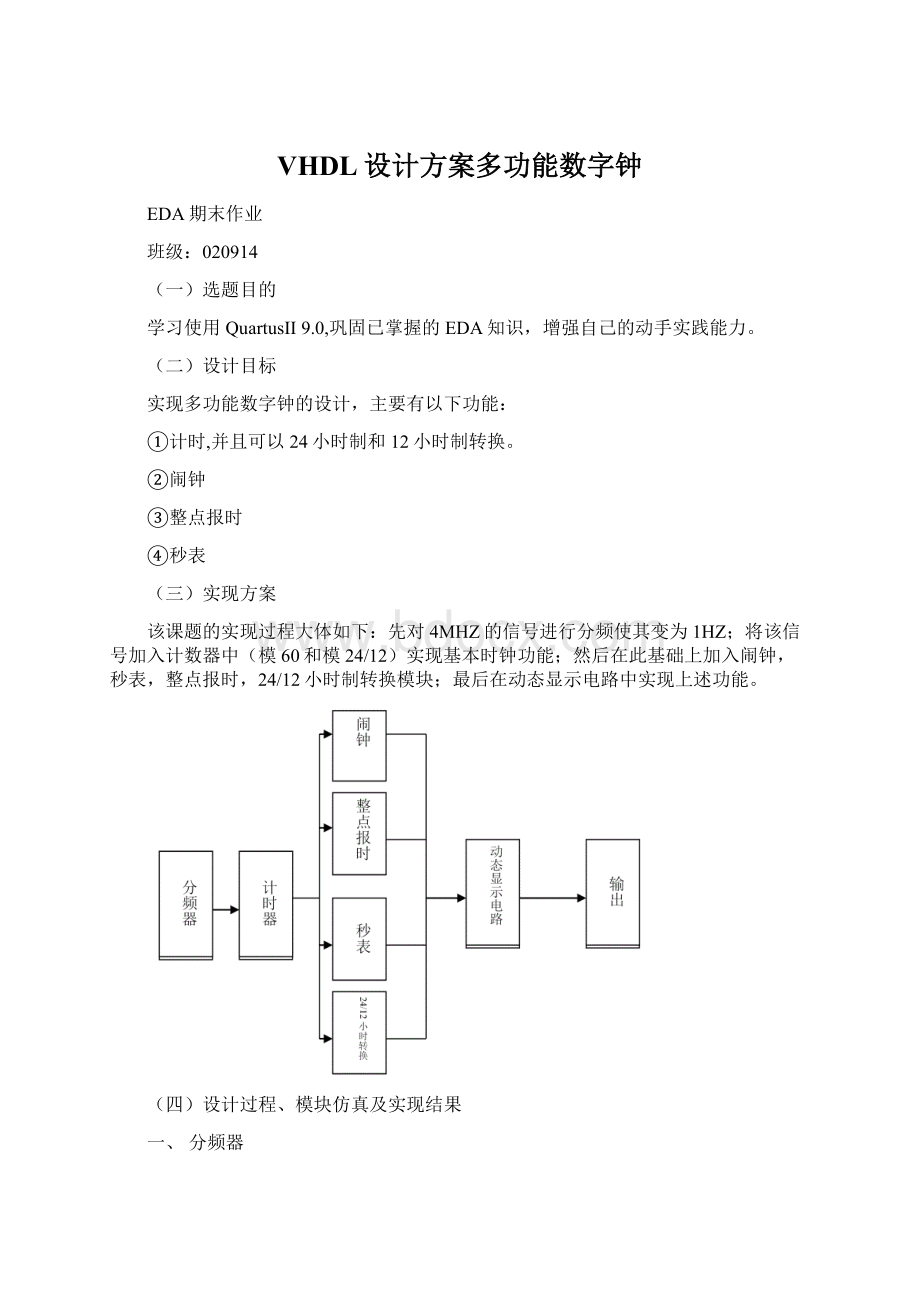

二、计时器(模60,模24,模12)

模60设计的电路图如下

模24/12计数器如下

合成模块分别如下

仿真波形如下

M60

波形分析:

ql[3..0]从0变到9,qh[3..0]从0变到5,当clk经过60个周期后,co输出一个脉冲。

从而实现模60计数器的功能。

M24/12

模12计数器(sv6=0)

模24计数器(sv6=1)

由于要进行24/12小时制的转换,所以加入开关sv6来控制转换模24和模12计数器。

由波形图可以看出,模24和模12功能均已实现。

计时器总电路为

三、动态显示功能

1、由sv3和sv8来控制转换正常计数器、闹钟、秒表的转换。

当sv3=0、sv8=0时,显示正常计时器;

当sv3=0、sv8=1时,显示秒表;

当sv3=1时,显示闹钟。

实现此功能的VHDL语言如下:

entitymandis

sv3,sv8:

sl,sh,ml,mh,hl,hh,ap,d,rsl,rsh,rml,rmh,rhl,rhh,rap,rd,swa,swb,swc,swd:

instd_logic_vector(3downto0)。

asl,ash,aml,amh,ahl,ahh,aap,ad:

outstd_logic_vector(3downto0)

)。

endmand。

architecturearcofmandis

signaltmp:

std_logic_vector(3downto0)。

process(sv3)

if(sv3='

0'

)then

ifsv8='

then

asl<

=sl。

ash<

=sh。

aml<

=ml。

amh<

=mh。

ahl<

=hl。

ahh<

=hh。

aap<

=ap。

ad<

=d。

else

=swa。

=swb。

=swc。

=swd。

="

1010"

。

0000"

endif。

=rsl。

=rsh。

=rml。

=rmh。

=rhl。

=rhh。

=rap。

=rd。

if(rap="

0010"

andrhh="

andrhl="

ahh<

0001"

ahl<

endarc。

2、数据选择器VHDL语言描述如下:

entitychsis

clk:

sl,sh,ml,mh,hl,hh,ap,d:

data:

outstd_logic_vector(3downto0)。

en:

outstd_logic_vector(7downto0)

endchs。

architecturearcofchsis

signaltt:

std_logic_vector(2downto0)。

signalt:

integerrange0to30000。

process(clk)

if(clk'

eventandclk='

t<

=t+1。

ift=30000thentt<

=tt+1。

casettis

when"

000"

=>

data<

en<

11111110"

001"

11111101"

010"

11111011"

011"

11110111"

100"

11101111"

101"

11011111"

110"

=ap+10。

10111111"

111"

01111111"

endcase。

endarc。

3、译码显示器的VHDL语言如下:

entityseg7is

port(a:

f:

outstd_logic_vector(6downto0))。

endseg7。

architecturearcofseg7is

process(a)

begin

caseais

when"

f<

1000000"

1111001"

0100100"

0011"

0110000"

0100"

0011001"

0101"

0010010"

0110"

0000010"

0111"

1111000"

1000"

0000000"

1001"

0010000"

0111111"

1011"

0001000"

1100"

0001100"

whenothers=>

合成模块分别为mand、chs、seg7

总电路合成图为

四、校分校时电路

设计电路如下:

电路分析:

为了保证时钟同步性,时钟的选取依然为1hz,所以o[3..0]均为1hz,o[0]为所采取出正常频率,o[1]为校分频率,o[2]为校时频率,o[3]为校天频率(星期)。

电路中的四个D触发器是简易的防颤抖装置,保证o[3..0]的正常输出。

Sv1和sv2是整个电路功能的控制器。

当sv1sv2=00时,计数器正常工作;

当sv1sv2=10时,进行校分工作;

当sv1sv2=01时,进行校时工作;

当sv1sv2=11时,进行校天工作。

在进行这些工作时,秒钟都停止。

合成模块为setclock

仿真波形如下:

五、整点报时功能

VHDL语言:

entitycallis

okhz,tkhz:

mh,ml,sh,sl:

y1:

outstd_logic

endcall。

architecturearcofcallis

process(okhz,tkhz,mh,ml,sh,sl)

if(mh="

andml="

andsh="

caseslis

y1<

=okhz。

=tkhz。

whenothers=>

='

endarc。

合成模块如下:

其中okhz代表频率为1khz的信号(由4K分频器获得),tkhz代表频率为2khz的信号(由2khz分频器获得)。

仿真结果为:

当分钟为“59”,秒钟的高位是“5”时,秒钟的低位为“2”、“4”、6”、”8”时,输出y1为低频信号;

当秒钟的低位为“9”时,输出为高频信号。

从而实现整点报时功能。

六、闹钟功能

电路图如下

电路说明:

由于闹钟只需要设置分钟、小时,所以分钟、始终为正常计数器,采用原来校分校时的方法来设定闹钟时间。

这里用sv3和sv4构成一个2—4译码器来控制校准的对象。

当sv3=0,sv4=0时,停止校准,分钟,时钟保持数字不变;

当sv3=1,sv4=0时,校准分钟,时钟不变;

当sv3=0,sv4=1时,校准时钟,分钟不变。

在闹钟功能中,由于用不到秒钟,所以秒钟始终显示“—”(BCD码表示为1010,)故上图中的ringsec模块就是实现秒钟置“—”功能,其VHDL语言为:

entityringsecis

en:

rsl,rsh:

endringsec。

architecturearcofringsecis

process(en)

if(en='

)then

rsl<

rsh<

合成模块如上图所示(ringsec)。

为了实现闹钟功能,我们还要设计一个比较模块,当计时器与闹钟的时钟、分钟都相等的时候给蜂鸣器一个信号,使其发声。

其VHDL语言如下:

entitycmpis

ml,mh,hl,hh,o,rml,rmh,rhl,rhh,ro:

instd_logic_vector(3downto0)。

r:

endcmp。

architecturearcofcmpis

process(clk)

if(ml=rmlandmh=rmhandhl=rhlandhh=rhh)thenr<

=clk。

elser<

endprocess。

合成模块为cmp:

波形为

由波形可见,当计时器与闹钟的时钟、分钟都相等的时候,输出r会有一个信号。

七、秒表功能

设计电路图如下

合成模块为stw:

八、24小时制转12小时制功能

用一个sv6开关来控制24小时制和12小时制。

当sv6=0时为12小时制;

当sv6=1时为24小时制。

1、24小时制转12小时制的模块(chg)

entitychgis

sv6:

hh,hl,ap:

chh,chl,cap:

endchg。

architecturearcofchgis

process(sv6,hh,hl,ap)

if(sv6='

)then——原来是24小时制,sv6变为0,需要进行24转12的工作

casehhis

chh<

chl<

cap<

——小时高位为0时不需要变化,只需再显示一个“A”,即cap=”0001”

ifhl<

"

thenchh<

cap<

elsechh<

=hl-2。

——12以下数字不变,显示“A”,13~19小时高位变0,低位减2,显示“P”

=>

thenchl<

=hl+8。

chh<

——20~21点的变化

elsechl<

——22~23点的变化

null。

else——原来是12小时制,sv6变为1,需要进行12转24的工作

ifap="

——AM的转换,数字都不变,只是不显示“A”,显示“—”

then

thenchh<

=hh+1。

=hl+2。

——下午1~8点的转换

=hl-8。

=hh+2。

——下午8~11点的转换

——换成24小时制后,原来现实A、P的管显示“—”

2、当变化sv6时,还要对原来计时器的电路(包括闹钟中的计时电路)中的小时位进行摸12和摸60的转换。

转换电路如下(newm24):

其中左上角的dmc模块是作为数据选择器74157控制信号发声器(即单脉冲发声器),其内部电路如下所示(dmc)

Newm24模块合成为

Newm24和dmc的仿真结果如下:

Newm24电路说明:

为了能在拨动开关sv6的同时进行模24模12转换,必须在开关拨动的同时使其能产生一个时间长度大于计时器一个周期,不大于其两个周期的单脉冲信号,从而保证在计时器时钟边沿到来时,能将chg所产生的转换信号置数到计数器。

(上图中的chh[3..0]和chl[3..0]为上述VHDL语言所编程序中的输出信号)。

当sv6发生变化时,dmc会产生一个值为0的单脉冲,置数端信号为0,计数器将chh[3..0]、chl[3..0]分别置入计时器时钟的十位和个位;

当sv6不变时,数据选择器选择的数均为“0000”,计数器正常计数至11或23时发生置数,正常计数。

合成后的总电路图为

开关对应功能表

Sv1、sv2

当sv1sv2=11时,进行校天工作

Sv3、sv8

由sv3和sv8来控制转换正常计数器、闹钟、秒表的转换。

当sv3=1时,显示闹钟

Sv5

控制秒表

Sv3、sv4

sv3和sv4构成一个2—4译码器来控制校准的对象。

当sv3=0,sv4=1时,校准时钟,分钟不变

Sv6

当sv6=1时为24小时制

(五)遇到的困难

各个模块之间的链接修改了很多次,提前没有整体构思好,单个模块设计好以后总是会在模块间的组合上出现接口不对应的情况。

在24/12小时制模块chg的设计中,不同的时间转换考虑的不周全(例如下午1~7点和下午8~11点的变化不一样)

自己对知识的掌握还是不够好,有许多模块设计了很长的时间(无论是构思还是具体编程)。

(六)对课程的建议

EDA课程上完以后,我感觉这门课程实际应用很强。

非常锻炼动手能力,与其他的课程很不一样。

希望学校增加该课的课时。