太原理工现代科技电子钟课程设计Word格式.docx

《太原理工现代科技电子钟课程设计Word格式.docx》由会员分享,可在线阅读,更多相关《太原理工现代科技电子钟课程设计Word格式.docx(40页珍藏版)》请在冰豆网上搜索。

学生提交

归档文件

课程设计说明书,主要包括以下内容:

(1)设计方案,系统框图,原理分析;

(2)系统各模块的VHDL源程序;

(3)综合、编程部分,包括各模块的综合结果、仿真分析,系统管脚定义,下载验证结果;

(4)设计总结部分,指出设计系统的特点及选用方案优缺点,提出改进意见及展望,总结设计收获、体会;

(5)参考文献。

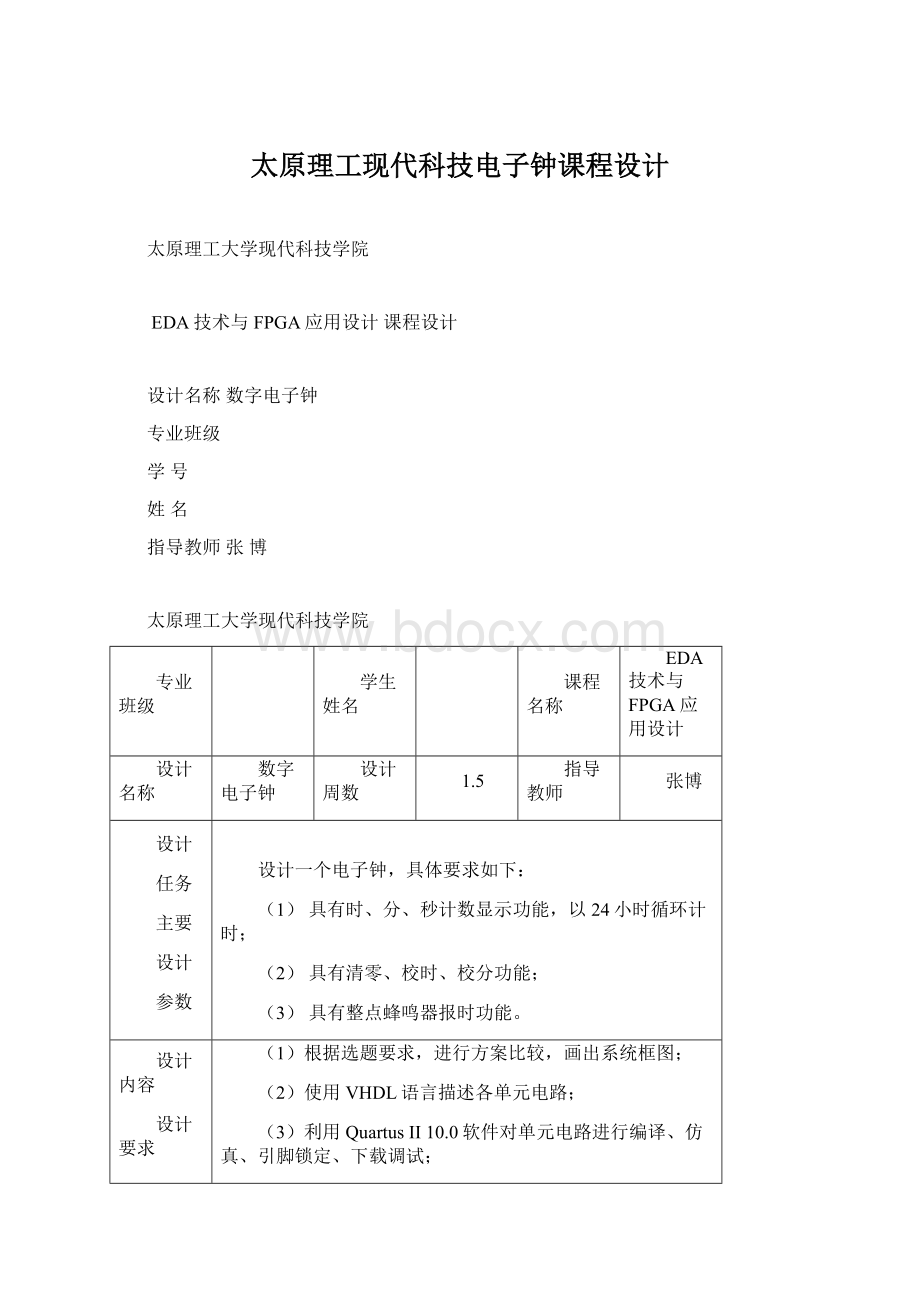

课程设计任务书

注:

1.课程设计完成后,学生提交的归档文件应按照:

封面—任务书—说明书—图纸的顺序进行装订上交(大张图纸不必装订)

2.可根据实际内容需要续表,但应保持原格式不变。

指导教师签名:

日期:

2016.06.08

……………………………………装………………………………………订…………………………………………线………………………………………

专业班级学号姓名成绩

数字电子钟

一、设计名称:

数字电子钟的实现

二、设计要求:

三、设计内容:

四、CPLD介绍:

(1)FPGA(Field-ProgrammableGateArray),即现场可编程门阵列,它是在PAL、GAL、CPLD等可编程器件的基础上进一步发展的产物。

它是作为专用集成电路(ASIC)领域中的一种半定制电路而出现的,既解决了定制电路的不足,又克服了原有可编程器件门电路数有限的缺点。

FPGA采用了逻辑单元阵列LCA(LogicCellArray)这样一个概念,内部包括可配置逻辑模块CLB(ConfigurableLogicBlock)、输出输入模块IOB(InputOutputBlock)和内部连线(Interconnect)三个部分。

现场可编程门阵列(FPGA)是可编程器件。

与传统逻辑电路和门阵列(如PAL,GAL及CPLD器件)相比,FPGA具有不同的结构,FPGA利用小型查找表16×

1RAM)来实现组合逻辑,每个查找表连接到一个D触发器的输入端,触发器再来驱动其他逻辑电路或驱动I/O,由此构成了既可实现组合逻辑功能又可实现时序逻辑功能的基本逻辑单元模块,这些模块间利用金属连线互相连接或连接到I/O模块。

FPGA的逻辑是通过向内部静态存储单元加载编程数据来实现的,存储在存储器单元中的值决定了逻辑单元的逻辑功能以及各模块之间或模块与I/O间的联接方式,并最终决定了FPGA所能实现的功能,FPGA允许无限次的编程。

5、电子钟总体设计方案:

本时钟系统主要由分频器、计数、译码、显示、校时以及闹钟等功能。

由于分频器从50MHZ晶振中得到1HZ信号给计数器提供标准时钟,译码器将计数器数据译码数码管能显示的信号,显示模块扫描译码器数据并显示。

由于计数的起始时间不可能与标准时间一致,所以需要加入一个分频程序。

1.分频程序

先后采用过两种方式:

(1)signalcount:

integer;

--分频内部时钟

process(clk)--分频程序

begin

if(clk'

eventandclk='

1'

)then

if(count=N-1)then

count<

=conv_integer('

0'

);

else

=count+1;

ifcount<

(integer(N/2))then

clk1<

='

;

else

endif;

endif;

endprocess;

这种分频程序可调,但是应用于开发板写入之后发现计数器在十几秒内无响应,十几秒之后正常计数,所以采用了进位时钟,见第二个。

(2)signalcnt:

std_logic_vector(25downto0);

process(rst,clk)

begin

ifrst='

then

cnt<

=(others=>

'

elsifclk'

=cnt+1;

endif;

clk1<

=cnt(24);

这个是应用于分频的分频程序模块,测试结果良好。

此分频没有严格分频至1秒种,要求严格可以进一步深入编辑。

2.计数模块

signalsz_h,sz_l:

std_logic_vector(3downto0);

--内部小时BCD

signalfz_h,fz_l:

--内部分钟BCD

signalmz_h,mz_l:

--内部秒钟BCD

signalgongneng:

std_logic_vector(2downto0);

--功能控制

process(clk1,gongneng,rst)--秒针BCD

ifrst='

then--复位有效

mz_h<

="

0000"

mz_l<

elsifkz_1='

then--调整秒针低位控制按钮

mz_l<

=a;

elsifkz_2='

then--调整秒针高位控制按钮

mz_h<

elsif(gongneng="

000"

and(clk1'

eventandclk1='

))then

ifmz_l=9then

ifmz_h=5then

=mz_h+1;

else

=mz_l+1;

以上一部分为秒针的计数器模块,通过IF嵌套将复位信号、秒针计数、及置位模块并入同一进程,因为信号不能不在多个进程被赋值,所以只能集成如同一进程。

process(clk1,gongneng,rst)--分针BCD

fz_h<

fz_l<

elsifkz_3='

then--分钟低位置数

fz_l<

elsifkz_4='

then--分钟高位置数

fz_h<

elsifgongneng="

ifclk1'

then

if(mz_l=9andmz_h=5)then

iffz_l=9then

iffz_h=5then

=fz_h+1;

=fz_l+1;

process(clk1,gongneng,rst)--时针BCD

then--复位控制

sz_h<

sz_l<

elsifkz_5='

then--时针低位控制

sz_l<

elsifkz_6='

then--时针高位控制

sz_h<

if(fz_l=9andfz_h=5andmz_l=9andfz_h=5)then

if(sz_h=2andsz_l=3)then

elsifsz_l=9then

=sz_h+1;

=sz_l+1;

以上一部分为分和时的计数器模块,通过IF嵌套将复位信号、分(时)计数、及置位模块并入同一进程,因为信号不能不在多个进程被赋值,所以只能集成如同一进程。

Gongneng为正常计时有效信号。

3.显示译码模块

通用形式为:

process(mz_h)--秒针高位显示

casemz_his

when"

=>

miao_h<

1000000"

0001"

1111001"

0010"

0100100"

0011"

0110000"

0100"

0011001"

0101"

0010010"

0110"

0000010"

0111"

1111000"

1000"

0000000"

1001"

0010000"

whenothers=>

null;

endcase;

因为实验箱电路板提供的是共阳数码管,所以为低位有效,将进程中的敏感信号切换即可显示各模块的时间显示。

4.功能调整模块

jz_0:

instd_logic;

--校正开关

signalgn:

--内部功能计数

--功能控制计数以便拓展

--这里只用到1为调位,0

process(jz_0)--功能计数

if(jz_0'

eventandjz_0='

)then

ifgn="

001"

then--此处可选功能增加或减少功能

gn<

=gn+1;

gongneng<

=gn;

以上为功能调整模块,例如本例中想通过000控制正常计数,而001时停止计数,开始调整,此处选择001返回000是因为校时分秒采用了单独的置位开关,所以功能只有停止和计数两种模式。

在附录中提供集成功能控制的校时程序。

5.校正时间输入调整模块

clk_tz:

--单独的时间调整按钮

process(clk_tz,gongneng)--校正时间调整

ifgongneng="

ifclk_tz'

eventandclk_tz='

then

ifa=9then

a<

else

=a+1;

endif;

此段程序虽然可以实现置数校时,但是例如分秒高位最高只有5所以改进程序如下:

process(clk_tz)

ifgongneng/="

ifkz_1='

orkz_3='

orkz_5='

then

ifkz_2='

orkz_4='

ifa>

=5then

ifkz_6='

ifsz_l>

4anda=1then

elsifa>

2then

这样就不会出现调整高位时间溢出的问题。

6.在实验过程中还加入了便于观察和研究的校时单独显示模块。

process(gongneng,a)--调整显示

ifgongneng="

then--正常计数时校时显示不显示

ts_xs<

1111111"

;

else

caseais

ts_xs<

7.整点报时

signalb:

--控制闪烁时间

process(gongneng,clk1,fz_l,fz_h,mz_h,mz_l)--蜂鸣器(灯光代替)

ifb=5then

b<

baoshi<

elsif(clk1'

if(gongneng="

andfz_l=9andfz_h=5andmz_l=9andmz_h=5)then

b<

baoshi<

=b+1;

此程序选择灯光亮5秒即可,具体亮闪时间可由自己调整决定,程序中if语句中有时分高低位加功能控制一共5个满足才灯光亮,实际测试中发现偶尔会出现部分整点不亮灯光,仔细判断发现是if语句中判断先后问题引起的,目前没有找到较好的解决办法。

8.按键消抖程序

signalcount:

integerrange0to3;

signaljz_0_0:

std_logic;

process(clk1)

begin

if(clk1'

)then--

if(jz_0='

)then--

if(count=3)then

count<

=count;

--

elsecount<

--

if(count=2)then

cp<

elsecp<

=0;

jz_0_0<

=cp;

这个主要是缓解调时及功能选择时按键抖动的问题,在实际的应用中相当重要。

6、设计电子钟完整程序

这段程序为便于调查观察各部分功能的程序,精简后的完整程序见附录。

libraryieee;

useieee.std_logic_1164.all;

useieee.std_logic_unsigned.all;

useieee.std_logic_arith.all;

entitydianzizhongis

GENERIC(N:

integer:

=50000000);

--N为分频数

port

(rst:

--复位按钮

clk_tz:

--功能调整时分秒按钮

jz_0:

--校正开关(JZ=1时校时)

kz_1:

--校正秒低位开关

kz_2:

--校正秒高位开关

kz_3:

--校正分低位开关

kz_4:

--校正分高位开关

kz_5:

--校正时低位开关

kz_6:

--校正时高位开关

clk:

instd_logic;

--输入时钟50MHz

shi_h:

outstd_logic_vector(6downto0);

--时高位

shi_l:

--时低位

fen_h:

--分高位

fen_l:

--分低位

miao_h:

--秒高位

miao_l:

--秒低位

ts_xs:

--调整时钟时显示(便于观察)

baoshi:

outstd_logic--报时灯光(没有蜂鸣器用灯光代替)

);

enddianzizhong;

architecturedzzofdianzizhongis

signalclk1:

--分频后时钟

--这里只用到1为调位,0为计数

signalcount:

--分频内部时钟

signala:

std_logic_vector(3downto0);

--校时显示端

--控制报时灯时间

process(clk_tz)--校正时间调整

process(rst,clk)--分频程序

ifmz_l=9