触发器时序逻辑电路习题答案电子教案Word文件下载.docx

《触发器时序逻辑电路习题答案电子教案Word文件下载.docx》由会员分享,可在线阅读,更多相关《触发器时序逻辑电路习题答案电子教案Word文件下载.docx(10页珍藏版)》请在冰豆网上搜索。

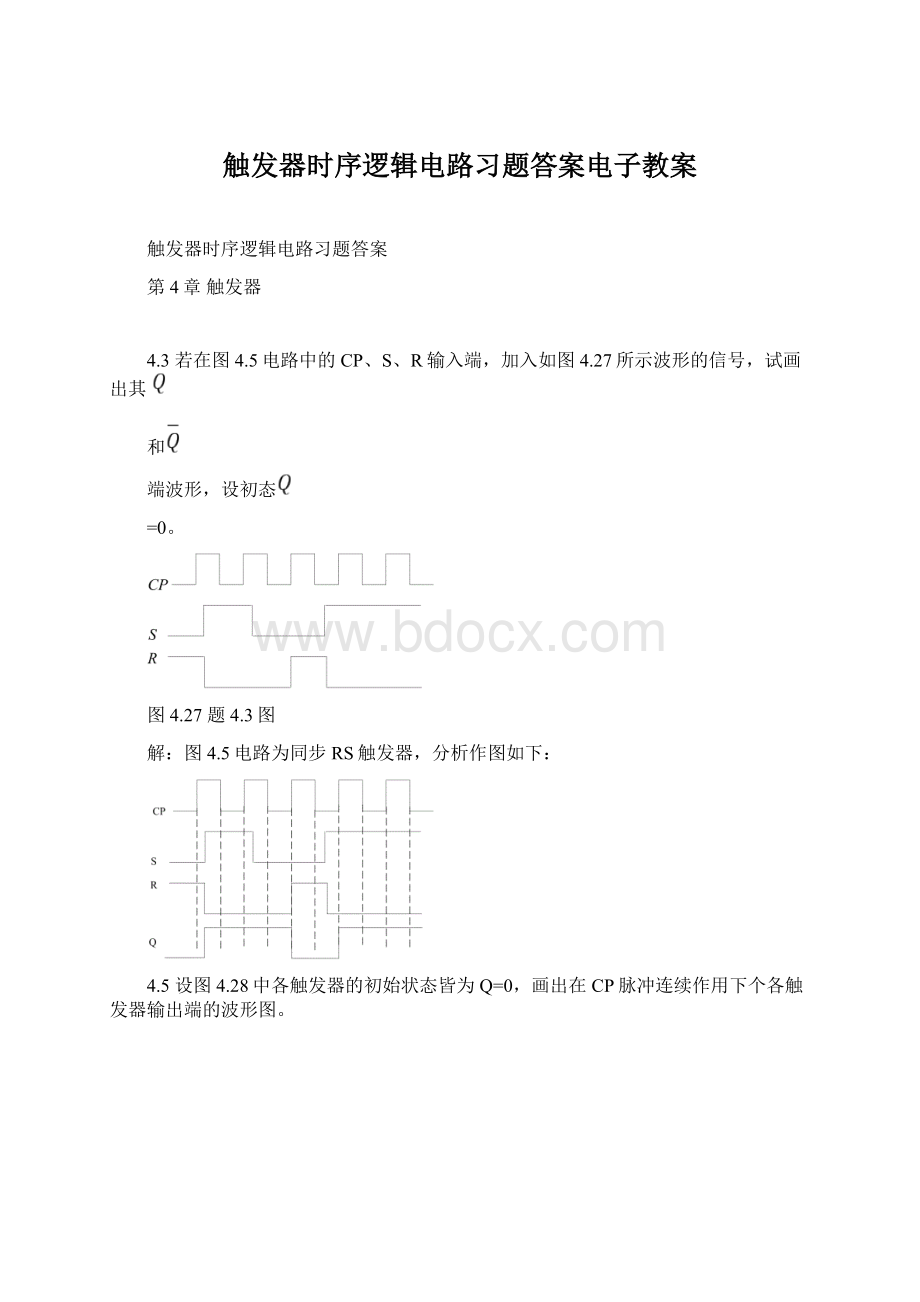

图4.5电路为同步RS触发器,分析作图如下:

4.5设图4.28中各触发器的初始状态皆为Q=0,画出在CP脉冲连续作用下个各触发器输出端的波形图。

图4.28题4.5图

4.6试写出图4.29(a)中各触发器的次态函数(即Q1n+1、Q2n+1与现态和输入变量之间的函数式),并画出在图4.29(b)给定信号的作用下Q1、Q2的波形。

假定各触发器的初始状态均为Q=0。

图4.29题4.6图

由图可见:

4.7图4.30(a)、(b)分别示出了触发器和逻辑门构成的脉冲分频电路,CP脉冲如图4.30(c)所示,设各触发器的初始状态均为0。

(1)试画出图(a)中的Q1、Q2和F的波形。

(2)试画出图(b)中的Q3、Q4和Y的波形。

图4.30题4.7图

(a)

R2=Q1低电平有效

(b)

CP3=CP上降沿触发CP4=CP下降沿触发

4.8电路如图4.31所示,设各触发器的初始状态均为0。

已知CP和A的波形,试分别画出Q1、Q2的波形。

图4.31题4.8图

由图可见

4.9电路如图4.32所示,设各触发器的初始状态均为0。

已知CP1、CP2的波形如图示,试分别画出Q1、Q2的波形。

图4.32题4.9图

第5章时序逻辑电路

5.1分析图5.39时序电路的逻辑功能,写出电路的驱动方程、状态方程,设各触发器的初始状态为0,画出电路的状态转换图,说明电路能否自启动。

图5.39题5.1图

驱动方程:

J0=K0=1,J1=K1=Q0,J2=K2=Q0Q1

状态方程:

,

状态转换图:

功能:

同步三位二进制加法计数器,可自启动。

5.5用JK触发器和门电路设计满足图5.43所示要求的两相脉冲发生电路。

图5.43题5.5图

解:

分析所给波形,可分为4个状态,00、01、11、01、00,由于有2个状态相同但次态不同,在实现途径上采用设计一个4进制计数器,再通过译码实现。

计数器采用同步二进制加法计数器,其状态方程如下:

采用JK触发器,把上述状态方程与其特性方程比较系数,可见J0=K0=1,J1=K1=Q0,设计电路如下:

分析图示电路,可得其工作波形如下所示,可见满足题目要求。

5.6试用双向移位寄存器74194构成6位扭环计数器。

解:

作状态转换图如下:

用74194实现,首先扩展成8位移位寄存器;

其次反馈形成扭环形计数器;

解决启动的方法可采用清零或者置数法。

此处采用清零法。

5.7由74290构成的计数器如图5.44所示,分析它们各为几进制计数器。

图5.44题5.7图

CP1=CP,S91=S92=0,R01=R02=Q3。

电路的基本连接形式是5进制计数器,采用反馈清零法形成4进制计数器。

其状态转换图如下:

CP1=CP,S91=S92=0,R01=Q1,R02=Q2。

电路的基本连接形式是5进制计数器,采用反馈清零法形成3进制计数器。

CP0=CP,CP1=Q0,S91=S92=0,R01=R02=Q3。

电路的基本连接形式是10进制计数器,采用反馈清零法形成8进制计数器。

CP0=CP,CP1=Q0,S91=S92=0,R01=Q0,R02=Q3。

电路的基本连接形式是10进制计数器,采用反馈清零法形成9进制计数器。

5.8试画出图5.45所示电路的完整状态换图。

图5.45题5.8图

EP=ET=1,RD=1,LD=Q2,DCBA=Q3100。

电路采用反馈置数法,且2次所置的数不同。

采用反馈置数法形成10进制计数器。

试用74161设计一个计数器,其计数状态为0111~1111。

作状态转换图,并作电路图如下:

5.10试分析图5.46所示电路,画出它的状态图,说明它是几进制计数器。

图5.46题5.10图

分析图示电路,可见采用反馈清零法实现10进制计数器,其状态转换图如下:

5.11试用74160构成二十四进制计数器,要求采用两种不同的方法。

74160为同步10进制加法计数器,功能表及管脚与74161相同。

实现24进制计数器的途径是:

先用2片74160扩展为100进制计数器,然后采用反馈清零法或者反馈置数法实现24进制计数器。

反馈清零法:

LD=1,

反馈置数法:

RD=1,DCBA=0000

讨论:

也可用74160分别实现4进制和6进制计数器,然后级联;

或者分别实现3进制和8进制计数器,然后级联。

5.12试设计一个能产生011100111001110的序列脉冲发生器。

采用计数器+数据选择器的实现途径。

按题意应有一个15进制计数器和一个16选1数据选择器。

计数器采用74161通过反馈置数法实现,数据选择器采用2片74151扩展构成。

电路图如下:

5.13设计一个灯光控制逻辑电路。

要求红、绿、黄三种颜色的灯在时钟信号作用下按表5.14规定的顺序转换状态。

表中的1表示灯“亮”,0表示灯“灭”。

分析题目要求,方案一可用8进制计数器和3个数据选择器实现;

方案二用计数器和门电路实现。

此处采用方案二设计电路如下。

5.14试用JK触发器和与非门设计一个11进制加计数器。

作状态转换表如下:

K0=1

5.15试用JK触发器(具有异步清零功能)和门电路采用反馈清零法设计一个9进制计数器。

依据题意,先用4个JK触发器组成4位二进制计数器,然后利用反馈清零法实现9进制计数器。

上述电路存在的问题是:

如果FF0或者FF3先清零,则RD端的清零信号消失,FF1、FF2可能达不到清零的目的。

改进的电路如下图所示,电路中利用了基本RS触发器的记忆功能。