FPGA典型设计方案精华汇总Word下载.docx

《FPGA典型设计方案精华汇总Word下载.docx》由会员分享,可在线阅读,更多相关《FPGA典型设计方案精华汇总Word下载.docx(23页珍藏版)》请在冰豆网上搜索。

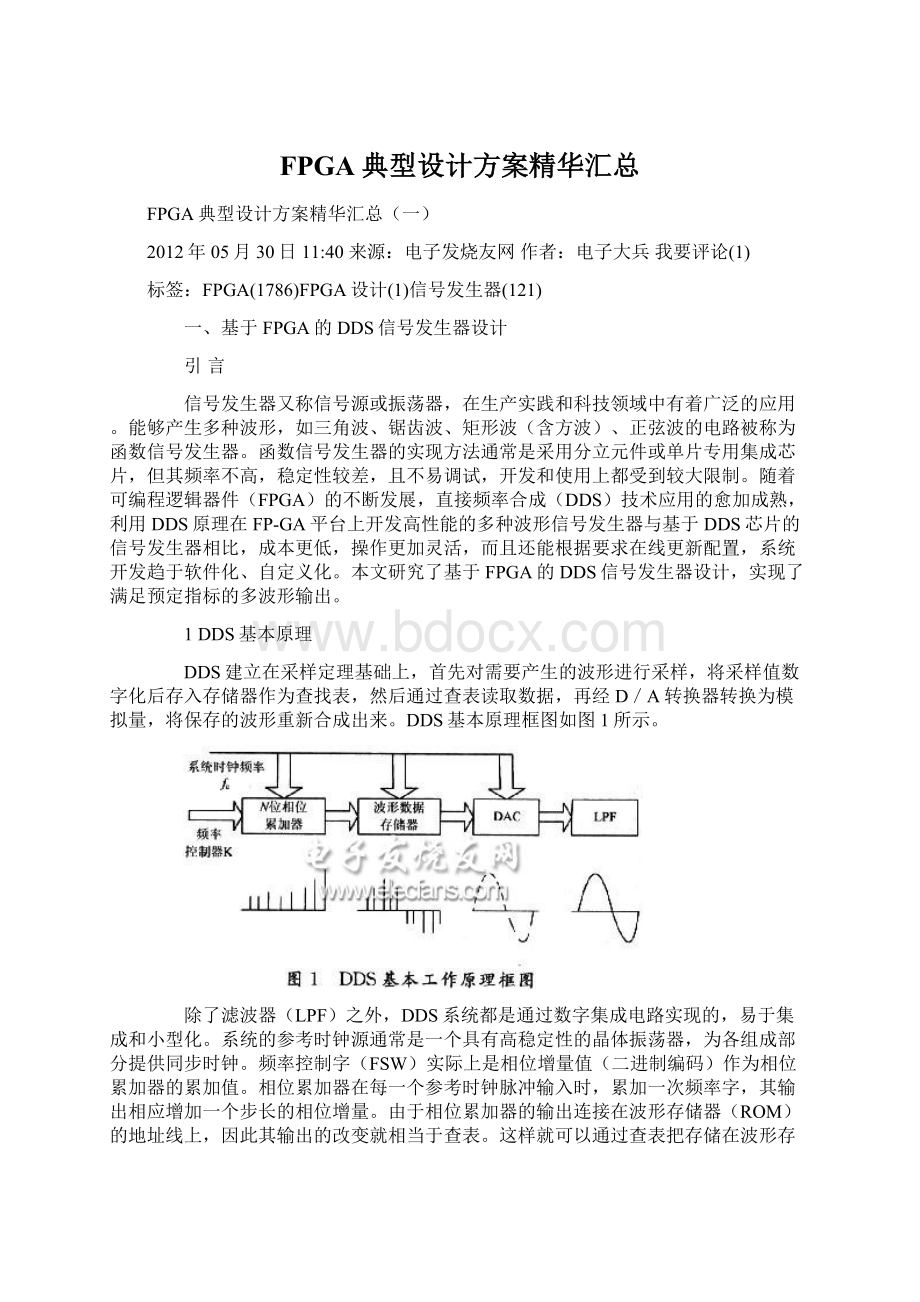

2系统总体方案设计

该设计以FPGA开发平台为核心,将各波形的幅值/相位量化数据存储在ROM内,按照设定频率,以相应频率控制字k为步进,对相位进行累加,以累加相位值作为地址码读取存放在存储器内的波形数据,经D/A转换和幅度控制、滤波即可得到所需波形。

波形发生器采取全数字化结构,用硬件描述语言Verilog设计实现其频率可调可显示。

经开发平台的D/A转化和外加滤波整形处理波形数据,理论上能够实现任意频率的各种波形。

系统总体设计方框图如图2所示。

系统按工作原理和控制对象的先后分为三个功能单元:

波形数据产生单元、D/A转化单元和滤波整形处理单元。

波形数据产生单元除具有波形数据输出功能外,还有频率设置和输出显示功能。

波形信号频率可设置范围为0~99999999Hz,系统时钟采用外接晶体振荡器40MHz时钟脉冲,频率稳定度优于10-4输出采用8位LED数码循环动态显示。

D/A转换单元负责对从ROM表里读取的波形数据进行D/A转换,对D/A转换器件的选用从建立时间、位数、转化误差和转换时间等四个方面考虑。

滤波整形处理单元完成对D/A转换的模拟波进行平滑,滤除杂波和高频干扰,补偿频带损耗和幅度损失,最终输出低误差、高质量、满足题设要求的波形。

3系统功能单元实现

3.1波形数据产生单元

波形数据产生单元是信号发生器设计的主体。

在此,采用DDS原理设计的信号发生器能完成三种波形(正弦、三角和方波)数据的产生,而且根据控制信号还可完成选定波形指定频率的输出。

波形数据产生单元按功能实现上的相互联系可划分为频率控制字生成模块、相位累加器模块和波形数据ROM表模块,如图3所示。

其中,频率控制字生成模块可根据输入产生指定频率字,同时显示输入频率数字。

相位累加器模块负责对所选波形的相位寻址,以频率控制字作为步长反复进行累加运算。

波形数据ROM表模块存放三种波形的幅值/相位量化值,通过地址选择相应波形的数据。

系统输入控制使用4×

4键盘.键盘主要按键功能介绍如下:

“0~9”:

数字键,设定信号频率;

“确定”:

用于对波形信号设置的确认,波形信号的设置必须“确定”后才有效;

“←”:

删除已输入信号频率数字的最后一位,用于修改设置的频率;

“清零”:

将频率数字快速全部清零;

“↑”:

步进增大控制;

“↓”:

步进减小控制。

设定频率输出范围为1kHz~10MHz,频率步进为50Hz。

系统输出采用8个LED数码管,以扫描方式显示(单位为Hz)频率数字。

根据DDS原理,以步进值50Hz作为频率控制字1,那么最大值10MHz对应的频率控制字为200000,用18位二进制数值就可以表示(218》200000)。

从抽样值恢复出原波形数据,理论上每个周期波形数据至少抽取2个点,考虑到实际应用时受频率损耗、线间串扰等因素的限制,该设计采用22b的频率控制字和相位累加器,4Kb的8位波形ROM表,取相位累加器输出的高12b寻址波形数据,三种波形按幅值/相位对应关系分别存储782个数据。

故各波形数据单位周期有800768(782×

210)个相位状态,完全满足任一波形在单位周期内取4个幅值点的要求,可保证即使输出最大频率的波形仍能达到较好的效果。

波形选择功能由两位开关组合实现,共有四种状态,其中三组用来表征不同的波型,另一组留作扩展波形用。

3.2D/A转换单元

数/模转换单元是继波形数据产生单元之后,将数字量形式的波形幅值转换成所要求的合成频率的模拟量形式信号。

DAC输出信号实际上是阶梯模拟信号,需在数/模转换后利用低通滤波器对波形进行平滑处理。

在此,采用ADI公司生产的单片双8位CMOS乘法数/模转换器AD7528,线性度达到1/2,转换时间达到纳秒级,可以很准确地进行10MHz信号的量化运算。

3.3滤波处理单元

滤波器是一种能通过有用频率信号而同时抑制(或衰减)无用频率信号的电子装置。

由于运算放大器具有近似理想的特性,且可以省去电感,得到接近理论预测的频率响应特性。

构成有源滤波电路后还具有一定的电压放大和缓冲作用,并能减小体积。

综合考虑,系统采用运算放大器SL560构成二阶低通滤波器。

4系统功能仿真和验证分析

4.1频率控制字生成模块仿真与分析

频率控制字的生成直接影响着波形数据的寻址,该模块负责快速记录并实时显示输入的频率数字,准确计算得到相应的频率控制字。

系统键盘为高速动态扫描(频率为200Hz),采用状态机设计,设置了按键去抖动功能。

在FPGA开发平台对该模块进行功能验证,整体无误操作产生,几乎没有时滞效应,按键的防抖动效果也良好,达到了预期的目的。

4.2相位累加器模块仿真与分析

相位累加器用于实现相位累加,并存储其累加结果。

当前,相位累加器的值和时钟周期到来后的相位累加器的值相差k(k为频率控制字)。

该模块的仿真波形如图4所示。

4.3实验波形观测与误差分析

信号发生器功能验证无误,用示波器观测实验波形如图5所示。

检测输入频率为0~10MHz时,波形形状均良好,未出现明显失真。

计算理论误差为0.095%,在实测中发现,波形数字的误差相对很小,不足0.1%。

由于滤波整形电路存在高频耦合通路,产生线间串扰,对滤波效果形成了不利影响,因此滤波器设计必须满足频带宽,截止特性好,抗干扰性强等特性。

5结语

介绍了以直接数字频率合成技术(DDS)为基础的波形信号发生器工作原理和设计过程,并在FPGA实验平台上设计实现了满足各功能指标的信号发生器。

系统硬件除需外加滤波整形电路外,其余部分均可在FPGA开发实验系统KH-310上集成开发,系统软件可在Quartus下编写代码,实现数据信息处理和控制操作等功能。

整体开发环境成熟,应用工具齐全,随着FPGA性价比的不断提高,基于FPGA平台开发信号发生器将逐步走向标准化、规模化和产品化。

现代电子和通信技术的发展,对信号发生器提出了更高、更严格的要求。

除了对信号频率范围、带宽和频率分辨率的严格限制外,对信号的波型及调制特性等也有着苛刻的规定。

研究和开发具有更高性价比的信号发生器将是当前和今后一段时间内亟需解决的课题。

这里旨在建立一种基于FPGA的简单数字信号发生器设计方法。

若能充分利用FPGA强大的数据运算处理能力以及编程灵活、运行速率快等优点,合理整合IP核资源和SoPC技术,简化设计结构,一定可以设计出功能多样、性能更加出色的信号发生器。

FPGA典型设计方案精华汇总

(一)

(2)

二、基于FPGA的信号发生器设计

以FPGA芯片为载体,通过QuartusII的LPM_ROM模块和VHDL语言为核心设计一个多功能信号发生器,根据输入信号的选择可以输出递增锯齿波、递减锯齿波、三角波、阶梯波和方波等5种信号,通过QuartusII软件进行波形仿真、定时分析,仿真正确后,利用实验板提供的资源,下载到芯片中实现预定功能。

信号发生器又称为波形发生器,是一种常用的信号源,广泛应用于电子电路、通信、控制和教学实验等领域。

它是科研及工程实践中最重要的仪器之一,以往多用硬件组成,系统结构比较复杂,可维护性和可操作性不佳。

随着计算机技术的发展,信号发生器的设计制作越来越多的是用计算机技术,种类繁多,价格、性能差异很大。

用FPGA或CPLD来实现,它的优点是可以进行功能仿真,而且FPGA和CPLD的片内资源丰富,设计的流程简单。

用FPGA所构成的系统来产生波形信号,这个系统既能和主机系统相连,用相应的上层软件展示波形信号,又方便程序的编写,而且还有A/D0809接口可以产生模拟信号的输出和外面的示波器相连。

1正弦信号发生器的LPM定制

正弦信号发生器由计数器或地址发生器(6位)、正弦信号数据ROM(6位地址线,8位数据线,含有64个8位数据,一个周期)、原理图顶层设计和8位D/A(实验中用DAC0832代替)。

其框图如图1所示。

其中信号产生模块将产生所需的各种信号,这些信号的产生可以有多种方式,如用计数器直接产生信号输出,或者用计数器产生存储器的地址,在存储器中存放信号输出的数据。

信号发生器的控制模块可以用数据选择器实现,用8选1数据选择器实现对5种信号的选择。

图1信号发生器结构框图

最后将波形数据送入D/A转换器,将数字信号转换为模拟信号输出。

用示波器测试D/A转换器的输出,可以观测到5种信号的输出。

1.1定制初始化数据文件

QuartusII能接受的LPM_ROM模块中的初始化数据文件的格式有两种:

。

mif格式文件和。

hex格式文件。

实际应用中只要使用其中一种格式的文件即可。

下面采用。

mif格式文件,调出产生ROM数据文件大小的选择窗。

根据64点8位正弦数据的情况,可选ROM的数据数Number为64,数据宽Wordsize取8位。

单击OK按钮,将出现图2所示的空的。

mif数据表格,表格中的数据格式可通过鼠标右键单击窗口边缘的地址数据弹出的窗口选择。

图2.mif数据表格

将波形数据填入mif文件表中也可以使用QuartusII以外的编辑器设计MIF文件,其格式如下:

#include《STdio.h》

#include“math.h”

main()

{inti;

floats;

for(i=0;

i《1024;

i++)

{s=sin(atan

(1)*8*i/1024);

printf(“%d:

%d;

\n”,i,(int)((s+1)*1023/2));

}}

把上述程序编译成程序后,可在DOS命令行下执行命令:

romgen》sin_rom.mif;

1.2定制LPM元件

打开MegaWizardPlug_InManager初始对话框,选择Createanewcustom…项。

单击Next按钮后,选择Storage项下的LPM_ROM,再选择ACEX1K器件和VHDL语言方式;

最后输入ROM文件存放的路径和文件名:

F:

\sing_gnt\data_rom(定制的ROM元件文件名),单击Next按钮,选择ROM控制线、地址线和数据线。

这里选择地址线位宽和ROM中数据数分别为6和64;

选择地址锁存控制信号inclock。

对于地址信号发生器的设计。

方法一:

用VHDL语言设计6位计数器,产生其元件符号;

方法二:

仍采用LPM定制的方法。

1.3完成顶层设计

按图3画出顶层原理图,然后进行编译,波形仿真如图4所示。

图3简易正弦信号发生器顶层电路设计

图4当前工程仿真波形输出

对当前设计通过执行QuartusII的命令Create∠Update/CreateSymbolFilesforCurrentFile,可以为设计电路建立一个元件符号,以便被顶层设计多功能信号发生器所调用。

2其他信号部分原程序

其他各信号发生器可参照正弦信号发生器的设计方法设计或直接采用VHDL硬件描述语言进行设计。

LIBRARYIEEE;

--递增锯齿波的设计

USEIEEE.STDLOGIC1164.ALL;

USEIEEE.STDLOGICUNSIGNED.ALL;

ENTITYsignal2IS--递增锯齿波signal1

PORT(clk,reset:

INstd_logic;

--复位信号reset,时钟信号clk

q:

OUTstd_logic_vector(7DOWNTO0));

--输出信号q

ENDsignal2;

ARCHITECTUREbOFsignal2IS

BEGIN

PROCESS(clk,reset)

VARIABLEtmp:

std_logic_vector(7DOWNTO0);

IFreset=‘0’THEN

tmp:

=“00000000”;

ELSITrising_ege(clk)THEN

IFtmp=“11111111”THEN

ELSE

=tmp+1;

--递增信号的变化

ENDIF;

q《=tmp:

ENDPROCESS;

ENDb;

--方波的设计

USEIEEE.STD_LOGIC_1164.ALL;

USEIEEE.STD_LOGIC_UNSIGNED.ALL;

entitysignal5is--方波signal5

instd_logic;

--复位信号reset,时钟信号clk

outstd_logic_vector(7DOWNTO0));

--输出信号q,8位数字信号

ENDsignal5;

ARCHITEECTUREaOFsignal5IS

SIGNAL;

a:

std_logic;

YARIABLEtmp:

std_logic_vector(7downto0);

BEQIN

IFreset=‘0’then

a《=‘0’;

elsifrising_edge(clk)THEN

IFtmp=“11111111”THEN

iftmp《=“10000000”then

a《=‘1’;

else

PROCESS(clk,a)

IFrising_edge(clk)THEN

IFa=‘1’THEN

q《=“11111111”;

q《=“00000000”;

ENDa;

FPGA典型设计方案精华汇总

(一)(3)

3顶层电路的设计

将上述6个模块生成符号,供顶层电路调用。

这些模块分别是:

递减锯齿波信号产生模块signall、递增锯齿波信号产生模块signal2、三角波信号产生模块signal3、阶梯波信号产生模块signal4、方波信号产生模块signal5和数据选择器mux51。

顶层电路的连接如图5所示。

图5信号发生器顶层电路

4D/A转换器的连接

选择一个D/A转换器,将数据选择器的输出与D/A转换器的输入端连接。

D/A转换器的可选范围很宽,这里以常用的DAC0832为例。

DAC0832的连接电路如图6所示。

图6DAC0832的连接电路

5实现与测试

信号发生器顶层电路的仿真波形如图7所示,这里只就输入选择信号等于5时的情况进行仿真,此时输出波形是方波,输出的数字信号为周期性的全0或全1。

图7信号发生器顶层电路的仿真波形

信号发生器的底层电路模块也可以分别进行仿真,例如对阶梯波信号产生模块signal4进行仿真,仿真波形如图8所示,输出的数字信号为阶梯状变化。

图8阶梯波信号产生模块signal4的仿真波形

6结束语

硬件电路设计主要是设计相关模块的设计思想的可视化,是相关模块的电路图的汇总和其相关仿真波形的集锦,该部分条理清晰,思路明确,从中我们可以清晰地看到该设计方案的具体模块和整个设计的原理结构实图;

程序设计这一部分主要阐述该设计的设计方法与设计思想,进一步从软件设计上揭示设计构思,主要包含了整个设计所用到的模块的硬件描述语言的设计,本文设计思路清晰,通过QuartusII软件进行波形仿真成功,特别是正弦信号发生器的LPM定制对于编程不是特别强的人员提供另一种途径来实现,加深理解EDA的层次设计思想,很好的把握住了教学的改革方向,更好的锻炼了学生理论联系实践的能力。

三、基于FPGA及VHDL的LED点阵汉字滚动显示设计方案

汉字滚动显示器的传统设计方法是用单片机来控制的,虽然单片机方案具有价格低廉,程序编程灵活等特点,但由于单片机硬件资源的限制,未来对设计的变更和升级,总是要付出较多研发经费和较长投放市场周期的代价,甚至有可能需要重新设计。

况且,在以显示为主的系统中,单片机的运算和控制等主要功能的利用率很低,单片机的优势得不到发挥,相当于很大的资源浪费。

采用EDA技术的自顶向下的模块化设计方法,借助相关开发软件,例如QualtusⅡ软件,将硬件描述语言——VHDL程序固化于具有丰富I/O口、内部逻辑和连线资源的FPGA(现场可编程门阵列)中。

该技术具有系统设计效率高、集成度好、保密性强、易于修改、易于实现等优点,成为当今数字系统设计主流技术。

此方式所制作的LED点阵控制器,由于是纯硬件行为,具有速度快、可靠性高、抗干扰能力强、开发周期短等显著优点。

1EDA点阵显示汉字原理

以8×

8的LED点阵为例,8×

8的LED点阵是由64个发光二极管按矩阵形式排列而成,每一行上的发光管有一个公共的阳极(或阴极),每一列上的发光管有一个公共的阴极(或阳极),一般按动态扫描方式显示汉字或图形。

扫描分为点扫描、行扫描和列扫描三种方式。

行扫描需要按行抽取字型码,列扫描则需要按列抽取字型码。

为满足视觉暂留要求,若使用点扫描方式,其扫描频率必须大于16×

64=1024Hz,周期小于1ms。

若使用行或列扫描,则频率必须大于16×

8=128Hz,周期小于7.8ms。

由于所用实验板上提供有1kHz的时钟,本例设计中利用该时钟进行扫描,使每行扫描时间为1ms,实验结果显示亮度合适。

现以行扫描为例简单说明动态扫描显示的原理。

图1给出汉字“热”在点阵为列共阳时的行字模。

工作时先将要扫描行的点阵字模从各列上输出,再让译码器选中(扫描)该行,使本行得以显示,接着再送下一行数据,再使下一行有效,直到8行全被扫描一遍。

至此,一幅完整的文字信息就显现出来,然后再反复扫描这8行直至显示新的信息。

以下设计采用行扫描方式实现滚动显示。

2硬件原理图

整个电路由五大部分组成:

时钟计数模块GEL_CLK,存储汉字字模的ROM模块ROMZI,数据分配器模块MUX,移位模块YW及显示模块XIANSH-I。

时钟计数模块用于产生整个电路所需要的时钟及其对时钟的计数值,例如:

移位时钟CLKYW,移位计数器CNTYW,字计数器CNTWORD,显示扫描计数器CNTSM。

ROMZI模块是由QualtusⅡ中的LPM1PORTROM定制成,用来存储8个待显示的汉字。

MUX模块用于在扫描时钟及扫描计数器的作用下,从ROM中读出一个汉字的8个行字模信息,送给移位模块YW,YW模块在移位时钟及移位计数器作用下,根据SELECT信号选择对读出的字模信息,进行相应的移位(左移、右移、上移、下移)后,最后送显示模块DISP驱动LED点阵显示汉字。

原理图如图2所示。

FPGA典型设计方案精华汇总

(一)(4)

40来源:

电子发烧友网作者:

电子大兵我要评论

(1)

3模块设计及时序仿真

3.1时钟计数产生模块

时钟计数产生模块由1kHz的输人时钟为基准,进行17位的循环计数CNT[16..O]。

该时钟,既是动态扫描显示的时钟,也是从ROM中取一个字8个字模的时钟,对之进行的3位循环计数作为扫描显示计数器和取一个字的字型码计数器。

CNT[16..O]中的CNT[9]是对该时钟的1024分频,将其作为移位时钟CNT_YW,周期约为ls。

CNT[13…lO]作为4位的移位计数器,是对移位时钟CLK_YW的计数,也是对移位位数的统计。

16个状态使一个汉字逐列移进点阵,又逐列移出。

每经过16个移位时钟,将会显示完一个汉字。

CNT[16..14]作为3位的取字计数器。

CNT[16…14]&

CNT[2..O]作为ROM地址发生器。

3.2ROMZI模块

利用LPM参数化模块库中单口ROM,利用QualtusⅡ中的MegaWizardPlug-InManager定制而成,定制前首先要制作LPMROM初始化文件,其中存储待显示汉字的字模数据,然后按照LPMMegaWizardPlug-InManager的向导提示,结合设计要求进行定制。

图3为所定制ROM中的初始化汉字“元旦生日开心快乐”的字型码。

数据分配模块MUX要求能在8个时钟作用下,从ROM中读出一行(一个汉字的8个字型码)分