射频电路结课论文wifi产品的一般设计Word文档下载推荐.docx

《射频电路结课论文wifi产品的一般设计Word文档下载推荐.docx》由会员分享,可在线阅读,更多相关《射频电路结课论文wifi产品的一般设计Word文档下载推荐.docx(16页珍藏版)》请在冰豆网上搜索。

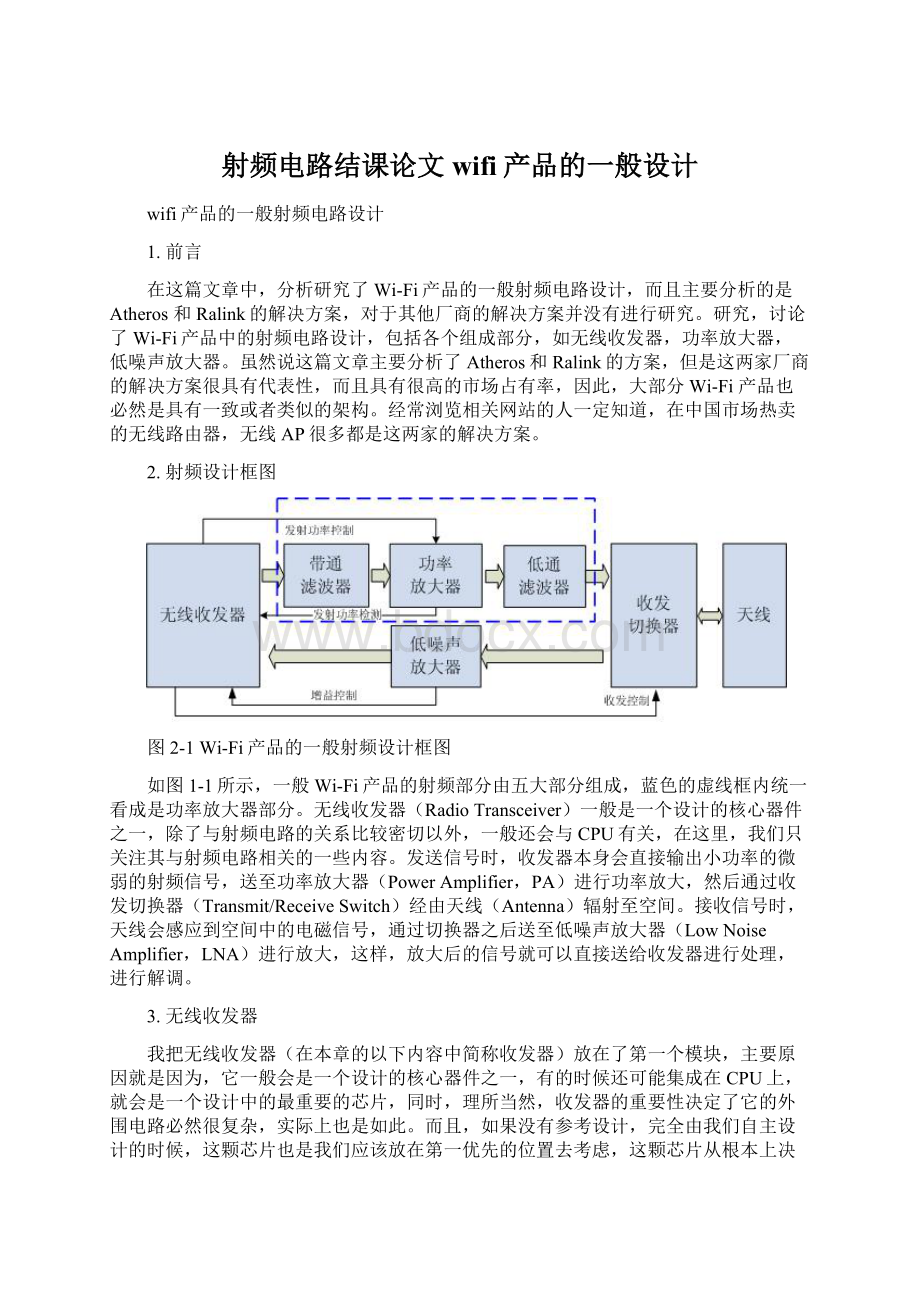

图3-1一般的无线收发芯片(射频电路设计相关)

3.1差分射频信号的处理

3.1.1收发器本身具有的管脚

对于射频信号,为了增强收发器的抗干扰能力,一般会采用差分信号的处理方式,也就是说,收发器会以差分形式将信号发送出去,同时外部电路也必须为收发器提供差分射频信号的输入。

如图2-2所示,红色方框内的四只管脚就是这个收发器的差分射频信号的输入,输出管脚,也是最重要的射频信号管脚。

图3-2收发器的射频输入与输出管脚

这里必须指出的是,Atheros的收发器一般会同时对输入与输出做差分处理。

但是Ralink一般要求外部输入的信号是差分的,而自身输出的射频信号则不是差分的。

图3-3和图3-4分别给出了RT3052(Ralink)和AR9220(Atheros)的主要射频信号管脚。

不难发现,Atheros的设计相比Ralink要更加细腻,不只是收发器芯片,在后续电路的设计中,也会发现,Atheros考虑的问题很周全,我想,这也是我们作为研发人应该具备的一种精神。

图3-3RT3052的主要射频信号管脚

图3-4AR9220的主要射频信号管脚

3.1.2收发器发送的差分信号

收发器发送的差分信号,我们要想办法把他们合二为一。

为什么要这样做,收发器送出的信号是要给功率放大电路的,功率放大电路处理的是单端信号。

平衡器通常用来处理差分信号的问题,除此之外,我们知道,电感和电容都能够改变信号的相位,从差分信号到单端信号,基本的方法就是用电感和电容组成两条不同的通路,这样,经过处理电路的两路信号就在相位上相差了180°

,从而可以使原本相位相差180°

的差分信号同相,得到单端信号。

相反,使单端信号通过两条不同的通路,就得到了差分信号。

下面让我们来分别看一下这两种方法的电路形式。

方法一,使用平衡器。

原本相位相差180°

的差分信号经过平衡器(Balun,俗称巴伦),就可以得到合二为一的单端射频信号。

如图3-5所示,图中的F1就是一个平衡器,差分信号RFOUT_P和RFOUT_N经过F1得到单端信号RF_OUT。

图3-5典型的平衡电路

方法二,使用分立元件。

典型的使用分立元件的处理电路如图3-6所示。

图3-6典型的分立元件处理电路

3.1收发器完整的外围电路设计

收发器,收发器相关的差分信号处理,收发器的电源供给,这三方面的内容基本上较完整的覆盖了收发器射频电路设计的内容,也就是说,把这三部分弄清楚,基本上就完成了这部分的设计。

想必大家应该比较清楚那三部分的结构了,好,让我们来试一下,在图3-1那个芯片的外围放置一些器件,再连上几条线,完成无线收发器及其外围电路设计。

在这里,我们对收发器输出的差分信号用平衡器处理得到单端信号RFOUT,来自低噪声放大器的接收信号RFIN用分立元件处理得到差分信号RFIN_P,RFIN_N。

这样,就得到了如图3-2所示的原理图。

图3-2完整设计的无线收发器外围电路

4.功率放大器

功率放大器,PowerAmplifier,俗称PA,主要的作用就是将无线收发器(RadioTransceiver)送来的射频信号进行功率放大,保证有足够大的输出功率满足设计需求。

功率放大器的设计是一个十分专业的话题,也有很多人,很多高级的射频工程师在这方面进行过十分深入的研究,我在这里只针对我们的Wi-Fi产品的常用的设计方法进行讨论。

我们的产品中,功率放大器的组成无非就是一颗芯片配上几颗外围的器件,但是在大功率的场合,几乎不会有人用集成电路去做功率放大,一般都是用分立元件设计出来的,晶体管或场效应管。

在我们目前的所有设计中,功率放大器都是用集成电路来实现的。

如图3-1所示,是通常的功率放大器的设计框图。

图4-1功率放大器的框图

功率放大器的设计会考虑很多参数,但主要分为三类:

增益,噪声,非线性。

增益,和最终的输出功率有关,噪声和非线性关系着信号质量。

图4-2典型的功放芯片

4.1功放芯片的供电

图4-2展示的一般功放芯片有三个电源管脚,分别是VCC,VC1,VC2,其中的VCC是主电源供电,VC1是芯片内部第一级放大的供电,VC2是芯片内部第二级放大的供电。

这里有个很重要的问题需要注意,VC1和VC2不是简单的供电管脚,这两个管脚通常不会直接连接到电源上,一般会串联一个电感(或者电阻)再连接到电源上,为什么呢?

这是因为这是为芯片内的功率晶体管(或场效应管)供电的管脚,通常在分离元件组成的功率放大电路中,我们都会看到在晶体管的集电极(或者场效应管的漏极)上都串有电感,而电感是不容易集成到芯片中的,这样,就需要在芯片的外部放置电感,这样,就得到了典型的功放芯片的供电方式,如图4-3所示。

图4-3典型的功放芯片供电方式

除了上面提到的电感的问题,另一个值得注意的就是,功放电路处理的模拟信号,是正统的模拟电路,因此需要尤其注意其电源要与数字电路的电源分开。

另一个极为重要的问题是,如图4-3所示,在每个电源管脚处,都需要放置一个滤波电容组合,例如VCC管脚处放置的是100pF和1000pF的滤波电容组合,VC1管脚处是10pF的电容。

滤波电容的组合形式是这样的,对于主电源管脚VCC,需要尽量多地放置不同容量的电容,而且这些电容的容量最好是不同数量级的,例如可以这样组合:

10uF+1uF+0.1uF+1000pF+100pF+10pF,不同容量的电容用于滤除不同频率成分的扰动。

对于VC1和VC2这两个管脚,要注意,放置的滤波电容容量要较小,通常在1-10pF。

4.2输入回路

功放电路的输入回路一般包括两个部分,一个是带通滤波器(BandPassFilter,BPF),一个是∏型匹配网络,我们分开两部分来讲。

4.2.1带通滤波器

我们知道,2.4GHz频段的子载波有13个,频率从2.412GHz到2.437GHz,相邻两信道之间的频率间隔是500MHz,很容易理解,从收发器(Transceiver)输出的信号包括了从2.412GHz到2.437GHz这样的一个频率带,因此,为了能够使有用的信号顺利地进入功放芯片,无用的杂乱信号被滤除,一般会在功放芯片的输入回路上放置一个带通滤波器。

带通滤波器有三种实现方法,一种是使用已经设计好的专用带通滤波器,这在Ralink的方案中使用的很多;

一种是使用分立元件组成的带通滤波器,这种方法用的不是很多;

第三种方法几乎是Atheros专有的,就是印制带通滤波器,这种滤波器最突出的优点就是没有成本,最突出的缺点是占用的空间比较大,而且还需要净空区,在AP51中就使用了这种滤波器。

用分立元件设计带通滤波器需要复杂的计算过程,也需要较强的数学功底,我们在这里不进行过多的研究。

接下来我们主要讨论如何选择一款已经设计好的带通滤波器。

通常情况下,成品的带通滤波器,输入和输出阻抗都会控制在50欧姆的标称值,对于通频带相关特性,一张图表足以反映出来。

如图4-4给出了我们常用的HMD845H的S21参数与频率之间的关系。

很明显,该带通滤波器的通频带为2.4GHz-2.5GHz,对于通频带以外的频率,衰落的很快。

图4-4HMD845H的S21参数

4.2.2∏型匹配网络

匹配,这件事在射频设计中是极其重要的,很多时候,我们设计或者调试射频电路,都是在解决匹配的问题,永远记住这样一条经典的准则:

共轭匹配传输功率最大。

∏型匹配网络一般直接放在功放芯片的输入端,也就是放在RFIN这个管脚处,通常芯片的管脚不会匹配到50欧姆,我们也不会知道管脚的输入特性,这样的话,∏型匹配网络的必要性就可想而知了。

∏型匹配网络,顾名思义,形状很像字母∏,我们来看一下实际的∏型匹配网络。

图4-5给出的是Ralink常用的一种∏型匹配网络。

图4-5Ralink常用的∏型匹配网络

4.2.3完整设计的输入回路

以上我们讨论了功放电路的输入回路的两个组成部分,带通滤波器和∏型匹配网络,有了这两个部分,我们就可以设计一个完整的输入回路了。

如图4-6所示,就是一个设计完整的功放电路输入回路。

图中的U9就是一款成品的带通滤波器,而C108,C109和L14就组成了一个∏型匹配网络。

图4-6完整设计的功放电路的输入回路

4.3输出回路

在输出回路中,最重要的组成部分(在很多设计中也是唯一的组成部分)就是低通滤波器,这时可能有人会问,为什么这里要用低通滤波器,而不是像输入回路那样使用带通滤波器?

原因很简单,这里的低通滤波器要解决的主要问题时由于功放引起的高次谐波,如二次谐波,三次谐波甚至更高次数的谐波,当然,低通滤波器还要解决的问题就是匹配问题。

其实,在射频电路的设计中,匹配的这个问题会一直伴随着我们。

滤波器的设计需要很复杂的计算,在这里我不想探讨过多的理论知识,所以,我就不给出如何计算的方法,只给出一般的低通滤波器的形式。

这里需要指出的是,Atheros的设计一般会使用三个元件,而Ralink一般会使用五个元件。

如图4-7所示,是Ralink常用的滤波器形式。

在图中,C112,C111,C113,C110和C114就组成了一个低通滤波器,来自功放芯片的信号PA_OUT经过滤波器后得到LPF_OUT这信号送至后续电路。

图4-7Ralink常用的低通滤波器

这时,我们就可以把功放芯片的输出端与低通滤波器相连接,就得到了一般射频功率放大电路的完整的输出回路,如图4-8所示。

图4-8完整设计的功率放大器输出回路

4.4功率检测

功率检测功能在我们的很多设计中都可以找到,这项功能可以使无线收发器(RadioTransceiver)时刻监视着功放电路的输出功率,这样,当功放的输出功率改变时,无线收发器就可以调整自身的输出功率或者改变功放电路的增益,使功放电路的输出功率稳定在一个固定的值。

功率检测电路输出的是直流电压值,这个电压值送给无线收发器之后,无线收发器自身内部进行A/D转换,就可以得知功放电路的输出功率了。

功率检测实现的方法通常有两种,在Ralink的设计中,通常使用功放芯片自身的功率检测功能;

在Atheros的设计中,除了使用功放芯片本身的功率检测功能之外,一般还会有一种Atheros特有的设计,我们将分成两部分讨论。

3.4.1芯片内建的功率检测

我们在图4-2中已经看到,一般的功放芯片会有POWER_DETECT这样的一个管脚,这个管脚的作用就是用于功率检测的。

使用芯片内建的功率检测功能可以简化电路设计,常见的完整形式如图4-9所示。

图4-9常见的使用内建功率检测功能的电路形式

3.4.2芯片外围的功率检测电路

我们在这里用单独的一节来讨论外围的检测电路,其实要讲的就是Atheros的方案,因为这个设计实在是太有个性了,让我们来一起见识一下吧。

如图4-10所示,就是Atheros常用的功率检测方案。

图中的PC1就是一个印制耦合器(PrintedCoupler),来自功率放大器的输出信号LPF_OUT经过耦合器,就在2,3脚感应到高频交变电压,这个电压随着输出功率的增大而增大L18,L19,D1,C217,R248组成了常规的整流电路,这样,就得到了随着输出功率的变化而变化的直流电压POWER_DETECT,无线收发器就可以得到这个电压值从而做作出相应的动作。

这里有一点需要注意的是,整流二极管D1一定要选择工作频率很高的二极管,例如这个设计中的SMS7630的工作频率就达10GHz。

图4-10Atheros常用的功率检测方案

4.5增益控制

增益控制的作用就是可以改变功放电路的增益,从而能改变输出功率。

改变功率放大器最终输出功率的方法有两种,一种是无线收发器改变自身的输出功率,另外一种就是改变功放电路的增益,在这里我们主要关注后者。

通常功放芯片的增益控制管脚会有两个或者两个以上,分别改变的是第一级放大和第二级放大的增益值,图4-11是典型的增益控制原理图。

来自收发器的控制信号PA_GAIN经过R245和C248组成的RC滤波电路(滤除来自收发器的可能的交流成分)通过两个电阻作用于功放芯片的GAIN_1和GAIN_2两个管脚,从而控制功率放大电路的增益,也控制着最终的输出功率。

图4-11典型的增益控制原理图

3.6温度检测

温度检测功能在Ralink的方案中使用的很多,但是在Atheros的方案就未曾见过。

这一功能可以检测功放芯片的温度,防止芯片温度过热而烧毁。

另外一个更加重要的作用就是根据环境温度调整功放电路的输出功率。

很多情况下,环境温度的改变,会对功放芯片的输出功率会造成比较大的影响,如果无线收发器通过温度检测电路得知当前的温度并适当的调整自身的输出功率或者改变功放的增益,就可以使功放电路在环境温度改变时依然可保持稳定的功率输出,这对于提高产品的稳定性是有好处的。

图4-12给出的是Ralink的典型的温度检测电路。

图中的RT1是热敏电阻,当环境温度改变时,自身的阻值会发生变化,这样,显而易见,TMP_DET的值就会发生变化,这样,收发器就可以检测到环境的温度了。

温度检测电路一般会放置在功放芯片的附近。

图4-12Ralink常用的温度检测电路

4.7完整设计的功率放大电路

如图4-2所示。

将图4-1中的各部分电路链接,就得到了完整的功率放大器。

通常情况下,在功放芯片的Datasheet中会给出一份参考设计,这对于我们的设计具有一定的指导作用。

图4-13完整设计的射频功率放大电路

5.低噪声放大器

低噪声放大器在框图1-1中位于收发切换器(Transmit/ReceiveSwitch)和无线收发器(RadioTransceiver)之间,对天线感应到的信号进行放大,这样才能使无线收发器进行有效的处理。

可以说,低噪声放大器的性能直接影响着整个设计的灵敏度。

低噪声放大器的框图如图4-1所示,有四个部分组成,输入回路,输出回路,放大电路,增益控制,在以下的内容中,我们将逐个讨论。

图5-1低噪声放大器的框图

5.1完整设计的低噪声放大器

在这里,我要向大家展示的是一款设计十分细腻的低噪声放大器,这也是我见过的设计最为优秀的低噪声放大器,就是来自某实际案例中的2.4GHz频段的放大器,让我们来一同领略它的风采,如图5-2所示。

图中的LNA_GAIN是来自无线收发器(RadioTransceiver)的增益控制信号,放大器使用的晶体管就是最常用的SGA-8343,R238,R239,R240是基极的偏置电阻,C219,L20,C220组成了低通滤波器,来自切换芯片(Switch)的LNA_IN通过低通滤波器之后经由C218耦合至低噪声放大器,Q2与C221,L51,C214,R240,C210,R239,R238,C211,R241,C215,L52组成了共射极放大电路,最终输出RFIN送至收发器进行处理。

尤其值得我们注意的是,在每一个节点处,都放置了滤波电容,这样,就可以最大限度的消除任何可能的噪声,从而实现性能优秀的低噪声放大电路。

图5-2某实际案例中设计精良的低噪声放大器

6.收发切换电路

收发切换电路实现的功能就是进行发射与接收的切换,通常其最重要的组成部分就是一颗芯片,我们分成四个部分来讨论:

芯片的选择,发射与接收回路,天线回路,控制管脚的处理。

6.1切换芯片的选择

切换芯片在结构上,通常就是一个单刀双掷的开关,开关掷向哪一边决定于加在控制管脚上的电压。

切换芯片的典型内部结构如图5-1所示。

图6-1切换芯片典型的内部结构

经过添加外围电路,我们就得到了如图6-2所示的完整的切换电路的设计。

图6-2完整设计的切换电路

7.天线与天线连接器

在这一章里,讲的不是天线的设计,因为天线设计是一个十分专业和复杂的学科。

在这里我想要说的其实就只是一个问题:

一定要在天线或者天线连接器的附近放置一个∏型匹配网络,这一点是我们做射频设计的人必须要牢记的事实。

看一下Atheros和Ralink的方案,会发现∏型匹配网络是必不可少的,典型的设计如图6-1所示。

图7-1典型的天线连接器电路设计

8.完整设计的射频电路

在前面几章的内容中,我们分成五章分别讲解了射频电路的无线收发器(RadioTransceiver),功率放大电路(PowerAmplifier,PA),低噪声放大器(LowNoiseAmplifier,LNA),收发切换电路(Transmit/ReceiveSwitch),天线与天线连接器(AntennaAndConnector),在每章的最后一节,我们都给出了每一部分的完整设计。

我想你已经知道了——没错,只要把我们每个部分的完整设计组合在一起,那么我们就得到了Wi-Fi产品的一般射频电路的完整设计,我们不要急,我们再来回顾一下在本文一开始提到的射频设计框图,如图7-1。

相信大家这时一定已经可以把每一个部分细化,得到更加详细的射频设计框图。

图8-1射频设计框图

通过前面的讨论,我们已经知道,功率放大器是由带通滤波器,∏型匹配网络,功率微波器件,增益控制,供电电路,功率检测,温度检测低通滤波器这些部分组成的;

低噪声放大器是由∏型匹配网络,低噪声放大电路和增益控制组成的;

收发切换器是由∏型匹配网络,切换芯片,滤波器组成的;

天线和连线连接器部分是由∏型匹配网络和连接器组成的。

于是,我们得到了Wi-Fi产品一般射频电路的详细框图,如图8-2所示。

图8-2射频设计详细框图

现在,让我们将各个模块的详细电路图,看看我们得到了什么。

没错,我们得到了完整的设计图,如图8-3所示。

在这个原理图中,我们设计的是一收一发的情况,如果是二发二收,那么原理图就是两个图8-3,复制而已。

图8-3完整详细的原理图

9.总结

本文通过介绍一般wifi的射频电路设计,详细分析了各个组成部分的原理图,设计图,说明了射频电路对今后通信领域有着非常重要的作用。

对今后的学习实践有指导性的意义。