第4章组合逻辑电路习题解答Word格式.docx

《第4章组合逻辑电路习题解答Word格式.docx》由会员分享,可在线阅读,更多相关《第4章组合逻辑电路习题解答Word格式.docx(26页珍藏版)》请在冰豆网上搜索。

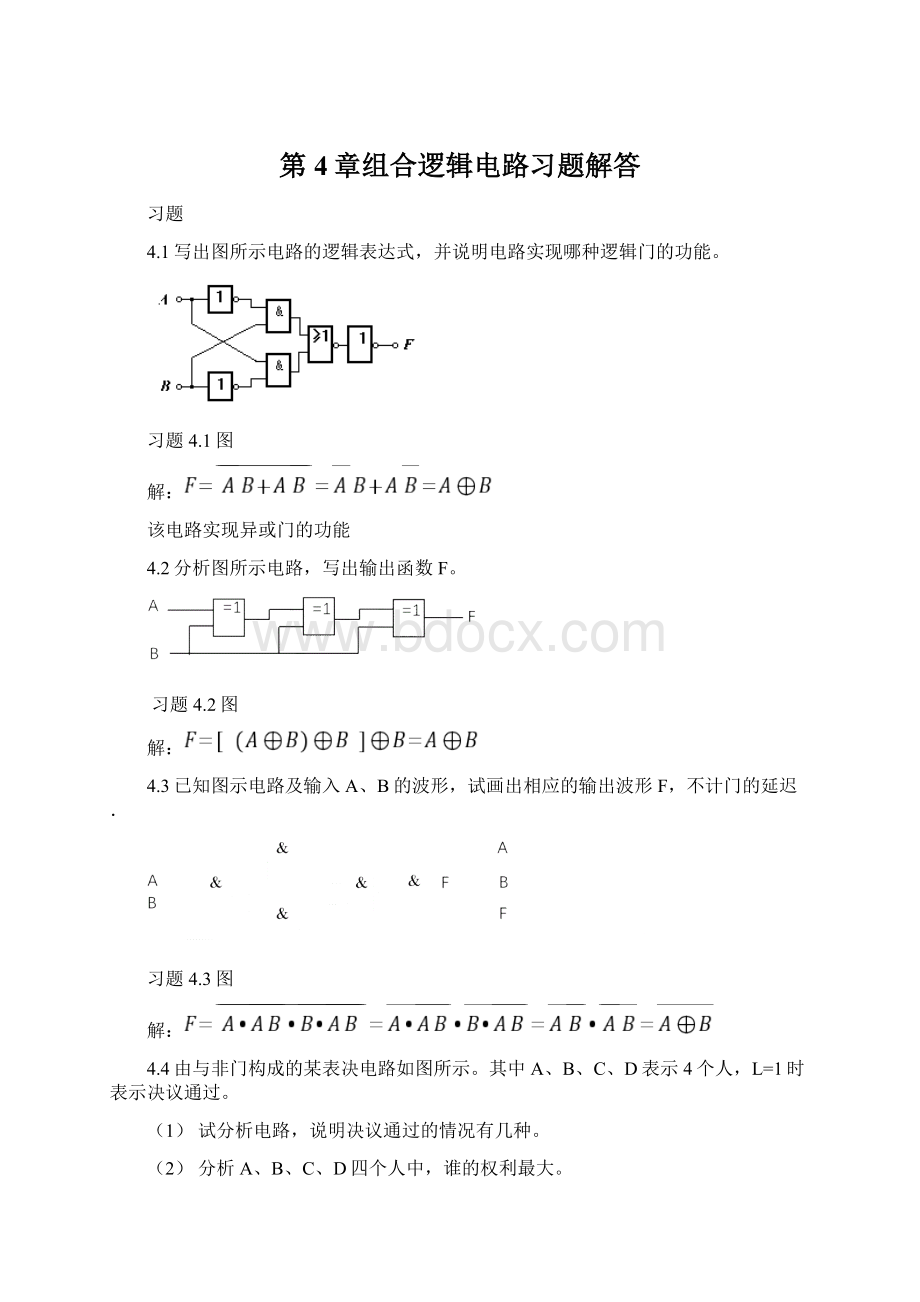

1011

1100

1101

1110

1111

(3)根据真值表可知,四个人当中C的权利最大。

4.5分析图所示逻辑电路,已知S1﹑S0为功能控制输入,A﹑B为输入信号,L为输出,求电路所具有的功能。

A

B

S1

S0

=1

&

习题4.5图

S1S0

00

01

10

11

A+B

(3)当S1S0=00和S1S0=11时,该电路实现两输入或门,当S1S0=01时,该电路实现两输入或非门,当S1S0=10时,该电路实现两输入与非门。

(2)

ABC

F

000

001

010

011

100

101

110

111

电路逻辑功能为:

“判输入ABC是否相同”电路。

4.7已知某组合电路的输入A、B、C和输出F的波形如下图所示,试写出F的最简与或表达式。

C

习题4.7图

(1)根据波形图得到真值表:

(2)由真值表得到逻辑表达式为

4.8、设

,要求用最简单的方法,实现的电路最简单。

1)用与非门实现。

2)用或非门实现。

3)用与或非门实现。

1)

(1)将逻辑函数化成最简与或式并转换成最简与非与非式。

(2)根据最简与非与非式画出用与非门实现的最简逻辑电路。

2)

(1)将逻辑函数的反函数化成最简与或式。

(2)利用反演规则将逻辑函数化成最简或与式并转换成最简或非或非式。

(3)根据最简或非或非式画出用或非门实现的最简逻辑电路。

(图略)

3)

(1)由上步可知逻辑函数的反函数化成最简与或式。

(2)则逻辑函数的最简与或非式为。

(3)根据最简与或非式画出用与或非门实现的最简逻辑电路。

4.9、设计一个由三个输入端、一个输出端组成的判奇电路,其逻辑功能为:

当奇数个输入信号为高电平时,输出为高电平,否则为低电平。

要求画出真值表和电路图。

(1)根据题意,设输入逻辑变量为A、B、C,输出逻辑变量为F,列出真值表为:

ABC

F

000

001

010

011

100

101

110

111

0

1

(2)由真值表得到逻辑函数表达式为:

(3)画出逻辑电路图

4.10、试设计一个8421BCD码的检码电路。

要求当输入量ABCD≤4,或≥8时,电路输出L为高电平,否则为低电平。

用与非门设计该电路。

(1)根据题意列出真值表为:

D3D2D1D0

×

(2)由真值表可得到输出逻辑函数表达式为:

(3)将输出逻辑函数表达式化简并转换为与非与非式为:

(4)画出逻辑电路图

4.11、一个组合逻辑电路有两个功能选择输入信号C1、C0,A、B作为其两个输入变量,F为电路的输出。

当C1C0取不同组合时,电路实现如下功能:

1.C1C0=00时,F=A

2.C1C0=01时,F=A⊕B

3.C1C0=10时,F=AB

4.C1C0=11时,F=A+B

试用门电路设计符合上述要求的逻辑电路。

(1)根据题意,列出真值表

(2)由真值表列出逻辑函数表达式为:

(3)根据逻辑函数表达式画出逻辑电路图。

C1C0AB

0000

0001

0010

0011

0100

0101

0110

0111

1000

1001

1010

1011

1100

1101

1110

1111

4.13、8-3线优先编码器74LS148在下列输入情况下,确定芯片输出端的状态。

(1)6=0,3=0,其余为1;

(2)EI=0,6=0,其余为1;

(3)EI=0,6=0,7=0,其余为1;

(4)EI=0,0~7全为0;

(5)EI=0,0~7全为1。

(1)74LS148在输入6=0,3=0,其余为1时,输出所有端均为1。

(2)74LS148在输入EI=0,6=0,其余为1时,输出A2A1A0=001,CS=0,EO=1。

(3)74LS148在输入EI=0,6=0,7=0,其余为1时,输出A2A1A0=000,CS=0,EO=1。

(4)74LS148在输入EI=0,0~7全为0时,输出A2A1A0=000,CS=0,EO=1。

(5)74LS148在输入EI=0,0~7全为1时,输出A2A1A0=111,CS=1,EO=0。

4.14、试用8-3线优先编码器74LS148连成32-5线的优先编码器。

4.15、4-16线译码器74LS154接成如习题4.15图所示电路。

图中S0、S1为选通输入端,芯片译码时,S0、S1同时为0,芯片才被选通,实现译码操作。

芯片输出端为低电平有效。

(1)写出电路的输出函数F1(A,B,C,D)和F2(A,B,C,D)的表达式,当ABCD为何种取值时,函数F1=F2=1;

(2)若要用74LS154芯片实现两个二位二进制数A1A0,B1B0的大小比较电路,即A>B时,F1=1;

A<B时,F2=1。

试画出其接线图。

Y0Y1Y2Y3Y4Y5Y6Y7Y8Y9Y10Y11Y12Y13Y14Y15

ABCD

F1

A3

A2

A1

A0

F2

习题4.15图

当ABCD=0111或ABCD=1001或ABCD=1101时,F1=F2=1。

(2)由题意得到真值表如下:

A1A0B1B0

F1F2

00

01

10

画出逻辑电路图为:

4、16用74LS138译码器构成如习题4.16图所示电路,写出输出F的逻辑表达式,列出真值表并说明电路功能。

习题4.16图

(1)由题可得逻辑函数表达式为:

(2)列出真值表如下:

电路的逻辑功能为:

奇偶判别电路。

4、17试用74LS138译码器和最少的与非门实现逻辑函数

2)F2(A,B,C)=A⊙B⊙C

(2)F2(A,B,C)=A⊙B⊙C

4.18、试用3线-8线译码器74LS138设计一个能对32个地址进行译码的译码器。

用3线-8线译码器74LS138设计一个能对32个地址进行译码的译码器如图所示。

G1

G2A

G2B

Y0

Y7

~

74LS138

Y16~Y23

Y24~Y31

-

Y0~Y7

Y8~Y15

A4

4.19、已知8421BCD可用7段译码器,驱动日字LED管,显示出十进制数字。

指出下列变换真值表中哪一行是正确的。

(注:

逻辑“1”表示灯亮)

D

a

b

c

d

e

f

g*

4

7

9

第二行4的显示是正确的。

4.20、已知某仪器面板有10只LED构成的条式显示器。

它受8421BCD码驱动,经译码而点亮,如图所示。

当输入DCBA=0111时,试说明该条式显示器点亮的情况。

习题4.20图

由图可知,二极管0~7均为亮的,8、9为熄灭的。

4.21、74LS138芯片构成的数据分配器电路和脉冲分配器电路如习题4.21图所示。

(1)图(a)电路中,数据从G1端输入,分配器的输出端得到的是什么信号。

(2)图(b)电路中,G2A端加脉冲,芯片的输出端应得到什么信号。

Y1

Y2

Y3

Y4

Y5

Y6

数据输入

地址

输入

(a)(b)

习题4.21图

图(a)电路中,数据从G1端输入,分配器的输出端得到的是G1的分配信号的非。

图(b)电路中,G2A端加脉冲,芯片的输出端应得到的是G2A的分配信号。

4.22、用8选1数据选择器74LS151构成如习题4.22图所示电路,

(1)写出输出F的逻辑表达式,

(2)用与非门实现该电路;

(3)用译码器74LS138和与非门实现该电路。

习题4.22图

(1)由图可知输出F的逻辑函数表达式为:

(2)略

(3)当D=1时,

当D=0时,

用两片译码器和与非门实现如下:

或门

可由与非门实现

4.23、试用74LS151数据选择器实现逻辑函数。

。

GYW

C74LS151

AD7D6D5D4D3D2D1D0

(3)

F3

4.24、8选1数据选择器74LS151芯片构成如习题4.24图所示电路。

图中G为使能端,G=0时,芯片正常工作;

G=1时,Y=0(W=1)。

分析电路功能,写出电路输出函数F的表达式。

习题4.24图

由题所给逻辑电路图可知,输出逻辑函数表达式为:

4.25、试用中规模器件设计一并行数据监测器,当输入4位二进制码中,有奇数个1时,输出F1为1;

当输入的这4位二进码是8421BCD码时,F2为1,其余情况F1、F2均为0。

(1)根据题意列出真值表如下:

11

(2)由真值表得到输出逻辑函数表达式为:

(3)用74LS154实现逻辑函获数如图所示。

4.26、四位超前进位全加器74LS283组成如习题4.26图所示电路,分析电路,说明在下述情况下电路输出CO和S3S2S1S0的状态。

(1)K=0A3A2A1A0=0101B3B2B1B0=1001

(2)K=0A3A2A1A0=0111B3B2B1B0=1101

(3)K=1A3A2A1A0=1011B3B2B1B0=0110

(4)K=1A3A2A1A0=0101B3B2B1B0=1110

COS3S2S1S0

74LS283CI

A3B3A2B2A1B1A0B0

A3B3A2B2A1B1A0B0K

习题4.25图

(1)当K=0,A3A2A1A0=0101,B3B2B1B0=1001时,输出S3S2S1S0=1110,CO=0。

(2)当K=0,A3A2A1A0=0111,B3B2B1B0=1101时,输出S3S2S1S0=0100,CO=1。

(3)当K=1,A3A2A1A0=1011,B3B2B1B0=0110时,输出S3S2S1S0=0101,CO=1。

(4)当K=1,A3A2A1A0=0101,B3B2B1B0=1110时,输出S3S2S1S0=0111,CO=0。

4.27、试将74LS85接成一个五位二进制数比较器。

将74LS85接成一个五位二进制数比较器如图所示,输入两个五位二进制数分别为X4X3X2X1X0和Y4Y3Y2Y1Y0

4.28、试用74LS185实现六位二进制数到BCD码的码组转换电路。

用74LS185实现六位二进制数到BCD码的码组转换电路如图所示。

D5D4D3D2D1D0为六位二进制数的输入,B3B2B1B0A3A2A1A0为两位十进制数的8421码的输出。

74185

EN

22

44

88

1610

3220

40

80

D0

D1

D2

D3

D4

D5

B0

B1B2

B3

4.29、设每个门的平均传输延迟时间tpd=20ns,试画出习题4.29图所示电路中A、B、C、D及vO各点的波形图,并注明时间参数,设vI为宽度足够的矩形脉冲.

vI

vO

ο

习题4.29图

电路中A、B、C、D及vO各点的波形如图所示。

4.30、下列各逻辑函数中,其中无冒险现象的为:

A.

B.

;

C.

D.

.

由题可知,A式中无冒险现象。

4.31、TTL或非门组成的电路如习题4.31图所示。

(1)分析电路在什么时刻可能出现冒险现象?

(2)用增加冗余项的方法来消除冒险,电路应该怎样修改?

习题4.31图

(1)当A=1,B=D=0时,可能会出现冒险现象。

(2)电路在最后一个或非门的输入端增加一个

项。