EDA15实验报告打印部分Word文档格式.docx

《EDA15实验报告打印部分Word文档格式.docx》由会员分享,可在线阅读,更多相关《EDA15实验报告打印部分Word文档格式.docx(27页珍藏版)》请在冰豆网上搜索。

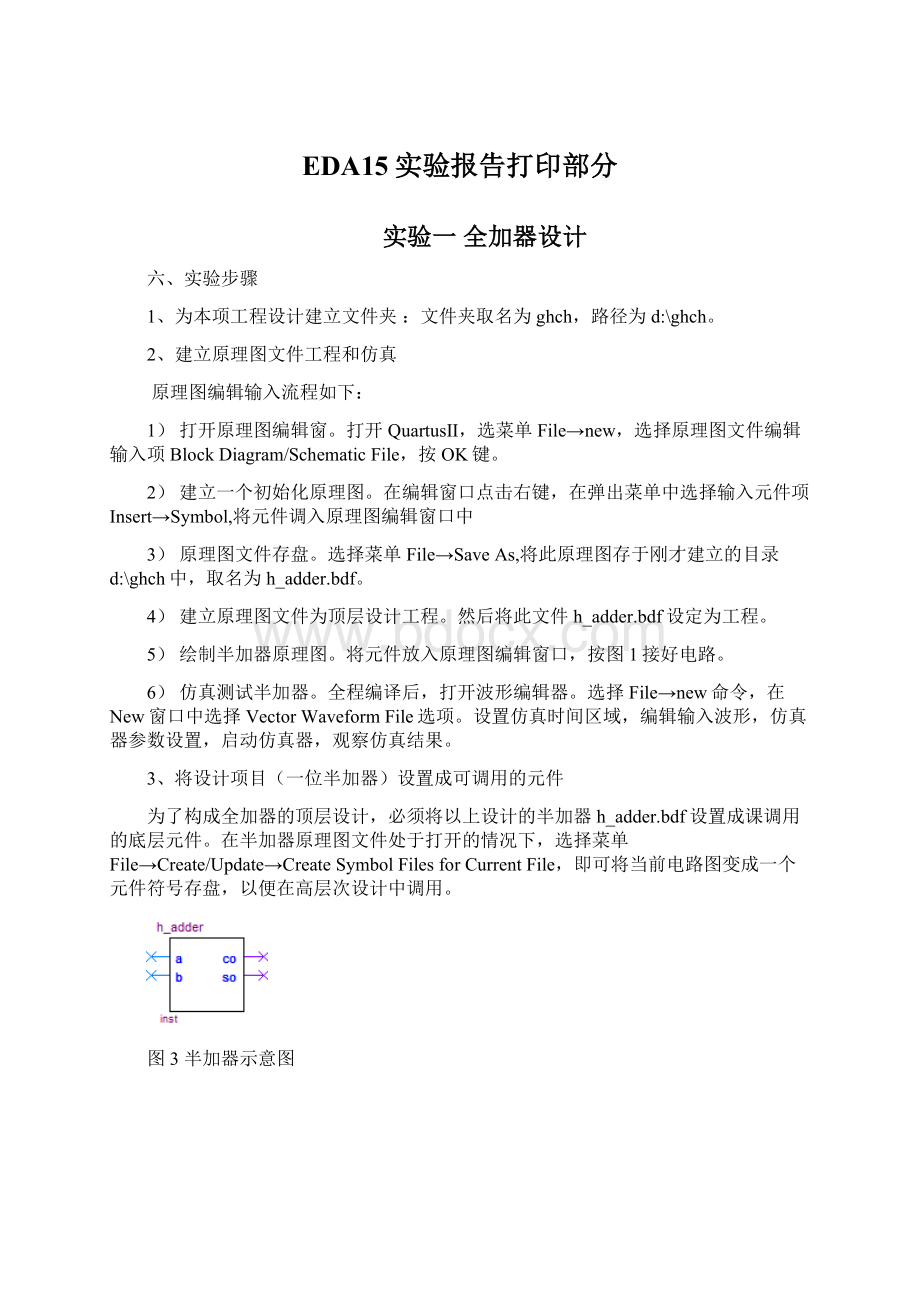

一位全加器的仿真波形图

4)仿真成功后得到了预期的设计效果后,将引脚锁定。

方法如下:

选择assignment中的pins,将To栏的信号锁定到相应的Location引脚列中。

引脚号对应关系可以从实验手册中查找,结果如图所示:

5)引脚锁定以后,再编译全程编译一次,然后编程下载,选择Tools->

programmer菜单,设计好编程硬件后点击Start开始下载。

6)下载成功后在硬件上检测设计思路的是否正确。

七、硬件测试结果

实验开关K1,K2,K3打开和关闭后LED灯可以按照表格要求亮暗,实验成功。

实验二模可变计数器设计

(四)实验程序

modulecount(clk,m,en,rst,SG,sel,led);

inputclk,m,en,rst;

//output[11:

0]q;

output[7:

0]SG;

output[2:

0]sel;

output[0:

0]led;

(*synthesis,keep*)regclk1;

(*synthesis,keep*)wire[3:

0]gw,sw,bw;

reg[3:

0]a;

reg[0:

reg[11:

0]model;

reg[7:

0]cnt,SG;

reg[2:

always@(posedgeclk)

begincnt=cnt+1;

if(cnt==200)beginclk1=1'

b1;

cnt=0;

end

elseclk1=1'

b0;

end//120分频,CLK为数码管扫描频率,CLK1为计数频率

always@(posedgeclk)

begin

if(sel<

6)sel=sel+1;

elsesel=4;

end//sel为数码管选择

always@(sel)begin

case(sel)

6:

a=gw;

//0数码管为个位

5:

a=sw;

//1数码管为十位

4:

a=bw;

//2数码管为百位

default:

a=0;

endcase

case(a)

0:

SG<

=8'

b00111111;

1:

b00000110;

2:

b01011011;

3:

b01001111;

b01100110;

b01101101;

b01111101;

7:

b00000111;

8:

b01111111;

9:

b01101111;

//8段译码值

SG=8'

b11111111;

endcase

always@(m)

if(m)model=12'

b000000001000;

//模值15

elsemodel=12'

b0000011100100;

//模值119

assigngw=q[3:

0];

assignsw=q[7:

4];

assignbw=q[11:

8];

always@(posedgeclk1,negedgerst)

begin

if(!

rst)q=0;

elseif(en)

if(q<

model)

if(gw==9)beginq=q+7;

if(sw==9)q=q+96;

end//BCD调整

elseq=q+1;

end

elseq=0;

always@(q)

if(q<

model)led<

=0;

elseled<

=1;

endmodule

(五)实验步骤

建立工作库文件和编辑设计文件

(1)在D盘新建一个文件夹用来保存工程文件

(2)打开QuartusⅡ软件,选择菜单File->

New->

VerilogHDLFile,点击OK后在打开的界面下输入已经设计好的程序。

(3)输入完程序后,保存文件选择菜单File->

Saveas,将文件保存到工程文件夹中,文件名不能含有中文字符,最好与程序实体名一样。

(4)保存好文件后,一般会提示是否新建一个工程,选择是,如果没有就在菜单打开File->

NewprojectWizard项,将出现工程项目建立向导。

(5)按照工程项目向导提示设计好工程中要用到的文件放到同一个工程文件夹中,选择实验中用到的芯片和第三方工具(一般默认EDA自带的工具箱,在这里不做任何选择)。

(6)完成工程项目建立后选择processing->

startcompilation或选择按钮开始全程编译,如果编译过程中出现错误或警告提示,则双击错误或警告提示就可以找到该错误或警告在设计文件的位置。

(7)在完成设计输入和综合编译以后,可以通过时序仿真来检查设计是否符合要求,这里我们可以通过建立波形文件(.vmf)。

在选择File->

VetorWaveformFile项后选择OK。

(8)设计Edit栏选择EndTime设计时间为50us,在View->

ulititywindows中选择NodeFinder或按Alt+1,然后将所有的输入输出拖到波形文件中,设计好输入时序和输出方式后保存文件。

选择processing栏中的Startsimulation或选择按钮开始波形仿真。

(9)仿真成功后得到了预期的设计效果后,将引脚锁定。

(10)引脚锁定以后,再编译全程编译一次,然后编程下载,选择Tools->

(11)下载成功后在硬件上检测设计思路的是否正确。

(六)仿真波形

编译仿真前波形设置,即输入设置:

仿真结果:

此时M=0,计数值q到111变重新开始计数。

此时M=1,计数值q到8变重新开始计数。

图中四个输入:

clk为时钟频率,en为与能端,高电频有效,rst为复位控制,低电频有效,m为模值改变,m=0,表示模值为111,m=1,表示模值为8。

输出q表示计数,实验成功。

(7)硬件测试结果

实验中调节K1打开为高电频,K2调节模值,并按下复位键开始计数,可以看到数码管上有数字在增加,当K2关闭,计数到111后重新0开始计数,当K2打开,计数到8后重新0开始计数。

实验成功。

实验三序列信号发生和检测计设计

五实验程序

modulex(clk,f,m,clr1,clr2,ld,s);

inputclk,clr1,clr2,ld;

outputf,m;

output[4:

0]s;

regf,m;

0]q2;

reg[4:

0]z,s;

reg[15:

0]wo;

parameter[15:

0]xulie=16'

b1011101000111011;

//要产生的序列

parameter[4:

0]q1=5'

b11101;

//要检测的序列

always@(posedgeclk,negedgeclr1)

if(~clr1)f<

//清产生序列

elseif(ld)wo<

=xulie;

elsebeginwo[0]<

=wo[15];

f<

wo[15:

1]<

=wo[14:

//并行转换为串行

always@(posedgeclkornegedgeclr2)

begin

if(~clr2)q2<

=0;

//清检测序列

else

case(q2)

0:

if(f==q1[4])q2<

elseq2<

1:

if(f==q1[3])q2<

=2;

2:

if(f==q1[2])q2<

=3;

3:

if(f==q1[1])q2<

=4;

=3;

4:

if(f==q1[0])q2<

=5;

//状态转移

q2<

always@(q2)

if(q2==5)m<

=1;

elsem<

//检测到11101,输出1

z[4:

1]=z[3:

z[0]=f;

s<

=z;

//转换为并行输出

(六)实验步骤

(七)仿真波形

由图知四个输入clk为1HZ频率,clr1,clr2为控制开关高电频正常工作,低电频载入数据,ld计数开关,低电频正常计数监测。

输出f为当前正在载入的序列值,m为监测到序列11101后为高电频,z,s显示正在检测的序列。

图可见,当z,s为11101时,m为高电频,仿真成功。

(八)硬件测试结果

实验开始按下复位键s1,s2,打上开关K3载入数据,再打下开关K3,开始正常工作,可以看到第七个LED显示f,前五个LED分别显示正在检测序列的五位,第八位显示m的值。

当第八位LED亮时,前五位LED显示正好是11101,经过实验代码调整,本实验在第八个LED不亮时,前五位全部不亮,当当第八位LED亮时,前五位LED显示11101,即亮亮亮暗亮。

实验四交通灯控制器设计

(四)实验程序

moduletraffic(S,clk,LED,COUNTER,LED1,sel);

inputclk;

regCPB;

//时钟

inputS;

reg[2:

//指明乡村路口是否有汽车的通行信号

reg[3:

output[5:

0]LED;

//信号灯的显示

0]LED1;

//显示时间的十位

output[8:

0]COUNTER;

//数码的显示

reg[5:

reg[7:

reg[35:

0]i;

regflag1;

regflag2;

0]cnt;

initial

flag2='

flag1='

COUNTER[7:

0]='

D60;

LED[5:

0]<

=6'

b001100;

//主干道是绿灯乡村道是红灯

end

if(cnt==100)beginCPB=1'

elseCPB=1'

always@(posedgeclk)

1)sel=sel+1;

elsesel=0;

always@(posedgeCPB)

if(COUNTER[3:

0]==4'

D0&

&

4]==4'

D0)//在数码管是60时判断是否有信号s的出现

if(S)

if(LED[5:

0]==6'

b001100)

b010100;

//表示主干道是黄灯而乡村是红灯

4]<

=4'

D0;

//显示的是4秒钟

COUNTER[3:

D4;

elseif(LED[5:

b010100)//表示4秒钟过后的乡村开始通路了

b100001;

//表示主干道是红灯而乡村是绿灯

D2;

//显示的是20秒钟

flag1=1'

0]=='

b100001)//表示20秒过后主干道通行了

='

b100010;

//表示主干道是红灯而乡村是黄灯

b100010)//表示即使s=1,20秒过后都要返源

D6;

//显示的是60秒钟

else

//表示可以开始进行20秒的检查是否乡村

b001100)

if(S&

(flag2=='

b1))//表示乡村道路有信号并且可以让乡村道路通行了

D0)//正常计数

4]=COUNTER[7:

4]-4'

D1;

0]=4'

D9;

0]=COUNTER[3:

0]-4'

if(flag1=='

b1)

if(!

S)

a=COUNTER[7:

a=COUNTER[3:

LED1[7:

LED1[7:

0]=8'

(10)引脚锁定以后,再编译