设计制作电子时钟.doc

《设计制作电子时钟.doc》由会员分享,可在线阅读,更多相关《设计制作电子时钟.doc(8页珍藏版)》请在冰豆网上搜索。

设计制作简易数字钟

一、设计要求

1、设计一振荡源,用于产生1Hz的脉冲信号;

2、能完成从00时00分00秒到23时59分59秒走时,并实时显示时、分、秒;

3、具有手动校时、校分、校秒功能。

发挥部分:

具有正点报时功能。

要求在59分58秒开始报时,持续5秒钟。

二、总体设计方案

1、方案选择数字钟实际上是由一个对标准频率(1HZ)进行计数的计数电路为主要部分构成的。

由于计数的起始时间不可能与标准时间(如北京时间)一致,故需要在电路上加一个校时电路,同时标准的1HZ时间信号必须做到准确稳定。

通常使用石英晶体振荡器电路来构成数字钟的标准时间基准信号。

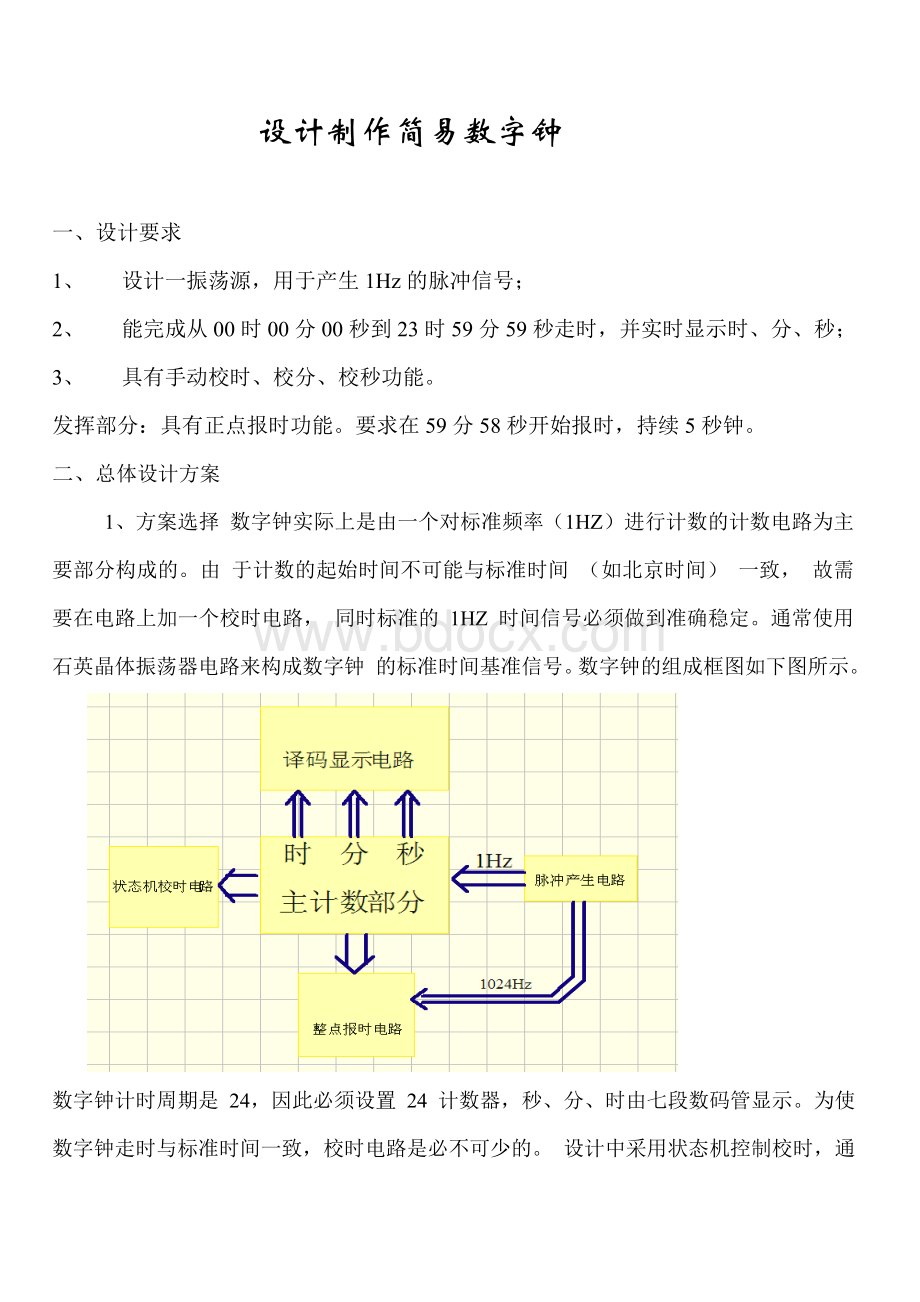

数字钟的组成框图如下图所示。

数字钟计时周期是24,因此必须设置24计数器,秒、分、时由七段数码管显示。

为使数字钟走时与标准时间一致,校时电路是必不可少的。

设计中采用状态机控制校时,通过切换开关用秒脉冲或手动按键产生脉冲先后对“时”“分”“秒”计数器进行校时操作。

2、数字钟的构成

(1)数字钟的构成:

振荡器、分频器、计数器、译码器、LED数码管显示器等几部分。

附加功能的实现还需采用T’触发器及与门和或门及蜂鸣器组成报时电路。

(2)数字钟的时、分、秒实际上就是由一个24进制计数器(00-23),两个60进制计数器(00-59)级联构成。

设计数字钟实际上就是计数器的级联。

(3)芯片选型:

由于24进制、60进制计数器均由集成计数器级联构成,且都包含有基本的十进制计数器,从设计简便考虑,芯片选择十进制计数器74LS390。

3、元器件列表:

型号74LS00、74LS04、74LS08、74LS21、74LS32、74LS47、74LS74、74LS86、74LS390、CD4068、CD4060、CD4511。

晶体管8050、510欧姆电阻、LED、轻触开关、自锁开关、蜂鸣器、10p电容、晶振32768、10M电阻。

三、系统工作原理

1、主计数部分原理图

图1主计数部分原理图

如图所示,用两个十进制计数器74LS390组成60进制计数器和24进制计数器,分别用于对分、秒和时的计数。

60进制计数器和24进制计数器均采用反馈清零法,当计数值到60或24时,其清零端CR=1,对计数值清零。

图中U11、U13、U15、U17A、U17B、Ui组成校时选通电路,用于选择校时位。

当校时控制信号 C1C2C3=111时,从分计数器来的溢出脉冲正常通过U13与门、U15异或门和U11非门,且相位与原进位溢出信号相同。

当C1C2C3=011时,与门Ui输出为零,U17A和U17B通过校时信号送至U15,因C1=0,故U13输出一直为零,将分溢出进位屏蔽,时计数信号为接入的校时信号。

后两级选通电路因C2C3=11,计数脉冲为正常时的脉冲信号(分计数脉冲来自秒溢出信号,秒计数脉冲为1Hz信号。

同理可知当 C1C2C3=101和C1C2C3=110时,可实现校分及校秒功能。

通过切换自锁开关还可选择校时信号来源,可为1Hz信号和手动按键产生的脉冲信号。

校时控制信号和脉冲产生信号由下面的电路产生。

2、信号产生电路及控制信号产生电路

图2控制信号和校时信号产生电路

本校时电路采用状态机校时方案,目地是只需通过一个按键便实现校时位选择功能。

状态机由RS触发器74LS74、74LS04和74LS21组成,它的四个状态分别为111、011、101、110,状态机输出接至上述主计数电路的C1C1C3输入端。

由上面的叙述知,这四个状态即可对时钟进行不校时、校时、校分和校秒操作。

状态机的状态改变由按键SS2实现,按键之后,状态机的输出便在四个状态之间转换。

按键S2用于对状态机的复位,按键S2后状态机的输出为111。

它的实用意义在于,当校时或校分而不需校其他位时,可直接按键S2,否则将通过按键SS2来使状态机回到111状态,这势必会对其他位的数值产生影响。

而设置复位按键后则不存在上述影响。

状态机状态转换表如下:

CP

RESET

当前状态(C1C2C3)

下一状态(C1C2C3)

↑

1

111

011

↑

1

011

101

↑

1

101

110

↑

1

110

111

x

0

xxx

111

按键SS1的作用是产生手动校时信号,用于手动校时。

图3秒脉冲及1024Hz信号产生电路

电路采用32768Hz晶振,经CD4060分频后输出2Hz信号,再由74LS74组成的D触发器对2Hz信号分频产生所需的1Hz秒脉冲信号。

从CD4060的5脚输出的1024Hz信号用于驱动整点报时电路中的蜂鸣器。

3、显示部分

显示部分由图1中的BCD译码电路和下图中的数码管组成。

由于所买器件的限制,译码器的时和分译码采用CD4511,秒译码采用74LS47。

对应的,数码管使用四个共阴数码管和两个共阳数码管。

译码器的输出接510欧姆限流电阻至数码管。

对于小时的显示,当数值不足10时,由于两个与门的输出为零,可将高位不需显示的0灭掉。

图4显示部分

4、整点报时电路

整点报时电路原理:

采用T’触发器。

在此之前U13C输出低电平,当计数至59分58秒时,U13C输出一高电平,对应的,US9的CLK输入端有一上升沿,从而触发器输出反转为高电平,打开UiB与门,蜂鸣器在1Hz和1024Hz信号的驱动下,有规律地鸣响。

当计数为00分03秒时,U13C输出一高电平,CLK再次出现一上升沿,输出反转为低电平,蜂鸣器关闭,从而实现整点5秒报时功能。

其中自锁开关SQ可控制蜂鸣器的开关,在不希望整点报时时关闭报时功能。

由于74芯片输出为高点平时的拉电流很小,不能直接驱动蜂鸣器,故还需加入一晶体管8050对输出扩流。

图5整点报时电路

四、制板及元件的安装调试

由于元件多,而且大多是芯片,加之数码管的布线困难,在第一次PCB布板失败后,我将原理图分为了三个部分——主计数部分、校时控制和信号产生部分及显示部分。

由于连线复杂,制作前两个部分时PCB采用了双面板。

制板后,焊接元件,由于元件多,而且过孔也多,焊接之后初次调试不成功,连基本的计数功能都不能实现。

我又用了几乎一天的时间来差错,共查出在顶层的三处漏焊。

用导线连接后,可以正常计数显示和报时。

原理图设计失误:

绘制原理图时误将74LS390的清零认为是低电平有效,从而导致对结果的手动清零功能未能实现,当按下主计数部分左侧的按键时,计数器的计数功能成为100进制计数器。

从理论上的改进如下图,平时键S1未按下,与非门 U0A输出为正常的清零信号,当按下S1时,不论U10C输出为什么,U0A输出均为高电平,从而实现手动

清零。

图6计数器的手动清零改进电路

五、心得体会

此时钟电路的原理图设计完全由自己完成,在设计的过程中遇到的问题都顺利解决了。

比如校时信号的选通电路和状态机的输出接入主计数器的方式。

通过此次设计制作,我对74系列和CD系列芯片的使用及电气特性有了更见深入的认识。

对这些芯片的常用应用电路也有了大致的认识。

动手方面,对于双面板的焊接方式和注意事项也了一定的了解。

这次在焊接时虽然漏焊了三个点,但是我还是通过不断的检查查处了错误所在,所以对这次课程设计的结果还是比较满意的。