ARM2体系结构Word文档下载推荐.docx

《ARM2体系结构Word文档下载推荐.docx》由会员分享,可在线阅读,更多相关《ARM2体系结构Word文档下载推荐.docx(34页珍藏版)》请在冰豆网上搜索。

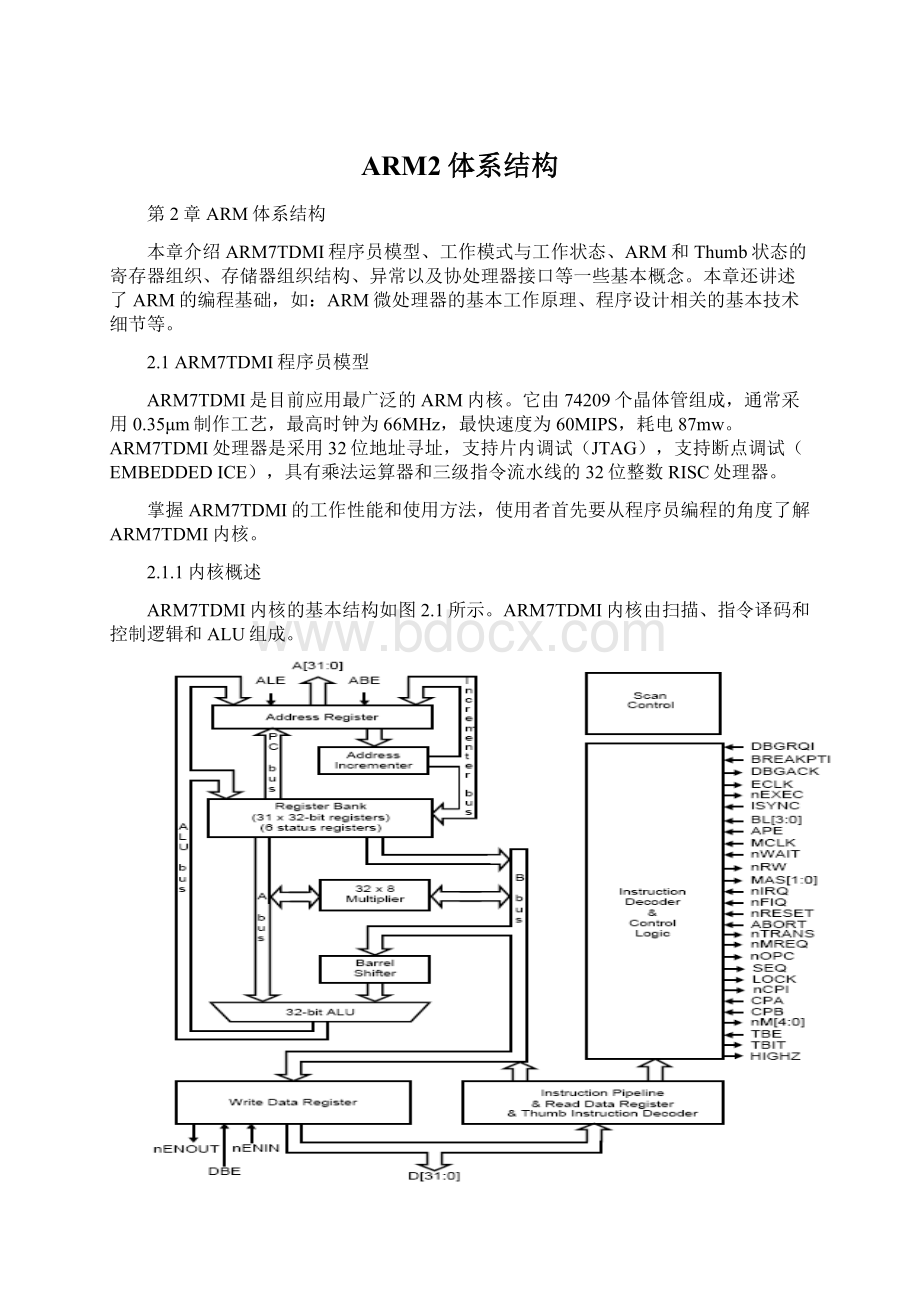

指令译码和控制逻辑包括指令流水线、Thumb指令译码器。

流水线技术是将每条指令分解为多步来执行,流水线方式是指把一个处理过程分解成若干个子过程,每个子过程可以与其他子过程同时进行,实现几条指令并行处理,以加速程序运行过程的技术。

流水线技术是通过增加计算机硬件来实现的,每条由各自独立的电路来处理,每完成一步,就进到下步,而前一步则处理后续指令。

采用流水线技术后,处理器并没有加速单条指令的执行,每条指令的操作步骤也不能少,由于多条指令的不同操作步骤同时执行,因而从总体上加快了指令流执行速度,缩短了程序执行时间。

在计算机的体系结构中,处理器包含指令部件I和指令执行部件E。

指令部件I负责完成指令取指、指令译码,指令执行部件E负责完成功能运算、结果保存。

计算机执行程序是按顺序执行的。

在一条指令中,可以分为三个部分,如图2.2所示:

取指令

译码

执行

图2.2指令执行过程

为了提高CPU的工作效率,ARM的控制器设计完全采用硬布线实现。

如图2.3所示,ARM把若干条指令在执行时间上重叠起来,使机器的执行速度大大加快。

I1取指令

I1译码

I1执行

I2取指令

I2译码

I2执行

I3取指令

I3译码

I3执行

图2.3流水线执行过程

从图2.3可以看出,指令部件完成第1条指令取指后,交给指令译码部件;

指令部件进行第2条指令的取指。

同理,译码部件完成第1条指令译码后,交给指令执行部件;

指令译码继续完成第2条指令的译码。

指令的整个执行过程相当于工业生产线上的流水作业,这种指令的处理机制称作指令流水线。

到目前为止,ARM核处理器的流水机制分为三级流水线、五级流水线和六级流水线(ARM11为八级流水线)。

ARM7采用三级流水线结构,分别是取指、译码和执行。

ARM9采用的是五级流水线结构,分别是取指、译码、执行、存储和回写。

ARM10采用的是六级流水线结构。

指令流水线遇到执行“跳转指令”时,指令流水线不能继续执行,自动清空指令流水线(如重新建立指令流水线需要2个或2个以上的指令周期),指令流水线需要重新建立。

为提高指令执行效率,ARM在指令设计上基本每条指令都采用条件执行。

执行含有条件的指令时,如条件不满足,相当指令一条NOP指令,指令流水线不清空。

ARM7TDMI执行使用3级流水线,第一级从内存中取回的指令,第二级开始译码,而第三级实际执行。

因此,程序计数器指针总是超出当前执行的指令两个指令,参见图2.3(在为分支指令计算偏移量时必须计算在内)。

在分支时ARM7TDMI将多花2个指令周期(因为流水线需要重新添满)。

所以最好利用条件执行指令来避免浪费周期。

例如:

...

CMPR0,#0

BEQfinish1

MOVR1,#1

MOVR2,#2

finish1

ARM7TDMI条件指令可以使系统执行更为有效:

MOVNER1,#1

MOVNER2,#2

Thumb指令译码器。

由于ARM内部只有一个32位运算器,为节约存储器空间,减少代码的存储空间,Thumb指令是将32位指令按照16位格式进行存储,在执行过程中,Thumb指令译码器把16位格式的指令还原成32位运算器能够执行的32位指令。

2.1.3运算器

ALU包含寄存器组、32*8乘法器、桶形移位器和32位的运算器。

本节简单介绍乘法器、桶形移位器和32位的运算器。

寄存器组将2.3节中介绍。

(1)32位的加法器

运算器不仅要实现加法运算,还必须实现指令集的所有指令。

它包括访问存储器的地址计算、跳转地址计算和位逻辑运算功能,ARM内核不采用微程序译码方式执行,采用完全的硬布线逻辑实现。

(2)桶形移位器

ARM7TDMI的运算指令包括两个操作数,第一个是寄存器,第二个可以是寄存器、立即数、或者是寄存器、立即数经过移位运算产生的操作数。

桶形移位器采用交叉开关,提供实现移位的硬件设备,减少数据的延时,提高指令的执行速度。

(3)32*8乘法器

ARM7TDMI支持64位结果乘法指令以及乘加指令。

乘法器是由硬件布线逻辑实现的,它采用著名的Booth改进电路,提高了乘法运行速度。

2.1.4内核接口信号

ARM7TDMI总线接口信号分为时钟信号、中断请求信号、总线控制信号、调试信号、边界扫描信号、处理器模式与状态信号、存储器接口信号、协处理器接口信号和电源等9类。

下面介绍各类主要信号:

1.时钟信号:

(1)MCLK(memoryclock)

输入信号。

ARM7TDMI、存储器及系统其它部件在MCLK时钟的控制下运行。

为获得地址原始的MCLK低电平定时信号,ALE须用MCLK的下降沿驱动成高电平信号,用MCLK的上升沿驱动成低电平信号。

ALE可以简单地反向MCLK信号得到,但是从MCLK得到ALE有延时,须特别注意。

(2)nWAIT(notwait)

nWAIT是由存储器或者外部设备给出的信号,可以用于延长总线周期。

当访问低速存储器或设备时,处理器将把访问时间延长若干个时钟周期,以等待低速存储器和设备的响应。

在ARM7TDMI内部,nWAIT与MCLK进行“与”操作,当nWAIT为高时,ARM7TDMI在MCLK的控制下运行。

在任何的多周期存储器访问时,nWAIT低电平保持到最终得到数据锁存。

(3)ECLK(externalclock)

ECLK是内核的输出信号,由MCLK扩展生成。

当调试内核时,ECLK是由TCK产生的DCLK信号。

2.中断请求信号:

(1)nIRQ(notinterruptrequest)

低电平有效。

如果nIRQ为低电平,将产生IRQ中断。

(2)nFIQ(notfastinterruptrequests)

低电平有效。

如果nFIQ为低电平将产生FIQ中断。

(3)ISYNC(synchronousinterrupt)

如果nIRQ和nFIQ与ARM核时钟同步,ISYNC为低电平;

如果ISYNC为高电平,要求nIRQ和nFIQ与ARM核时钟进行同步。

3.总线控制信号:

(1)nRESET(notreset)

nRESET为低电平导致正在执行的指令非正常执行。

nRESET为低电平时,处理器在复位处执行指令的虚拟预取。

如nRESET一直为低,处理器执行内部周期,同时地址自动从复位处增值,最终地址会产生溢出,地址为0。

当nRESET在低电平保持2个或2个以上时钟周期后,恢复为高电平一个时钟周期,ARM7TDMI将从地址0×

00重新开始执行。

(2)HIGHZ(highimpedance)

HIGHZ信号为高电平表示HIGHZ指令被加载到TAP控制器。

(3)nENIN(notenableinput)

在写周期,nENIN与nENOUT共同控制数据总线。

在简单的系统中,nENIN为低,nENOUT不定义。

在一些较复杂的应用系统中,nENIN允许外部系统操纵。

当外部设备驱动总线时,nENIN可用于信号延时。

(4)nENOUT(notenableoutput)

在数据写周期,nENOUT一直保持低电平。

在共享总线应用中,nENOUT信号可用作辅助仲裁。

(5)ABE(addressbusenable)

ABE输入为低电平,强迫地址总线进入高阻状态。

MAS[1:

0]、nRW、LOCK、nOPC和nTRANS信号也有类似的情况。

如果系统不要求禁止地址驱动,ABE应接到高电平。

(6)APE(addresspipelineenable)

当APE为高电平表示总线处于流水线方式,当APE为低电平,表示总线处于非流水线方式。

APE的电平要保持到存储器控制信号指明另一个非顺序访问结束。

地址总线、LOCK、nRW、MAS[1..0]、nOPC、和nTRANS与APE共同作用,以确定总线周期的类型。

系统可能包含DRAM和SRAM以及ROM。

为适应不同地址周期的需要,在MCLK为低时APE可以变换。

APE信号控制ARM7TDMI的地址总线可以在流水线方式或非流水线方式下操作。

APE信号的输入可以控制ARM7TDMI的地址总线形成流水线或取消流水线。

APE信号影响A[31:

0]、nRW、MAS[1:

0]、LOCK、nOPC和nTRANS信号。

作为地址译码的结果,APE由被访问的存储体驱动,APE信号需要保持到另一个非顺序访问周期。

通常,在同类存储器的猝发顺序访问中,APE保持为同一电平。

在只包含SRAM和ROM的系统中,在产生要求的地址时,APE总是保持低电平;

许多应用系统包含DRAM和SRAM/ROM,为适应不同的地址定时要求,在MCLK的低电平相位内,APE可以安全改变。

(7)ALE(adresslatchenable)

在非顺序周期里,地址译码需要加入一个等待状态,用于控制地址输出的锁存器,通常地址信号需要稳定,直到周期结束。

ALE为高电平,系统地址将保持不变。

它的作用与MAS[1:

0],nRW,LOCK,nOPC和nTRANS信号类似。

(8)DBE(databusenable)

在单向或双向总线数据输出时,DBE应为高电平。

DBE为低电平时,双向数据总线进入高阻状态,单向数据输出总线为高阻,无数据输出。

(9)TBE(testbusenable)

TBE是ARM7TDMI输出控制信号,通常TBE总是保持为高电平。

TBE控制信号在测试时使用。

当TBE为低电平时,数据总线D[31:

0]、地址总线A[31:

0]、LOCK、MAS[1:

0]、nRW、nTRANS和nOPC被强制为高阻状态。

由于TBE没有与之相关的扫描单元,因此允许外部信号在扫描测试期间被置为高阻状态。

4.调试信号:

(1)BREAKPT(breakpoint)

为了调试程序,BREAKPT信号允许外部设备停止处理器正在执行的程序。

BREAKPT为高,引起当前存储器访问的中断。

如对存储器的访问是取指,指令到达指令流水线,ARM7TDMI进入调试状态;

如对存储器的访问是存取数据,当前指令执行完成,ARM7TDMI进入调试状态。

BREAKPT信号允许扩充ICE类型的内部断点。

(2)