VHDL2008年答案文档格式.doc

《VHDL2008年答案文档格式.doc》由会员分享,可在线阅读,更多相关《VHDL2008年答案文档格式.doc(11页珍藏版)》请在冰豆网上搜索。

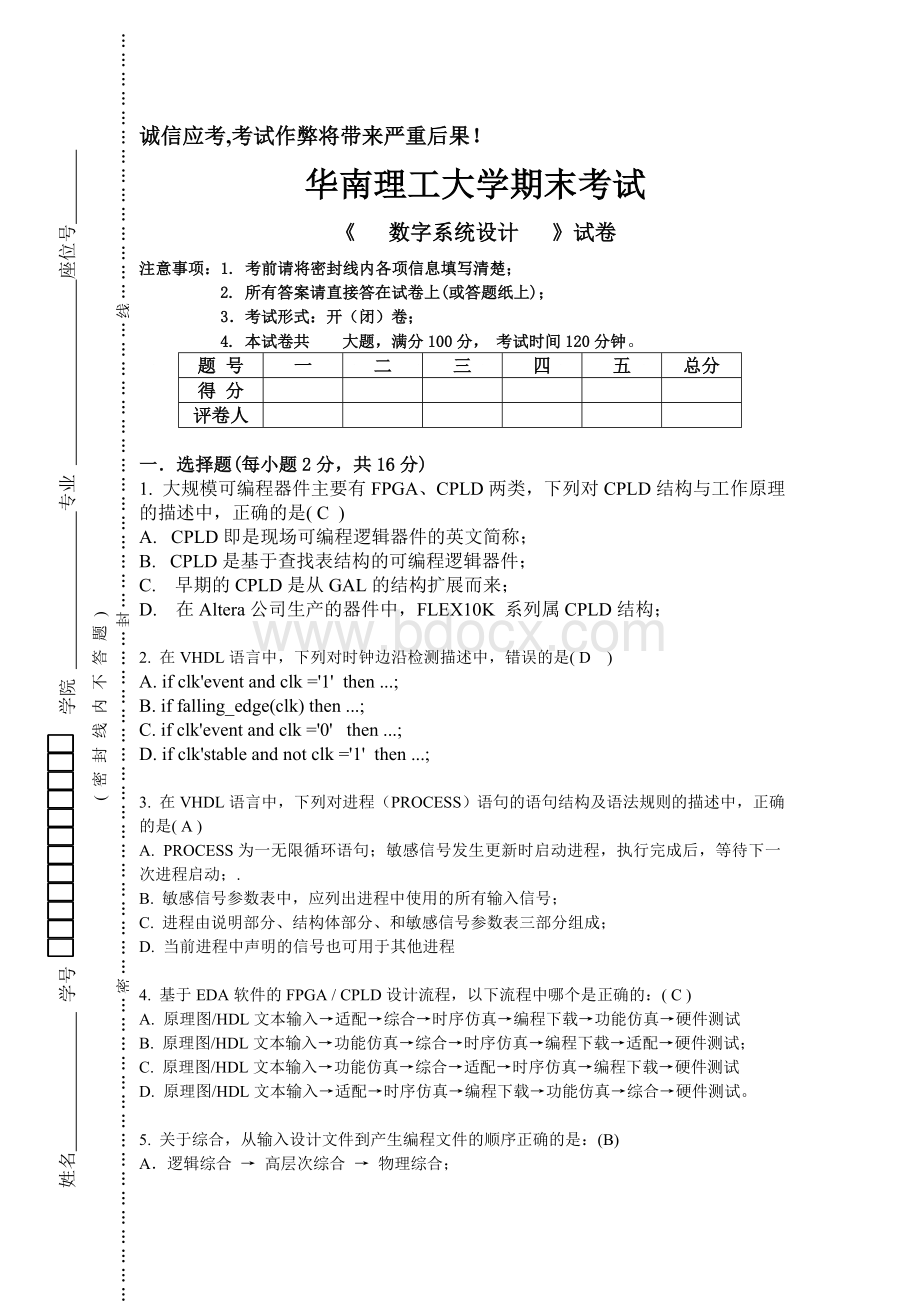

)

A.

CPLD即是现场可编程逻辑器件的英文简称;

B.

CPLD是基于查找表结构的可编程逻辑器件;

C.

早期的CPLD是从GAL的结构扩展而来;

D.

在Altera公司生产的器件中,FLEX10K系列属CPLD结构;

2.在VHDL语言中,下列对时钟边沿检测描述中,错误的是(

D)

A.ifclk'

eventandclk='

1'

then...;

B.iffalling_edge(clk)then...;

C.ifclk'

0'

D.ifclk'

stableandnotclk='

3.在VHDL语言中,下列对进程(PROCESS)语句的语句结构及语法规则的描述中,正确的是(

A)

A.

PROCESS为一无限循环语句;

敏感信号发生更新时启动进程,执行完成后,等待下一次进程启动;

.

B.敏感信号参数表中,应列出进程中使用的所有输入信号;

C.进程由说明部分、结构体部分、和敏感信号参数表三部分组成;

D.当前进程中声明的信号也可用于其他进程

4.基于EDA软件的FPGA/CPLD设计流程,以下流程中哪个是正确的:

(

C)

A.原理图/HDL文本输入→适配→综合→时序仿真→编程下载→功能仿真→硬件测试

B.原理图/HDL文本输入→功能仿真→综合→时序仿真→编程下载→适配→硬件测试;

C.原理图/HDL文本输入→功能仿真→综合→适配→时序仿真→编程下载→硬件测试

D.原理图/HDL文本输入→适配→时序仿真→编程下载→功能仿真→综合→硬件测试。

5.关于综合,从输入设计文件到产生编程文件的顺序正确的是:

(B)

A.逻辑综合→高层次综合→物理综合;

B.高层次综合→逻辑综合→物理综合;

C.物理综合→逻辑综合→高层次综合;

D.高层次综合→逻辑综合→时序综合;

6.进程中的信号赋值语句,其信号更新是(

A.按顺序完成;

B.比变量更快完成;

C.在进程的挂起时完成;

D.都不对。

7.下列不属于VHDL基本程序结构是(A)

A.CONFIGURATION定义区

B.ARCHITECTURE定义区

C.USE定义区

D.ENTITY定义区

8.下面对利用原理图输入设计方法进行数字电路系统设计,那一种说法是不正确的_(C)。

A. 原理图输入设计方法直观便捷,但不适合完成较大规模的电路系统设计;

B. 原理图输入设计方法一般是一种自底向上的设计方法;

C. 原理图输入设计方法无法对电路进行功能描述;

D. 原理图输入设计方法也可进行层次化设计。

二.简答题(22分)

1.简述利用EDA技术设计数字系统的特点。

1) 用软件的方式设计硬件;

2) 用软件方式设计的系统到硬件系统的转换是由有关的开发软件自动完成;

3) 采用自顶向下的设计方法;

4) 设计过程中可用有关软件进行各种仿真;

5) 系统可现场编程,在线升级;

6) 整个系统可集成在一个芯片上,体积小、功耗低、可靠性高。

2.什么是信号建立时间?

(2分)什么是信号保持时间?

(2分)

建立时间是指在触发器的时钟信号上升沿到来以前,数据稳定不变的时间。

保持时间是指在触发器的时钟信号上升沿到来以后,数据稳定不变的时间。

3.仿真分为哪几个层次的仿真?

(3分)

1) 电路级仿真;

2) 逻辑仿真;

3) 开关级仿真;

4) 算法仿真

4.实验中,对某程序进行编译时出现错误提示:

“VHDLDesignFile“aaa.vhd”mustcontainanentityofthesamename.”(4分)

这是什么原因?

如何修改?

产生这个错误的原因是ENTITY的名字与VHDL文件名字不一样。

只需要把ENTITY的名字改为“aaa”或者把“aaa.vhd”改成ENTITY的名字就可以了。

5.实验中,如果编译时出现“Can’topenVHDL“WORK””这样的错误提示。

这又是什么原因,如何修改?

(4分)

出现这个错误的原因是把VHD文件直接放在了硬盘根目录下,只需要建立一个文件夹就可以解决。

6.用图示法描述一般时序系统的模型,并作简要说明。

组合逻辑

电路

存储器

输入

现态

输出

次态

时序电路的一般模型,由组合逻辑电路&具有记忆功能的存储器组成。

系统的当前状态保存在存储器或寄存器中,组合逻辑也可以分为次态产生逻辑与输出逻辑两部分。

系统的次态由系统的当前状态与输入有关,同样地,系统的输出也是由存储器的状态与输入信号一起决定的。

三.根据下述VHDL程序段,画出相应的逻辑示意图,并加以简单说明(共10分,每题5分)。

1、Process(clk)

Begin

If(clk=‘1’)thenQ<

=data;

Endif;

Endprocess;

这是一个D触发器。

2、ENTITYexampleIS

PORT(a,b,c,g1,g2a,g2b:

INstd_logic;

y:

OUTstd_logic_vector(7DOWNTO0));

ENDENTITY;

ARCHITECTUREbehavOFexampleIS

SIGNALindata:

std_logic_vector(2DOWNTO0);

BEGIN

indata<

=c&

b&

a;

PROCESS(indata,g1,g2a,g2b)

BEGIN

IF(g1='

andg2a='

ANDg2b='

)THEN

CASEindataIS

WHEN"

000"

=>

y<

="

11111110"

;

001"

11111101"

010"

11111011"

011"

11110111"

100"

11101111"

101"

11011111"

110"

10111111"

111"

01111111"

WHENOTHERS=>

y<

XXXXXXXX"

ENDCASE;

ELSE

y<

11111111"

ENDIF;

ENDPROCESS;

ENDbehav;

这是一个三八线译码器。

a

b

c

g1

四.综合题(52分)

1.根据原理图写出相应的VHDL程序:

(10分)

LIBRARYieee;

USEieee.std_logic_1164.all;

ENTITYproblem4IS

PORT(DIN,CLK:

INstd_logic;

QOUT:

OUTstd_logic);

ENDproblem4;

ARCHITECTUREbehaveOFproblem4IS

SIGNALQ:

std_logic;

DFF:

PROCESS(CLK)

IF(CLK'

eventANDCLK='

)THENQ<

=DIN;

ENDIF;

ENDPROCESS;

LATCH:

PROCESS(Q,CLK)

IF(CLK='

)THENQOUT<

=NOTQ;

ENDbehave;

2.有一个传输门,根据下述赋值语句和给定的波形,画出对应Z1,Z2,Z3和Z4的波形图。

(1)Z1<

=Vi,惯性延时时间为4ns

(2)Z2<

=Viafter4ns,惯性延时时间为4ns

(3)Z3<

=TRANSPORTViAFTER3ns,惯性延时时间为4ns

(4)Z4<

=Vi,传输门的Tr=4ns,Tf=2ns

3.根据ASM图画出时序图。

4.下面的ASM图含有多少个状态单元,用虚线框加以表示(2分)。

并用双进程状态机描述,请在空白处填入合适语句,使程序完整正确。

(8分)

Entitytrafficis

Port(reset,clk:

instd_logic;

car,timed:

major_green,minor_green:

outstd_logic);

endentity;

Architectureasmoftrafficis

typestateis(G,R);

signalpresent_state,next_state:

state;

seq:

process(reset,clk)

begin

if(reset='

)then

present_state=G;

elsif(clk'

eventandclk='

)then

present_state=next_state;

endif;

endprocess;