数字电子技术试题Word文档格式.docx

《数字电子技术试题Word文档格式.docx》由会员分享,可在线阅读,更多相关《数字电子技术试题Word文档格式.docx(13页珍藏版)》请在冰豆网上搜索。

(D)10μs

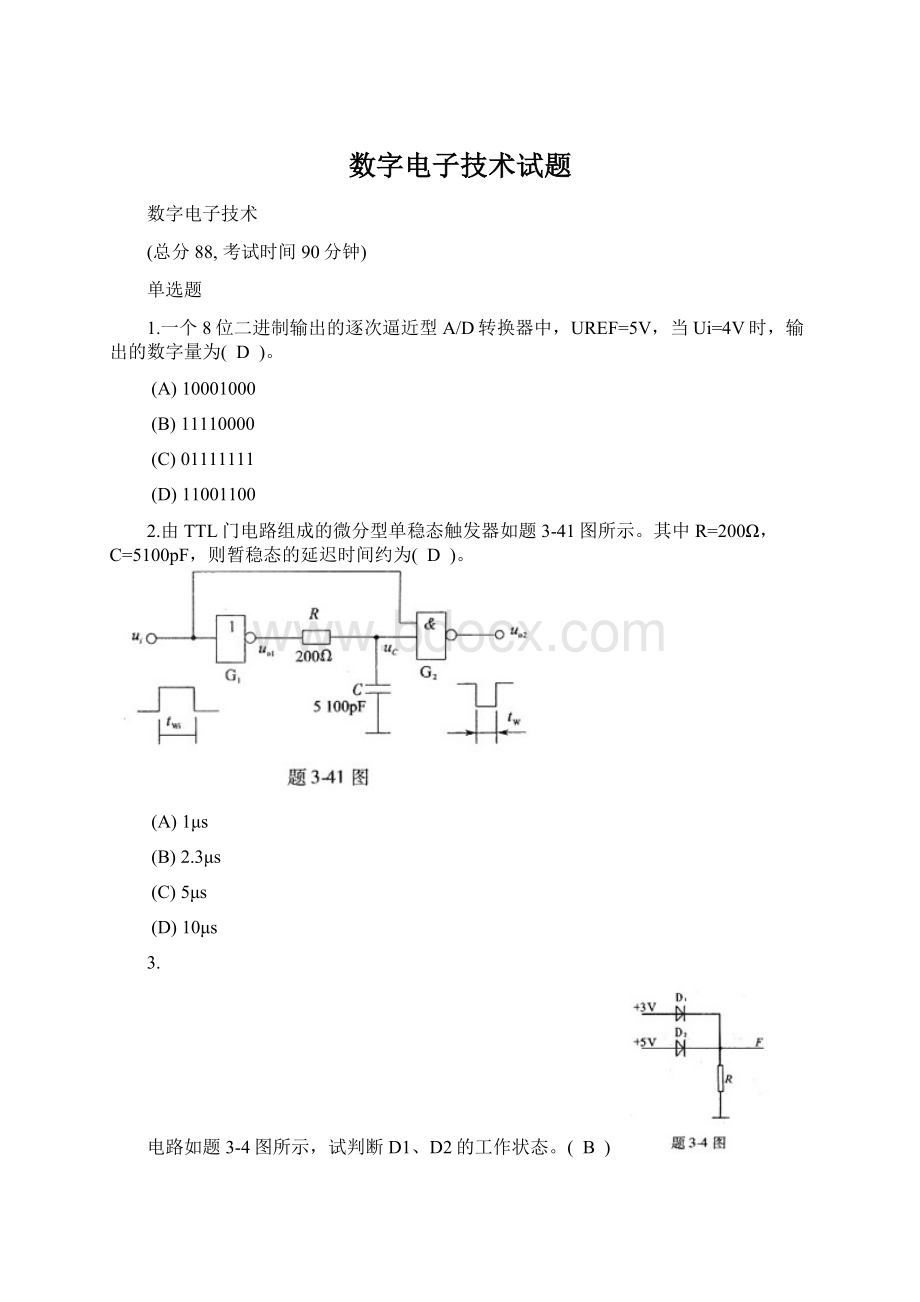

3.

电路如题3-4图所示,试判断D1、D2的工作状态。

(

B

)

(A)D1导通,D2截止

(B)D1截止,D2导通

(C)D1导通,D2导通

(D)D1截止,D2截止

4.一个三极管的发射结处于正向偏置,集电结也处于正向偏置,则该三极管工作在(

A

)状态。

(A)饱和

(B)截止

(C)放大

(D)不能确定

5.TTL与非门的3输入端A、B、C,在C输入端接一电阻到地,要实现,RA的取值应(

(A)小于200Ω

(B)大于2kΩ

(C)小于2kΩ

(D)可以任意取值

6.电路如题3-28图所示,设触发器的初始状态为0,其在输入A和CP脉冲作用下输出Q端的波形为(

7.如题3-26图所示电路,设初始状态Q=0,其在CP脉冲作用下输出Q端的波形为(

8.由8选1数据选择器组成的三变量逻辑函数发生器电路如题3-19图所示,该电路所产生的逻辑函数为(

9.由3-8译码器和8选1数据选择器组成的电路如题3-20图所示,3-8译码器输入的三位二进制数为A=A2A1A0,8选1数据选择器输入的三位二进制数为B=B2B1B0,输出为F,该电路的逻辑功能为(

C

(A)数据选择器

(B)数据分配器

(C)同比较器

(D)译码器

10.十进制数的“5”,用余3码表示为(

(A)1000

(B)1011

(C)0110

(D)0101

11.某组合逻辑电路的工作波形如题3-21图所示,其中A、B、C是电路的输入端,F是输出端,该电路的输出F的函数表达式和逻辑功能为(

12.以下几种说法中,正确的是(

(A)一个逻辑函数的全部最小项之和恒等于0

(B)一个逻辑函数的全部最大项之和恒等于0

(C)一个逻辑函数的全部最小项之积恒等于1

(D)一个逻辑函数的全部最大项之积恒等于0

13.下列几种说法中与BCD码的性质不符的是(

(A)BCD码是一种人为选定的0~9十个数字的代码

(B)一组四位二进制数组成的码只能表示一位十进制数

(C)BCD码有多种

(D)BCD码是一组四位二进制数,能表示16以内的任何一个十进制数

14.四位R—2R的T形网络D/A转换器如题3-43图所示,当参考电压UREF=10V,数字量输入D3D2D1D0=1000时的输出电压为(

(A)5V

(B)8V

(C)-5V

(D)-8V

15.函数的最简与或式为(

(A)1

(B)0

(C)AB

(D)

16.由4位二进制同步计数器74LS161和与非门组成的电路如题3-32图所示,其中S1、S2为使能端,Q0~Q3为输出,CP为计数脉冲输入,为置位输入端,试判断该电路为(

)进制计数器。

(A)十进制计数器

(B)五进制计数器

(C)十一进制计数器

(D)十六进制计数器

17.由JK触发器组成的电路如题3-33图所示,试判断该电路的逻辑功能是(

(A)同步二进制加法计数器

(B)同步二进制减法计数器

(C)异步二进制加法计数器

(D)异步二进制减法计数器

18.用n级触发器组成的计数器,其最大计数模是(

(A)n

(B)2n

(C)n2

(D)2n

19.微分型单稳态触发器如题3-40图所示。

其中R=390Ω,C=0.01μF,则暂稳态的延迟时间为(C

(A)6.9μs

(B)3.9μs

(C)2.73μs

(D)12μs

20.函数(

(A)相等

(B)互为反函数

(C)互为对偶式

(D)答案都不正确

21.JK触发器连接如题3-25图所示,其在CP脉冲作用下,Q端的输出波形为(

22.TTL与非门的关门电平为0.7V,开门电平为1.9V,当输入低电平为0.4V,输入高电平为3.2V时,输入高电平噪声容限为(

(A)1.1V

(B)1.3V

(C)1.2V

(D)1.5V

23.由与非门构成的RC环形多谐振荡器如题3-37图所示,当n=101时,振荡周期为10.1μs,则每个与非门的平均传输延迟时间tdp为(

)ns。

(A)10

(B)20

(C)25

(D)50

24.组合电路如题3-23图所示,该电路的逻辑功能是(

(A)数据选择器

(B)译码器

(C)数据分配器

(D)编码器

25.逻辑函数的标准或与式是由(

)构成的逻辑表达式。

(A)最大项之积

(B)最小项之积

(C)最大项之和

(D)最小项之和

26.由异或门组成的电路如题3-18图所示,A、B、C、D为输入二进制代码,F为输出,该电路具有(

)逻辑功能。

(A)偶校验电路

(B)奇校验电路

(C)数值比较器

(D)数据分配器

27.由D触发器组成的电路如题3-35图所示,该电路的状态转换图为(

28.TTL门电路如题3-7图所示,能够完成F=AB的电路是(

29.逻辑函数的最简或与式是(

30.一个触发器的状态转换图如题3-27图所示,则该触发器为(

(A)RS触发器

(B)T触发器

(C)JK触发器

(D)D触发器

31.某电路的输入、输出波形如题3-11图所示,该电路所实现的逻辑函数表达式为(

(A)F=AB

(B)F=A+B

(C)

32.RC环形多谐振荡器如题3-39图所示,当R=1kΩ,C=0.01μF时,其振荡频率约为(

(A)100kHz

(B)143kHz

(C)84kHz

(D)43.5kHz

33.由D触发器组成的电路如题3-34图所示,试判断该电路的逻辑功能是(

(A)同步二进制加法计数器

(B)同步二进制减法计数器

34.四位移位寄存器,现态为0111,经右移一位后其次态为(

(A)0011或1011

(B)1111或1110

(C)1011或1110

(D)0011或1111

35.逻辑函数的反函数为(

36.若将一异或门(输入端为A、B)当做反相器使用,则A、B端应(

)连接。

(A)A或B中有一个接1

(B)A或B中有一个接0

(C)A和B并联使用

(D)不能实现

37.一个移位寄存器原来的状态为0000,如果串行输入始终为1,则经过4个移位脉冲后寄存器的内容为(

(A)0001

(B)0111

(C)1110

(D)1111

38.八位DAC电路可分辨的最小输出电压为10mV,则输入数字量为(10000000)2时,输出电压为(

(A)2.56V

(B)1.28V

(C)1.27V

(D)2.55V

39.CMOS门电路如题3-9图所示,设二极管具有理想特性,其输出F的逻辑表达式为(

40.能起定时作用的电路是(

(A)施密特触发器

(B)单稳态触发器

(C)多谐振荡器

(D)译码器

41.把50Hz的正弦波变成周期性变化的矩形波,应选用(

)电路。

42.由3-8译码器和与非门构成的组合电路如题3-24图所示,输入A、B、C为二进制代码,输出为F1和F2该电路具有的逻辑功能是(

(B)全加器

(C)数据比较器

43.组合逻辑电路如题3-22图所示,该电路的逻辑功能是(

(A)三变量多数表决电路

(B)三变量非一致电路

(C)三变量一致电路

(D)三变量奇校验电路

44.如题3-10图所示电路,该电路的输出F的逻辑表达式为(D