自考计算机系统结构试题及答案解析Word格式.docx

《自考计算机系统结构试题及答案解析Word格式.docx》由会员分享,可在线阅读,更多相关《自考计算机系统结构试题及答案解析Word格式.docx(8页珍藏版)》请在冰豆网上搜索。

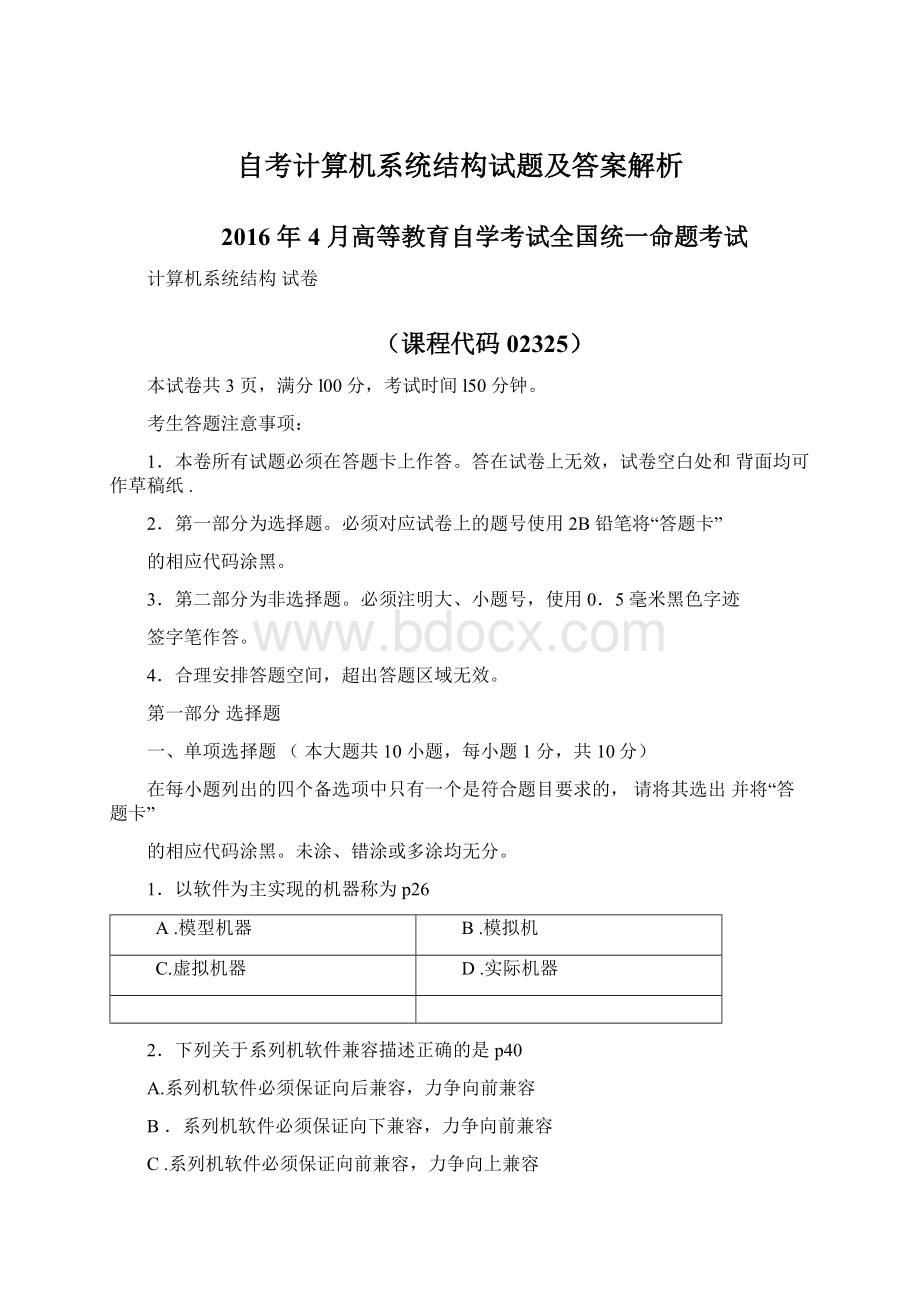

C.虚拟机器

D.实际机器

2.下列关于系列机软件兼容描述正确的是p40

A.系列机软件必须保证向后兼容,力争向前兼容

B.系列机软件必须保证向下兼容,力争向前兼容

C.系列机软件必须保证向前兼容,力争向上兼容

D.系列机软件必须保证向下兼容,力争向后兼容

3.浮点数阶值采用二进制p位、尾数基值位rm,则该浮点数的最大阶值

为p63

A.2p

B.2p-1

C.2p-1

D.2p-1-1

4.为了使任何时候所需的信息都只用一个存储周期访问到,信息在主存中存放的地址要求是p73

A.地址最低位为0B.地址最高位为0

D.该信息宽度的整

C.该信息宽度的一半

数倍

5.存储器的最大频宽是指p98

A.存储器瞬时访问的频宽

B.存储器最大的传输速率

C.存储器连续访问时的频宽

D.存储器的实际传输速率

6.总线控制定时查询方式的控制线的线数为p111

.周期

C.速度

9.并行向量处理的互联网络是

A•交换幵关B.纵横交叉幵关

C.单总线D.多总线

10.从指令和数据的多倍性来看,阵列机属于

A•单指令流单数据流

B•单指令流多数据流

C•多指令流单数据流

D•多指令流多数据流

第二部分非选择题

二、填空题(本大题共10小题,每小题2分,共20分)

请在答题卡上作答。

11.软件的功能可以用_硬件或—固件实现。

12.指令由—操作码和—地址码两部分组成。

p75

13.计算机应用可归纳为向上升级的4类:

数据处理、—信息处理、

__知识处理和智能处理。

p44~p45

14.浮点数下溢处理的精度损失对__系统程序和__应用程

序设计者都是透明的。

p69

15.适当选择好Cache的容量、块的大小、组相联的_组数和组内

的_块数,可以保证有较高的命中率。

16.能够并行读出多个CPU字的单体多字和—多体单字、—多体多

字的交叉访问主存系统被称为并行主存系统。

p100

17.中断系统的软、硬件功能分配实质上是中断_处理程序软件和

中断_响应硬件的功能分配。

p107

18.页式存储是把_主存空间和_程序空间都机械地等分成固

定大小的页,按页顺序编号。

p131

19.主存空间数据相关是相邻两条指令之间出现对主存

_同一单元要求__先写而后读的关联。

20.将二维数组中各元素在存储器中_错位存放可以使行或列的各

元素都能并行访问,但会造成_主对角线上各元素的并行访问冲突。

三、简答题(本大题共5小题,每小题6分,共30分)

21.简述指令字格式优化的措施。

p80

答:

⑴采用扩展操作码,并根据指令的频度Pi的分布状况选择适合的

编码方式,以缩短操作码的平均码长;

⑵采用多种寻址方式,以缩短地址码的长度,并在有限的地址长度内提供更多的地址信息;

⑶采用0、1、2、3等多种地址制,以增强指令的功能;

⑷在同种地址制内再采用多种地址形式,让每种地址字段可以有多种长度,且让长操作码与短操作码进行组配;

⑸在维持指令字在存储器中按整数边界存储的前提下,使用多种不同的指令字长度。

22.简述引入数据表示的原则。

p61

⑴看系统的效率是否有显着提高,包括实现时间和存储空间是否有显着减少;

实现时间是否减少又主要看主存和处理机之间传递的信息量是否减少;

⑵看引入这种数据表示后,其通用性和利用率是否提高。

如果只对某种数据结构的实现效率高、而对其他数据结构的实现效率低,或应用较少,将导致性价比下降。

23.简述数组多路通道的数据传输方式。

p119

K个字节的

数组多路通道在每选择好一台设备后,要连续传送完固定

成组数据后,才能释放总线,通道再去选择下一台设备,再传送该设备的

K个字节。

如此,以成组方式轮流交叉地为多台高速设备服务。

设备要想

传送N个字节,就需要先给厂N/K「次申请使用通道总线才行。

24.简述机群系统相对于传统的并行系统的优点。

答:

⑴系统有高的性能价格比;

⑵系统的开发周期短;

⑶系统的可扩展性好;

⑷系统的资源利用率高;

⑸用户投资风险小;

⑹用户编程方便。

25.简述SIMD系统的互连网络的设计目标。

⑴结构不要过于复杂,以降低成本;

⑵互联要灵活,以满足算法和应用的需求;

⑶处理单元间信息交换所需传送步数尽可能少,以提高速度性能;

⑷能用规整单一的基本构件组合而成,或经多次通过或多级连接来实现复

杂的互联,使模块性好,以便于用VLSL实现并满足系统的可扩展性。

四、简单应用题(本大题共2小题,每小题10分,共20分)

26.给出N=8的蝶式变换,如图题26图所示。

⑴写出互连函数关系。

⑵如果采用omega网络,需几次通过才能完成此变换?

0。

1。

2。

3。

4。

6。

7。

。

7

题26图

解:

⑴互联函数关系:

f(P2PlPo)=PoPlP2

⑵如果处理单元设有屏蔽位控制硬件,可让PE0、PE2、PE5和PE7均处于屏

蔽,

PE、PE3、PE4和PE6为活跃,只需要在omega网络上通过一次,传输路径无冗余。

如果处理单元未设置屏蔽位控制硬件,就需要在omega网络上通过两次,

此时,传输路径就会出现很多冗余。

27.由3位数(其中最低位为下溢处理的附加位)经ROM查表舍入法,下溢

处理成2位结果,设计使下溢处理平均误差接近于0的ROM表,列出ROM

编码表的地址与内容的对应关系。

3位数的ROM下溢处理表共有23=8个地址,地址码为000〜111,每个

地址存放一个处理结果

下溢处理平均处理误差接近于0的ROM处理表如图27所示

地址

000

001

010

011

100

101

110

111

内容

00

01

10

11

图27

五、综合应用题(本大题共2小题,每小题10分,共20分)

28.如果通道在数据传送期中,选择设备的时间T5为10卩s,传送一个字

节数据需要的时间Td为口so

(1)某低速设备每隔500卩s发出一个字节数据请求,至多可接几台这种设备?

(2)对于题28表所示的低速设备,一次通信传送的字节数不少于1024

个字节,则哪些设备可挂?

哪些设备不可挂?

设备

A

B

C

D

E

F

设备速

率

fi/B•

-1

口s

1/

题28表A~F设备的速率

⑴低速设备每隔500卩?

发出一个字节的数据传送请求,挂低速设备的通道应按字节多路通道方式工作,极限流量:

f=1/(Ts+Td)

如果所挂的台数为m设备的速率fi实际就是设备发出的字节传送请求的间隔时间的倒数,相同设备,速率之和为mfi。

为了不丢失信息,应满

足:

1/(Ts+Td)>

mfi

于是m应满足:

me1/(Ts+Td)•fi=500/(10+)=48

所以至多可挂48台低速设备。

如题曲表蔚示呀低理设备,此通逆能选择迪道"

如采诵肃上挂曆E台设备我g逸择遥道的扱限流建为:

3和(爲*氏〕空寸垃+0J廿丿

般制通進上所挂的设备速率

X—血•遁7泸事询站仃分)

+0.5

扛

即』W1.96B(J分)

根据題湖去耳知.只齟挫讥E』设备M分口设备因为速率暑过馬所以不船挂④(】分〉

29.有以下FORK、JOIN写成的在多处理机上并行执行的程序:

10U=A+B

FORK30

20V二U/B

JOIN2

GOTO40

30W=A*U

40FORK60

50X=W-V

GOTO70

60Y=W*U

70Z=X/Y

假设现为两台处理机,除法速度最慢,加、减法速度最快,画出该程序在

两台处理机上运行时的资源时空图。

如答29图。

址理机

C?

Ul

30