PLL原理要点Word格式文档下载.docx

《PLL原理要点Word格式文档下载.docx》由会员分享,可在线阅读,更多相关《PLL原理要点Word格式文档下载.docx(32页珍藏版)》请在冰豆网上搜索。

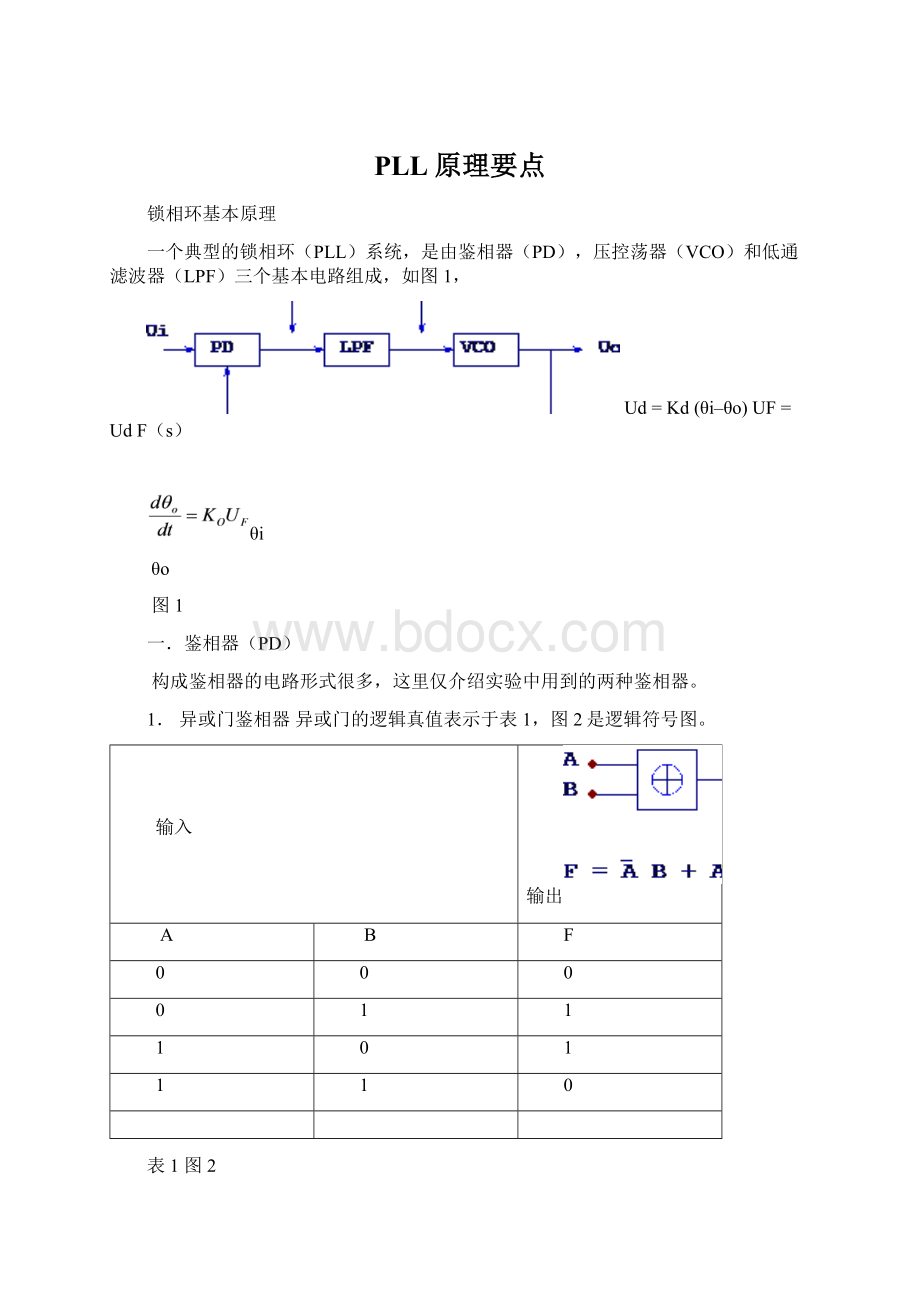

占空比与θ有关,见图3。

将F输出波

形通过积分器平滑,则积分器输出波形

的平均值,它同样与θ有关,这样,我

们就可以利用异或门来进行相位到电压θ

的转换,构成相位检出电路。

于是经积图3

分器积分后的平均值(直流分量)为:

U

U=Vdd*θ/

(1)Vcc

不同的θ,有不同的直流分量Vd。

θ与V的关系可用图4来描述。

从图中,两者呈简单线形关1/2Vcc

系:

Ud=Kd*θ

(2)

1/2ππθ

Kd为鉴相灵敏度图4

2.边沿触发鉴相器前已述及,异或门相位比较器在使用时要求两个作比较的信号必须是占空比为50%的波形,这就给应用带来了一些不便。

而边沿触发鉴相器是通过比较两输入信号的上跳边沿(或下跳边沿)来对信号进行鉴相,对输入信号的占空比不作要求。

二.压控振荡器(VCO)

压控振荡器是振荡频率ω0受控制电压UF(t)控制的振荡器,即是一种电压——频率变换器。

VCO的特性可以用瞬时频率ω0(t)与控制电压UF(t)之间的关系曲线来表示。

未加控制电压时(但不能认为就是控制直流电压为0,因控制端电压应是直流电压和控制电压的叠加),VCO的振荡频率,称为自由振荡频率ωom,或中心频率,在VCO线性控制范围内,其瞬时角频率可表示为:

ωo(t)=ωom+K0UF(t)

式中,K0——VCO控制特性曲线的斜率,常称为VCO的控制灵敏度,或称压控灵敏度。

三.环路滤波器

这里仅讨论无源比例积分滤波器如图5。

其传递函数为:

式中:

τ1=R1C

τ2=R2C

图5

四.锁相环的相位模型及传输函数

图6

图6为锁相环的相位模型。

要注意一点,锁相环是一个相位反馈系统,在环路中流通的是相位,而不是电压。

因此研究锁相环的相位模型就可得环路的完整性能。

由图6可知:

(1)当A点断开环路时,锁相环的开环相位传输函数为

KL(S)=

(2)环路闭合时的相位传输函数为

H(S)

(3)环路闭合时的相位误差传输函数为

He(S)=

当环路滤波器选用无源比例积分滤波器时,经推导可得:

H(S)=

式中,,τ1=R1C,τ2=R2C

2

=,K=KdKo

同样可得:

He(S)=

ωn称为系统的固有频率或自然角频率;

称为系统的阻尼系数。

要注意的是上面讨论中的ω指的是输入信号相位的变化角频率,而不是输入信号本身的角频率。

如输入信号是调频信号,则ω指的是调制信号的角频率而不是载波的角频率。

五.锁相环的同步与捕捉

锁相环的输出频率(或VCO的频率)ωo能跟踪输入频率ωi的工作状态,称为同步状态,在同步状态下,始终有ωo=ωi。

在锁相环保持同步的条件下,输入频率ωi的最大变化范围,称为同步带宽,用ωH表示。

超出此范围,环路则失锁。

失锁时,ωoωi,如果从两个方向设法改变ωi,使ωi向ωo靠拢,进而使ωo=(ωi-ωo),当ωo小到某一数值时,环路则从失锁进入锁定状态。

这个使PLL经过频率牵引最终导致入锁的频率范围称为捕捉带ωp。

同步带ωH,捕捉带ωp和VCO中心频率ωo的关系如图7。

图7

实验原理及步骤

利用CMOS固有的低功耗、宽工作电源、集成度高等特点,可以设计出性能良好、使用方便的锁相环单片电路。

其中CD4046是一种能工作在1MHZ以下的通用PLL产品,它广泛应用于通信计算机接口领域。

图8示出CD4046的电路方框功能图。

在这个单片集成电路中,内含两个相位比较器,其中PD1是异或门鉴相器;

PD2是边沿触发式鉴相器。

另外电路中含有一个VCO,一个前置放大器A1,一个低通滤波器输出缓冲放大器A2和一个内部5V基准稳压管。

从图8可看出,引脚(16)是正电源引入端;

(8)脚是负电源端,在用单电源时接地;

(6)脚,(7)脚外接电阻C67;

(11)脚外接电阻R11和C67决定了VCO的自由振荡频率;

(12)脚外接电阻R12,它用作确定在控制电压为零时的最低振荡频率fomin;

(5)脚为VCO禁止端,当(5)脚加上“1”电平图8CD4046原理图

(即VDD)时,VCO停止工作,当为“0”

电平(即VSS)时,VCO工作;

(14)脚是PLL参考基准输入端;

(4)脚是VCO输出;

(3)是比较输入端;

(2)和(13)脚分别是PD1和PD2的输出端;

(9)脚是VCO的控制端;

(10)是缓冲放大器的输出端;

(1)脚和

(2)脚配合可做锁定指示;

(15)脚是内设5V基准电压输出端

实验一、PLL参数测试

一、压控灵敏度KO的测量

如图9,V(9)从0~9V

每隔1伏测一点,作出f-V(9)

曲线,从曲线求KO。

(KO的单位是

rad/s.v)同时测出V(9)=

1/2VDD=4.5V时VCO的频率fo、示波器

(即中心频率)图9

二、鉴相灵敏度Kd的测量。

测量方框如图10,其中LPF

为附录3中的(b)。

由于取

值R2=100K>

>

RW和R2=

R3,则运放的同相增益:

10K

反相增益:

图10

所以运放的输出UA=KAUF+KMUM=2UF-UW

信号源为—频率连续可调的方波发生器。

实验步骤

1.用另一块4046(记为4046B,图9那块记为4046A)组装一信号源,如图11。

2.按图10接实验图,注意运放324

和RW的工作电压为9V和-5V,4046

的电压为9V和OV。

由于实验中的稳

压电源只能提供两路电源,而实际需

要三路,所以应将稳压电源输出分别

调节到+12V和-5V。

9V电压由+12V

经三端稳压器7809降压后提供。

图11

3.断开信号源和4046A的PD1的连接,调RW,使4046A的VCO的频率为中心频率fO,同时调信号源的输出频率也为4046A的中心频率fO。

4.连接信号源和4046A的PD1,用双踪示波器观察Ui、UO,可观察到两个锁定的方波信号,其相差约为π/2。

5.调RW,观察Ud波形的变化,用示波器观察Ud、Ui、UO,应能观察到它们符合图3所示的相位关系。

6.通过用示波器测Ud的占空比测θe(参考图3)用数字电压表测UF(即U),θe从π/6到5π/6,每π/6测一点,作出UF~θe曲线,并由曲线求出Kd(单位为V/Rad)。

可调节示波器X轴扫描速度,让Ud的一个周期在荧屏上显示整六格,则每格就代表π/6,这样可以提高测量速度。

三、环路开环增益的测量(KH)

图12环路开环增益测量方块图

开环增益即为环路直流总增益KH=Δω/Δθ=KdK0KF(0),式中KF(0)为频率为0时,环路低通滤波器的传递函数,显然当用比例积分滤波器时,KF(0)=1,∴KH=KdK0。

实验方块图如图12,注意不用运放,LPF为附录3中的(b)。

当鉴相器比较两同相信号时,UF=0,VC0振荡于fmin;

当鉴相器比较两反相信号时,UF=VDD,VCO振荡于fmax。

做这实验时应注意是开环。

在理想情况下

KH=Δω/Δθ=2πΔf/Δθ=2π(fmax-fmin)/π=2(fmax-fmin)

实验中信号源即为图11信号源,其Out1和Out2为倒相信号。

四、同步带、捕捉带测量

实验方块如图13(LPF为附录3中的(b))。

图13同步带、捕捉带测量方块图

1.同步带的测量:

调信号源(图11)频率约为4046A的中心频率。

示波器分别测Ui和Uo,并以Ui作为示波器的触发同步信号,频率计测Ui,这时示波器可显示两个稳定的波形,即Ui和Uo是锁定的。

在一定范围内缓慢改变信号源频率,可看到两个波形的频率同时变化,且都保持稳定清晰,这就是跟踪。

但当信号源频率远大于(高端)或远小于(低端)4046A的中心频率时,Ui波形还保持稳定清晰,但Uo不能保持稳定清晰,这就是失锁。

记下刚出现失锁时的Ui频率即高端频率fHH和低端频率fHL,则同步带ΔfH = fHH-fHL 。

由于我们用的是PD1,是异或门相鉴器,当Ui和Uo为分数倍数关系时,也可能出现两个稳定的波形,这种情况应认为是“失锁”。

只有出现两个同频的稳定波形时才认为是“锁定。

2.捕捉带的测量:

环路失锁后,缓慢改变信号源频率,从高端或低端向4046A的中心频率靠近,当信号源频率分别为fPH和fPL时,环路又锁定。

则环路捕捉带ΔfP=fPH-fPL。

五、ωn、ξ的测量

实验如图14。

我们知道,当信号源的频率突然改变时(即对应Uj方波的前后沿),UF都产生一次阻尼振荡。

从阻尼振荡波形可测出A1、A2、T,其物理意义见图14。

并由A1、A2、T求出PLL的ωn和ξ:

实验步骤:

断开4046B(4)与4046A(14)

的连线,分别调W2、W1使4046A与4046B都振荡在4046A的中心频率上。

然后接上连线,这时应可观察到锁定波形。

再加入Ui(几百HZ,几百mVp-p的方波)。

示波器测UF和Ui,LPF为附录3中的(a),记录UF的A1、A2,T,并计算出ξ和ωn。

要注意的是,UF是叠加有高频信号的低频阻尼振荡信号。

A1、A2,T应是低频信号的振幅和周期。

图14Wn、ξ测试图

实验二、PLL应用实验

一、PLL频率合成器实验

频率合成器的基本原理如图15。

fi

从PLL原理知,当PLL处于锁定状fo

态时,PD两个输入信号的频率一定

精确相等。

所以可得:

f0=Nfi

图15

若fi为晶振标准信号,则通过改变分频比N,便可获得同样精度的不同频率信号输出。

选用不同的分频电路就可组成各种不同的频率合成器。

一)1KHZ标准信号源制作

1、用CMOS与非门和4M晶体组成

4MHz振荡器,如图16。

图中Rf使

F1工作于线性放大区。

晶体的等效

电感,C1、C2构成谐振回路。

C1、

C2可利用器件的分布电容不另接。

F1、F2、F3使用CD4069。

2、据讲义后面的CD4518管脚图,

测量并画出Q1,Q2、Q3、Q4及

CP之间的相位关系图。

CD4518图16

是CMOS器件,输入的CP信号一

定要用CMOS信号,即低电平为地,高电平接近VDD,(不能用直流电平为0的交流方波信号)其高低电平不能超过器件电源的正负电平。

测量时示波器的一个通道固定测Q4,都以Q4作示波器的同步触发源,且以Q4的下降沿作示波器的开始扫描点,另一个通道轮流测其他信号(CP、Q1、Q2、Q3)这样就能保证相位准确而且开始扫描点为计数器的“0”状态。

同时调节CP信号的频率或示波器的扫描速度让示波器标尺的每大格代表一个CP周期。

这样就可方便测量。

CD4518是BCD码计数器,其真值表不难自己写出,然后和测出的波形进行对照,理解其工作原理,尤其是Q2的波形