数电往年试题Word文档下载推荐.doc

《数电往年试题Word文档下载推荐.doc》由会员分享,可在线阅读,更多相关《数电往年试题Word文档下载推荐.doc(23页珍藏版)》请在冰豆网上搜索。

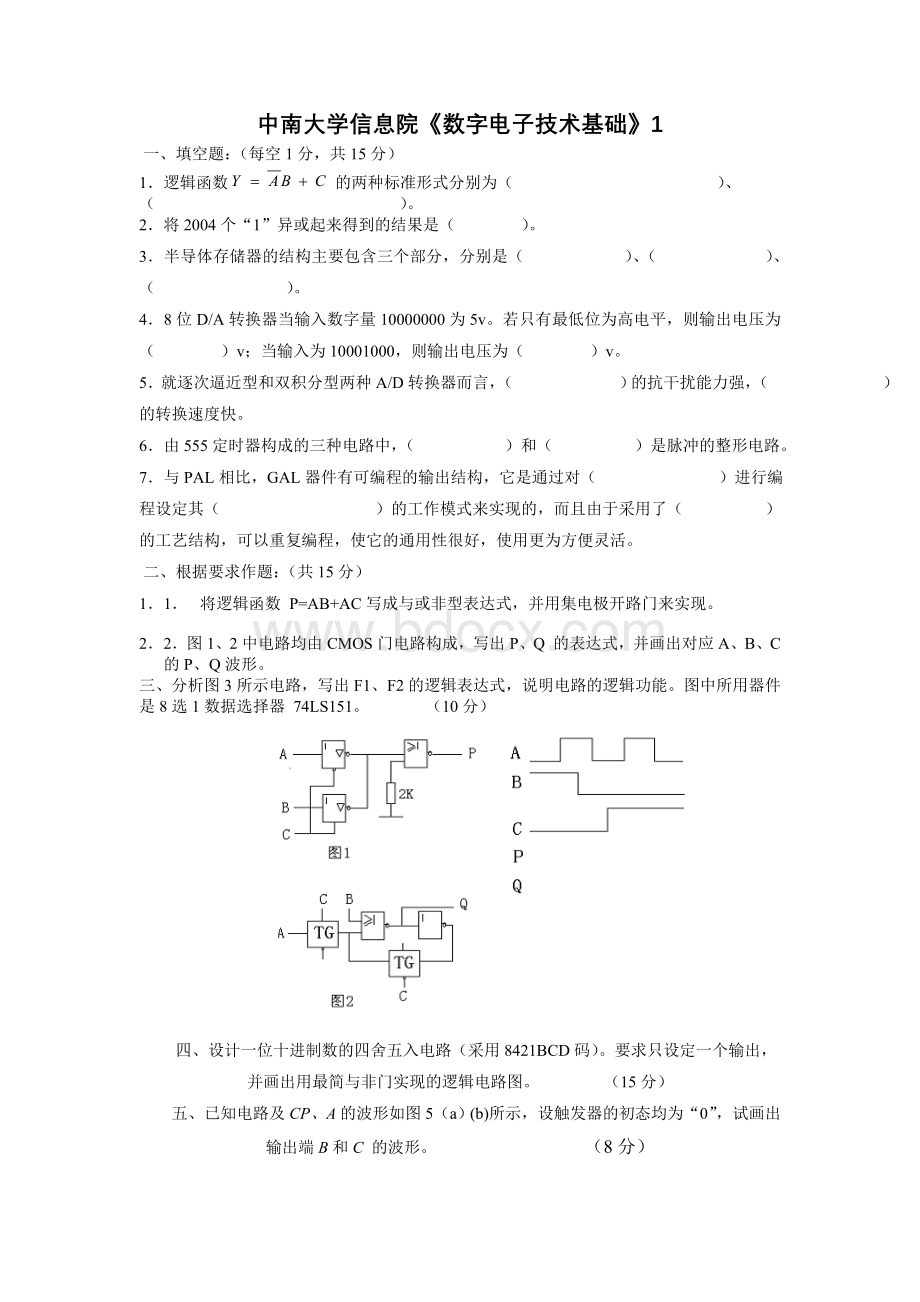

三、分析图3所示电路,写出F1、F2的逻辑表达式,说明电路的逻辑功能。

图中所用器件是8选1数据选择器74LS151。

(10分)

四、设计一位十进制数的四舍五入电路(采用8421BCD码)。

要求只设定一个输出,并画出用最简与非门实现的逻辑电路图。

(15分)

五、已知电路及CP、A的波形如图5(a)(b)所示,设触发器的初态均为“0”,试画出输出端B和C的波形。

(8分)

B

C

六、用T触发器和异或门构成的某种电路如图6(a)所示,在示波器上观察到波形如图6(b)所示。

试问该电路是如何连接的?

请在原图上画出正确的连接图,并标明T的取值。

(6分)

七、电路如图7所示,其中RA=RB=10kΩ,C=0.1μf,试问:

1.在Uk为高电平期间,由555定时器构成的是什么电路,其输出U0的频率f0=?

2.分析由JK触发器FF1、FF2、FF3构成的计数器电路,要求:

写出驱动方程和状态方程,列出状态转换表,画出完整的状态转换图;

3.设Q3、Q2、Q1的初态为000,Uk所加正脉冲的宽度为Tw=6/f0,脉冲过后Q3、Q2、Q1将保持在哪个状态?

(共15分)

八、图8所示是16*4位ROM和同步十六进制加法计数器74LS161组成的脉冲分频电路。

ROM中的数据见表8所示。

试画出在CP信号连续作用下的D3、D2、D1、D0输出的电压波形,并说明它们和CP信号频率之比。

(16分)

表8

地址输入

数据输出

A3A2A1A0

D3D2D1D0

0000

0001

0010

0011

0100

0101

0110

0111

1000

1001

1010

1011

1100

1101

1110

1111

1111

0000

CP波形如图所示:

答案

一、填空(每空1分,共15分)

1.

2.0

3.地址译码器、存储矩阵、输出缓冲器

4.0.039、5.31

5.双积分型、逐次逼近型

6.施密特触发器、单稳态触发器

7.结构控制字、输出逻辑宏单元、E2CMOS

1.,OC门线与实现图略

2.

三、

(1)列真值表:

(2)逻辑功能:

全减器

四、设用A3A2A1A0表示该数,输出F。

列出真值表如下:

逻辑表达式为:

逻辑图如下:

五、

六、T=1,连线,图略。

七、1.多谐振荡器f0=476Hz;

2.写出驱动方程3分,状态方程3分,列出状态转换000->

100->

110->

111->

011->

001->

回到100;

3.Q3Q2Q1=100(3分);

八、D3、D2、D1、D0频率比分别是1/15、3/15、5/15、7/15;

中南大学信息院《数字电子技术基础》2

(每空1分,共16分)

1.逻辑函数有四种表示方法,它们分别是()、()、()和()。

3.目前我们所学的双极型集成电路和单极型集成电路的典型电路分别是()电路和()电路。

4.施密特触发器有()个稳定状态.,多谐振荡器有()个稳定状态。

5.已知Intel2114是1K*4位的RAM集成电路芯片,它有地址线()条,数据线()条。

6.已知被转换的信号的上限截止频率为10kHz,则A/D转换器的采样频率应高于()kHz;

完成一次转换所用的时间应小于()。

7.GAL器件的全称是(),与PAL相比,它的输出电路是通过编程设定其()的工作模式来实现的,而且由于采用了()的工艺结构,可以重复编程,使用更为方便灵活。

(共16分)

3.1.

试画出用反相器和集电极开路与非门实现逻辑函数。

2、图1、2中电路由TTL门电路构成,图3由CMOS门电路构成,试分别写出F1、F2、F3的表达式。

三、已知电路及输入波形如图4(a)(b)所示,其中FF1是D锁存器,FF2是维持-阻塞D触发器,根据CP和D的输入波形画出Q1和Q2的输出波形。

设触发器的初始状态均为0。

(8分)

四、分析图5所示电路,写出Z1、Z2的逻辑表达式,列出真值表,说明电路的逻辑功能。

(10分)

五、设计一位8421BCD码的判奇电路,当输入码为奇数时,输出为1,否则为0。

要求使用两种方法实现:

(1)用最简与非门实现,画出逻辑电路图;

(2)用一片8选1数据选择器74LS151加若干门电路实现,画出电路图。

(20分)

六、电路如图7所示,其中RA=RB=10kΩ,C=0.1μf,试问:

写出驱动方程和状态方程,画出完整的状态转换图;

4.2.

设Q3、Q2、Q1的初态为000,Uk所加正脉冲的宽度为Tw=5/f0,脉冲过后Q3、Q2、Q1将保持在哪个状态?

(共15分)

七、集成4位二进制加法计数器74161的连接图如图8所示,LD是预置控制端;

D0、D1、D2、D3是预置数据输入端;

Q3、Q2、Q1、Q0是触发器的输出端,Q0是最低位,Q3是最高位;

LD为低电平时电路开始置数,LD为高电平时电路计数。

试分析电路的功能。

要求:

(1)列出状态转换表;

(2)检验自启动能力;

(3)说明计数模值。

(15分)

一、填空(每空1分,共16分)

1.真值表、逻辑图、逻辑表达式、卡诺图;

2.0;

3.TTL、CMOS;

4.两、0;

5.10、4;

6.20、50μS;

7.通用阵列逻辑、输出逻辑宏单元、E2CMOS;

1.

A

B

R

+VCC

C

四、

(1)表达式

(2)真值表

(3)逻辑功能为:

五、首先,根据电路逻辑描述画出卡诺图:

(1)最简“与-或式”为:

;

(2)“与非-与非式”为:

(与非门实现图略)

六、

(1)

(1)

多谐振荡器;

(2)

(2)

驱动方程:

状态方程:

状态转换图:

(3)初态为000,五个周期后将保持在100状态。

七、

(1)状态转换图:

(2)可以自启动;

(3)模=8;

中南大学信息院《数字电子技术基础》3

一、填空(每题1分,共10分)

1.TTL门电路输出高电平为V,阈值电压为V;

2.触发器按动作特点可分为基本型、、和边沿型;

3.组合逻辑电路产生竞争冒险的内因是;

4.三位二进制减法计数器的初始状态为101,四个CP脉冲后它的状态为;

5.如果要把一宽脉冲变换为窄脉冲应采用触发器;

6.RAM的扩展可分为、