xxx芯片详细设计模板Word格式文档下载.docx

《xxx芯片详细设计模板Word格式文档下载.docx》由会员分享,可在线阅读,更多相关《xxx芯片详细设计模板Word格式文档下载.docx(6页珍藏版)》请在冰豆网上搜索。

创建此文件

1.1

2010-7-13

根据评审结果修改

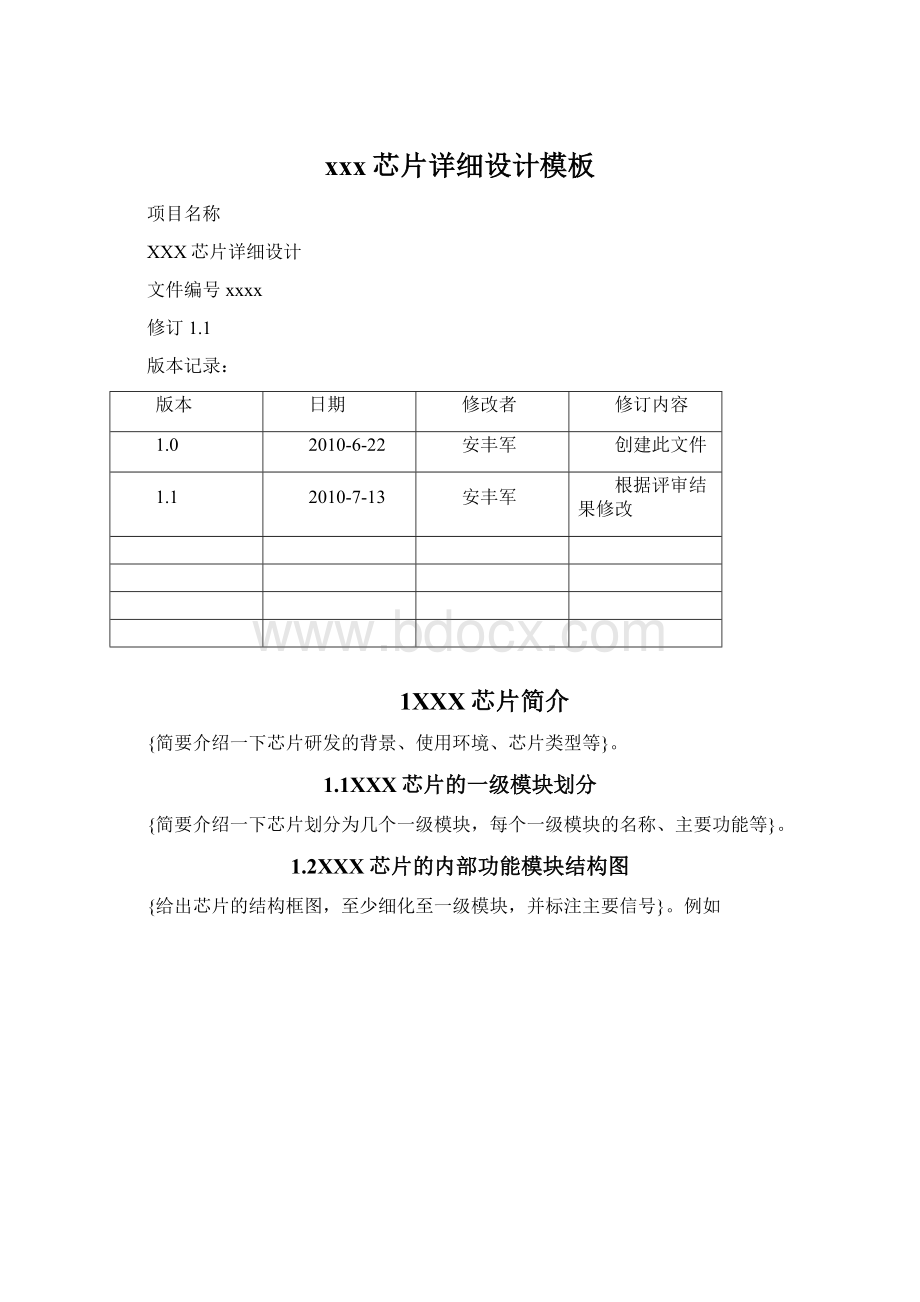

1XXX芯片简介

{简要介绍一下芯片研发的背景、使用环境、芯片类型等}。

1.1XXX芯片的一级模块划分

{简要介绍一下芯片划分为几个一级模块,每个一级模块的名称、主要功能等}。

1.2XXX芯片的内部功能模块结构图

{给出芯片的结构框图,至少细化至一级模块,并标注主要信号}。

例如

图11RF_FPGASX50T芯片内部模块结构图

2一级模块一

2.1功能描述

{简要介绍一下该一级的主要功能};

2.2接口说明

表21一级模块一信号定义

信号名称

位宽

类型

说明

外部接口

clk_1

1

INPUT

外部输入时钟1

clk_2

外部输入时钟2

rst_1

外部复位信号1

interface1_sig_1

外部信号1

Interface2_sig_1

OUTPUT

外部信号2

内部接口

inner_sig_1

内部信号1

inner_sig_2

内部信号2

{注意信号名称定义要符合《FPGA编码规范》,按照不同的组别进行信号分类}。

2.3实现说明

{介绍一下该一级模块划分为几个二级模块,每个二级模块的名称、主要功能等,给出该一级模块的结构框图,至少细化至二级模块}。

图21接收链路信号处理模块框图

2.3.1二级模块一:

{介绍一下该二级模块的具体实现,包括相关寄存器设置说明}。

表22ADC检波控制相关寄存器表

地址

寄存器名称

寄存器格式描述

功能描述

0x184

adc_op_ctl

BIT1-BIT0,OthersRsv

BIT0:

0->

1启动写ADC检波器读操作;

BIT1:

ADC检波器读状态,0-空闲,1-忙状态;

0x188

adc_value

BIT15-BIT0

检波器功率值

{二级模块接口定义}。

表23my_power_detector接口定义

clk

时钟输入信号,clk_33m_in

rst

复位信号,rst_33m_in

start

功率检波启动信号

sclk

ADC7680SPI口时钟输出

sdin

ADC7680SPI口数据输入

power_data

16

功率检波反馈功率值

power_data_vld

功率检波反馈功率值有效

sync

ADC7680SPI口片选输出

{二级模块实现具体说明,包括但不限于伪码、流程图、状态机转移图、时序图、重要IP参数配置、滤波器系数等}。

图22检波控制模块主要信号时序图

表242x,15-taps滤波器系数

A0

A1

A2

A3

A4

A5

A6

A7

A14

A13

A12

A11

A10

A9

A8

FEC9

0000

03EB

F56A

27A8

4000

{二级模块资源使用情况预估}。

发射链路的所有用IPcore实现的滤波器都可以从IPcore的资源评估中得取,共计DSP48E共计24个,而3x滤波器消耗DSP48E13个,IQ两路共计26个,所以发射链路消耗50个DSP48E。

{如果该二级模块下还有三级、四级模块,按照同样的原则表述,最多只表述到四级模块}。

2.3.2二级模块二:

{同二级模块一}。

2.4表项/寄存器设置

{一级模块一的表项/寄存器说明等}。

2.5重要资源使用情况说明

{一级模块一的资源使用情况估计,包括但不限于reg、BRAM、乘法器、时钟资源等}。

3一级模块二

{同一级模块一}。

4参考资料

{XXX芯片设计过程中涉及到的参考资料,需要有名称/作者/版本等}。

5附录一:

XXXX

{XXX芯片设计需要特殊说明的环节or寄存器附表等}。