《嵌入式系统原理》试题B(2013秋)Word格式.doc

《《嵌入式系统原理》试题B(2013秋)Word格式.doc》由会员分享,可在线阅读,更多相关《《嵌入式系统原理》试题B(2013秋)Word格式.doc(6页珍藏版)》请在冰豆网上搜索。

九

十

总分

评卷教师

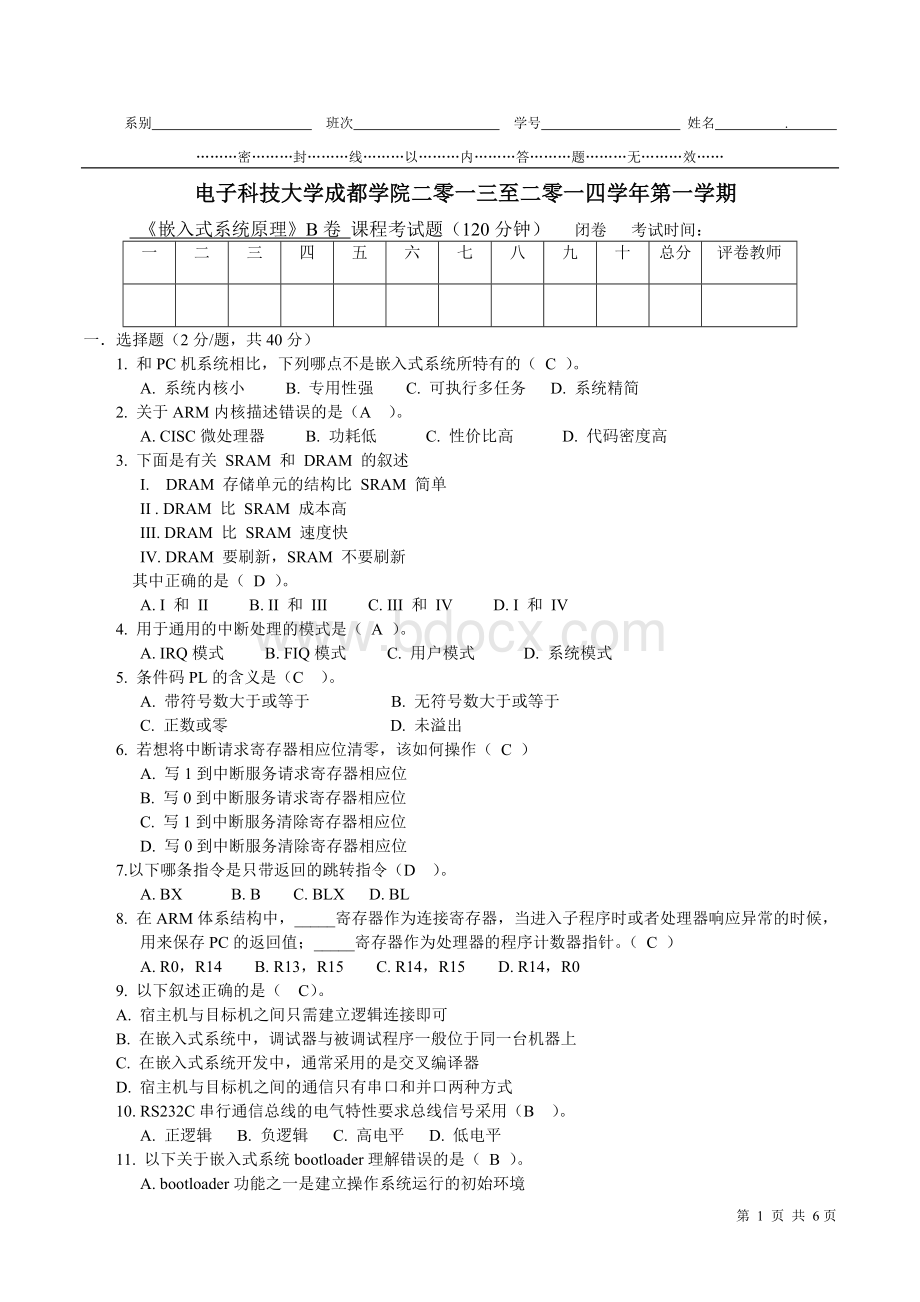

一.选择题(2分/题,共40分)

1.和PC机系统相比,下列哪点不是嵌入式系统所特有的(C)。

A.系统内核小B.专用性强C.可执行多任务D.系统精简

2.关于ARM内核描述错误的是(A)。

A.CISC微处理器B.功耗低C.性价比高D.代码密度高

3.下面是有关SRAM和DRAM的叙述

I.DRAM存储单元的结构比SRAM简单

II.DRAM比SRAM成本高

III.DRAM比SRAM速度快

IV.DRAM要刷新,SRAM不要刷新

其中正确的是(D)。

A.I和IIB.II和IIIC.III和IVD.I和IV

4.用于通用的中断处理的模式是(A)。

A.IRQ模式B.FIQ模式C.用户模式D.系统模式

5.条件码PL的含义是(C)。

A.带符号数大于或等于B.无符号数大于或等于

C.正数或零D.未溢出

6.若想将中断请求寄存器相应位清零,该如何操作(C)

A.写1到中断服务请求寄存器相应位

B.写0到中断服务请求寄存器相应位

C.写1到中断服务清除寄存器相应位

D.写0到中断服务清除寄存器相应位

7.以下哪条指令是只带返回的跳转指令(D)。

A.BXB.BC.BLXD.BL

8.在ARM体系结构中,_____寄存器作为连接寄存器,当进入子程序时或者处理器响应异常的时候,用来保存PC的返回值;

_____寄存器作为处理器的程序计数器指针。

(C)

A.R0,R14B.R13,R15C.R14,R15D.R14,R0

9.以下叙述正确的是(C)。

A.宿主机与目标机之间只需建立逻辑连接即可

B.在嵌入式系统中,调试器与被调试程序一般位于同一台机器上

C.在嵌入式系统开发中,通常采用的是交叉编译器

D.宿主机与目标机之间的通信只有串口和并口两种方式

10.RS232C串行通信总线的电气特性要求总线信号采用(B)。

A.正逻辑B.负逻辑C.高电平D.低电平

11.以下关于嵌入式系统bootloader理解错误的是(B)。

A.bootloader功能之一是建立操作系统运行的初始环境

B.bootloader是通用的

C.有些bootloader支持多CPU

D.是系统加电后运行的第一段软件代码

12.ARM7系列微处理器采用了三级流水线结构:

当一条指令被译码时,上一条指令正被(D)。

A.取指B.译码C.执行D.访存

13.FIQ中断的入口地址是(C)。

A.0x0000001CB.0x00000008

C.0x00000018D.0x00000014

14.存储一个32位数0x127845到3000H~3003H四个字节单元中,若以小端模式存储,则3000H存储单元的内容为(D)。

A.0x00B.0x45C.0x78D.0x12

15.以下描述正确的是(C)。

A.SRAM需要动态刷新B.SDRAM是掉电不易失的存储器C.FLASH在写入之前必须擦除

D.EEPROM是只读的

16.判断运算结果是负数的CPSR标志位是(A)。

A.N位B.Z位C.C位D.V位

17.USB总线属于(B)。

A.片总线B.外总线C.内总线D.并行总线

18.以S3C44B0X的定时器5为例,要求产生1ms的定时间隔。

主时钟频率MCLK为60MHz;

预定标器和分频器均采用缺省设置,定时初值为(A)。

A.30000B.60000C.15000D.120000

19.以下关于嵌入式系统理解正确的是(D)。

A.嵌入式系统的运行平台都是通用计算机

B.嵌入式系统的软件和硬件相对独立

C.嵌入式系统具有通用处理器、标准总线和外设

D.嵌入式系统一般不能再编程

20.在嵌入式处理器与外部设备接口中,使用2根线实现多对多双向收发的是(A)。

A.I2CB.UARTC.SPID.USB

二.简答题(5分/题,共30分)

1.简述嵌入式系统的概念及其特点。

2.简述嵌入式系统设计过程的基本流程。

3.ARM微处理器异常的响应和返回过程

4.存储器有哪些性能指标?

试比较常用的处理器特点。

5.RS232双机互联示意图如图1所示,写出其利用硬件握手进行发送和接收数据的过程。

图1

6.叙述存储器译码扩展地址的步骤。

三.详述题(共30分)

1.(10分)如图1为单周期存储器读时序图。

CLK为时钟信号,上升沿有效;

RD为读信号,高电平有效。

如果主设备要求的建立时间,保持时间,则此系统最高的时钟频率为多少?

能否满足保持时间的要求?

参考

功能描述

最小值

最大值

单位

t0

rd延迟时间

5

10

ns

t1

rd持续时间

60

t2

rd到有效数据输出

30

t3

data持续时间

图1

2.(20分)下图为一个跑马灯实验的硬件电路,请设计相应的软件程序,要求实现按照PD0至PD7的顺序依次点亮每一盏灯(即PD0亮->

PD0、PD1亮->

PD0、PD1、PD2亮->

……->

PD0~PD6亮->

PD0~PD7亮),至八盏灯全亮后,再重新开始只点亮PD0直至八盏灯全亮……依次照此循环。

(程序中涉及到的相关寄存器如下表所示)

要求:

1.必须使用嵌入式C语言编写;

2.必须有流程图;

3.必须定义出所用寄存器及其地址;

4.程序中必须加入注释。

第6页共6页