时序约束实例Word文档下载推荐.docx

《时序约束实例Word文档下载推荐.docx》由会员分享,可在线阅读,更多相关《时序约束实例Word文档下载推荐.docx(13页珍藏版)》请在冰豆网上搜索。

标签:

一,概述

用Altera的话来讲,timequesttiminganalyzer是一个功能强大的,ASIC-style的时序分析工具。

采用工业标准--SDC(synopsysdesigncontraints)--的约束、分析和报告方法来验证你的设计是否满足时序设计的要求。

在用户的角度,从我使用TimeQuest的经验看,它与IC设计中经常用到的比如primetime,timecraft等STA软件是比较类似的。

用过primetime或timecraft的朋友是非常容易上手的。

在这一系列的文章里,我将会拿一个DAC7512控制器的verilog设计作为例子,详细讲解如何使用TimeQuest进行时序设计和分析。

二,TimeQuest的基本操作流程

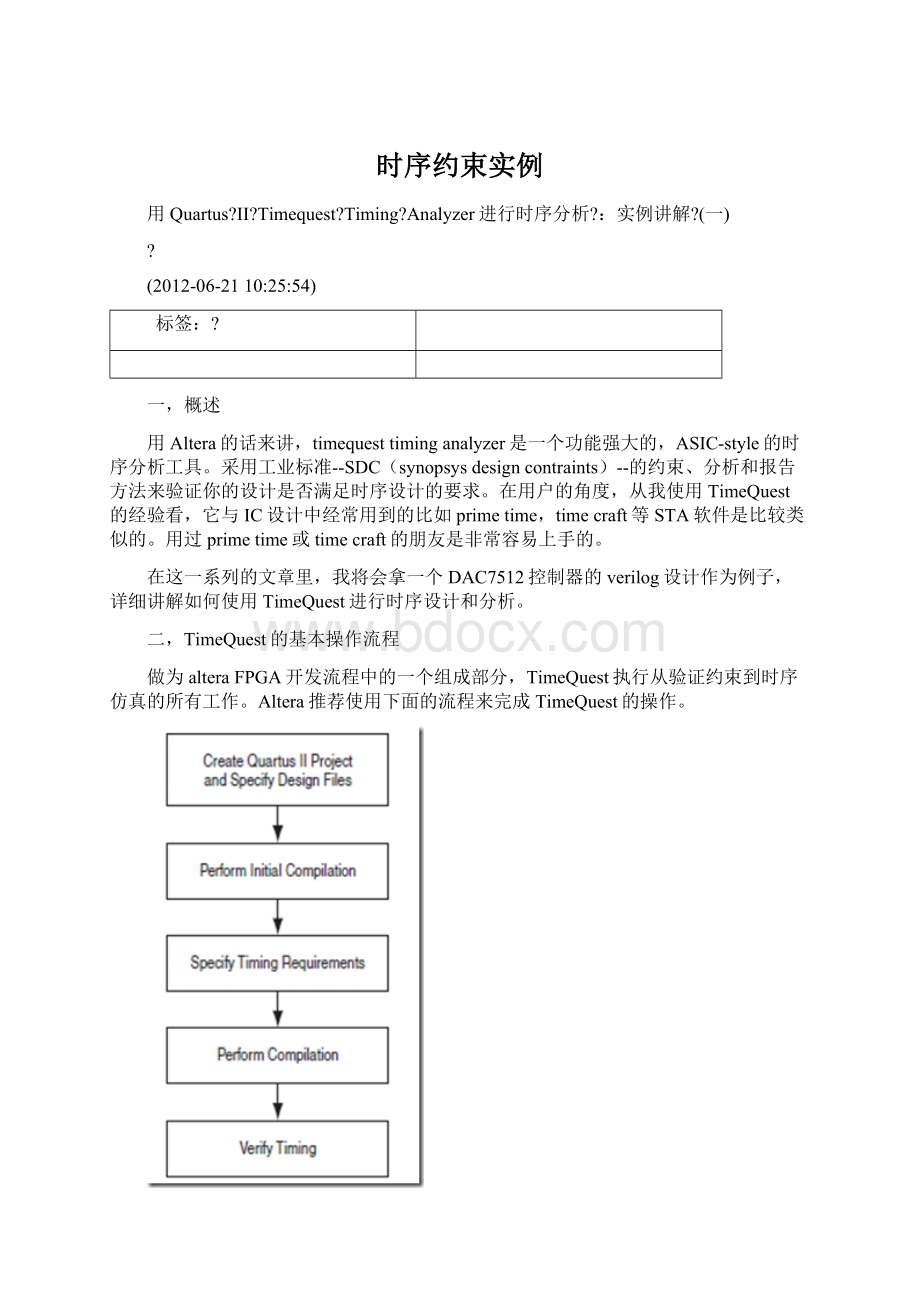

做为alteraFPGA开发流程中的一个组成部分,TimeQuest执行从验证约束到时序仿真的所有工作。

Altera推荐使用下面的流程来完成TimeQuest的操作。

1.建立项目并加入相关设计文件

不管做什么事情,都需要有一个目标或者说对象。

我们用TimeQuest做时序分析,当然也需要一个对象,这个对象实际上就是我们的设计。

所以首先是要建立一个QuartusII的项目,并把所有需要的设计文件都加入到项目中去。

需要注意的一点是,这里的设计文件,不仅仅包含逻辑设计相关的文件,也包含已经存在的时序约束文件,当然,需要以synopsysDesignConstraints(.sdc)的格式存在的。

2.对项目进行预编译(initialcompilation)

项目建立以后,如果从来没有对项目进行过编译的话,就需要对项目进行预编译。

这里的预编译是对应于全编译(fullcompilation)来讲的,我们可以理解为预编译是对项目进行部分的编译,而全编译是对项目进行完整的编译。

做预编译的目的是为了生成一个initialdesigndatabase,然后我们可以根据这个database用Timequest采用交互的模式生成时序约束。

实际上,对于小的设计,编译时间并不是很长的话,完全可以不去区分预编译和全编译,需要编译的时候,直接做全编译就可以了,做全编译的话,可以生成一个post-fit的database,完全可以给TimeQuest使用。

3.向设计中添加时序约束

在用TimeQuest做时序分析之前,必须要指定出对时序的要求,也就是我们通常所说的时序约束。

这些约束包括时钟,时序例外(timingexceptions)和输入/输出延时等。

默认情况下,QuartusII软件会给所有没有被下约束的时钟都设定为1GHz。

没有任何的时序例外,也就是说所有的timingpath都按1T去check。

所有的输入/输出的延迟都按0来计算。

这显然不符合绝大多数设计的时序要求,所以有必要根据设计的特性,添加必要的时序约束。

如上所述,时序约束主要包括三类:

时钟,时序例外和输入/输出延迟。

其中时钟和输入/输出延迟可以认为是在某种程度上增强时序设计的要求。

而时序例外可以认为是在某种程度上降低时序设计的要求。

比如说,仅仅设定一个时钟的频率为100MHz的话,这个时钟域里所有timingpath都需要能工作在100MHz下。

这显然是增强了时序设计的要求。

可是如果在这个时钟域下面,有部分timingpath是不需要做1T的check的,那么就可以通过添加时序例外来避免对这些timingpath做1T的check,即降低了时序设计的要求。

在用TimeQuest做时序分析时,如果非常熟悉设计的构架和对时序的要求,又比较熟悉sdc的相关命令,那么可以直接在sdc文件里输入时序约束的命令。

而通常情况下,可以利用TimeQuestGUI提供的设定时序约束的向导添加时序约束。

不过要注意的是,用向导生成的时序约束,并不会被直接写到sdc文件里,所以如果要保存这些时序约束,必须在TimeQuest用writesdc的命令来保存所生成的时序约束。

4.执行完整的编译

在设定好时序约束以后,就需要对整个设计进行完整的编译。

在编译过程中,软件会优化设计的逻辑、布局布线等来尽可能满足所有的时序约束。

如果没有添加时序约束,那么软件在编译的时候,会按照默认的时序约束对设计进行优化,对于绝大多数的设计,都会报出来时序的问题,但因为默认的时序约束与设计本身的要求在绝大多数情况下,都是不同的,所以这些时序的问题也并不是设计本身的问题,并没有太多的参考价值,而且很多初学者也不会注意到这个问题。

这样就把设计中很多潜在的时序问题给隐藏起来了,最终带来的可能就是系统运行的不稳定,甚至是完全不能运行。

5.验证时序

当完成编译以后,我们就可以用TimeQuest来验证时序了。

在时序分析的过程中,TimeQuest会分析设计中所有的timingpath,计算每一条timingpath的延时,检查每一条timingpath是否满足时序约束,最后按照positiveslack或negativeslack来报告时序分析的结果。

其中negativeslack就表示对应的timingpath不满足时序约束的要求(timingviolation)。

如果遇到有不满足时序要求的情况,则可以根据对应的时序报告分析设计,确定如何优化设计使之满足时序约束。

时序约束有任何变化的话,都需要重新编译设计。

这个反复的过程可以让我们解决设计中的时序问题。

三,DAC7512控制器

DAC7512是一个具有三线串行接口的DAC。

我们基于FPGA用Verilog语言实现了一个简单的DAC7512的控制器。

下面是控制器的结构图:

DAC7512控制器由三个模块组成,PLL用来生成控制器所要的时钟C0(25MHz)和C1(50MHz),其lock信号用来做为控制器的异步reset。

da_data模块生成要送往DAC7512的数据,其中DA_DATA为数据,DA_DATA_EN为数据有效信号,该模块使用C0时钟,整个属于C0时钟域。

DAC7512模块用于将DA_DATA转换成符合DAC7512接口标准的串行数据并送给DAC7512,要用到C1(50MHz)和DA_SCLK(C1二分频,25MHz)两个时钟。

DAC7512控制器一共有四个输入输出端口。

CLK_IN为PLL的基准时钟,为25MHz。

DA_DIN,DA_SCLK和DA_SYNC为三线串口,都为输出端口。

由于C0,C1是由同一个PLL输出的,DA_SCLK是由C1经二分频得到的,三者之间是同步的,处于同一个clockgroup中。

DAC7512模块的详细设计资料可参照本博客中“FPGA设计中DAC7512控制的Verilog实现”的文章。

不过要注意一点的是,在串行总线上,DA_DIN是在DA_SCLK的下降沿有效的。

把DA_DIN设计为C1时钟域的信号,并控制其值只在DA_SCLK为高电平的时候发生变化。

这样可以把DA_DIN与DA_SCLK之间的时序要求转换为DA_DIN在C1时钟域的时序要求,细节我们会在下面介绍。

四,用TimeQuest对DAC7512控制器进行时序分析?

在对某个对象下时序约束的时候,首先要能正确识别它,TimeQuest会对设计中各组成部分根据属性进行归类,我们在下时序约束的时候,可以通过命令查找对应类别的某个对象。

TimeQuest对设计中各组成部分的归类主要有cells,pins,nets和ports几种。

寄存器,门电路等为cells;

设计的输入输出端口为ports;

寄存器,门电路等的输入输出引脚为pins;

ports和pins之间的连线为nets。

具体可以参照下图(此图出自AlteraTimeQuest的使用说明)。

下面我们按照本文第二部分用TimeQuest做时序分析的基本操作流程所描述的流程对DAC7512控制器进行时序分析。

建立和预编译项目的部分相对简单,涉及到的也只是QuartusII的一些基本操作,这里我们就不再做具体的叙述。

主要介绍如何向项目中添加时序约束和如何进行时序验证。

首先建立一个名称与项目top层名字一致的sdc文件,然后按照下面的步骤添加时序约束。

1.创建时钟

添加时序约束的第一步就是创建时钟。

为了确保STA结果的准确性,必须定义设计中所有的时钟,并指定时钟所有相关参数。

TimeQuest支持下面的时钟类型:

a)基准时钟(Baseclocks)

b)虚拟时钟(Virtualclocks)

c)多频率时钟(Multifrequencyclocks)

d)生成时钟(Generatedclocks)

我们在添加时序约束的时候,首先创建时钟的原因是后面其它的时序约束都要参考相关的时钟的。

基准时钟:

基准时钟是输入到FPGA中的原始输入时钟。

与PLLs输出的时钟不同,基准时钟一般是由片外晶振产生的。

定义基准时钟的原因是其他生成时钟和时序约束通常都以基准时钟为参照。

很明显,在DAC7512控制器中,CLK_IN是基准时钟。

我们用下面的命令来创建这个基准时钟:

create_clock-nameCLK_IN-period40-waveform{020}[get_ports{CLK_IN}]

其中,create_clock是创建时钟的命令,后面是命令的各种选项。

其中-nameCLK_IN选项给出了时钟的名字,即CLK_IN。

-period40给出了时钟的周期,即40ns。

-waveform{020}给出了时钟的占空比,即50/50。

最后的[get_ports{CLK_IN}]是嵌套的tcl命令,给出了CLK_IN对应的port,实际上也就是CLK_IN的输入引脚。

在sdc文件里添加上述命令后,在quartusII里编译设计,然后通过tools–>

TimeQuestTimeAanlyzer命令打开TimeQuest。

在TimeQuest的Tasks窗口,找到ReportClocks,双击之,TimeQuest就会在右边主窗口给出设计中已成功添加的时钟信息。

如下图所示,可以看到CLK_IN,其类型为基准时钟,周期为40ns,频率为25MHz,targets项为CLK_IN,即表示这个时钟是连接在CLK_IN端口上的。

这说明上面create_clock的命令已经在设计中正确创建了时钟CLK_IN。

实际上对于create_clock命令,我们可以通过quartusII的帮助系统(),查找它的语法。

在QuartusII的帮助里,可以查找到:

Syntax

create_clock?

[-h|-help][-long_help][-add][-name<

clock_name>

]-period?

<

value>

[-waveform?

edge_list>

][<

targets>

]

另外,帮助系统里有很详尽的关于该命令的描述,并且给出了各种使用的范例。

不仅仅是这一个命令,所有的命令都可以在帮助系统里找到。

如果看到一个陌生的命令,或者不知道命令该如何使用,那么最好的办法就是在帮助系统里查找该命令。

PLL时钟:

上面我们创建了基准时钟。

下面我们创建PLL输出的时钟。

在Altera的FPGA中,PLL电路是通过ALTPLL的IP库被添加到设计中的。

下图是一个典