基于FPGA的实时测距雷达研究Word文档下载推荐.docx

《基于FPGA的实时测距雷达研究Word文档下载推荐.docx》由会员分享,可在线阅读,更多相关《基于FPGA的实时测距雷达研究Word文档下载推荐.docx(20页珍藏版)》请在冰豆网上搜索。

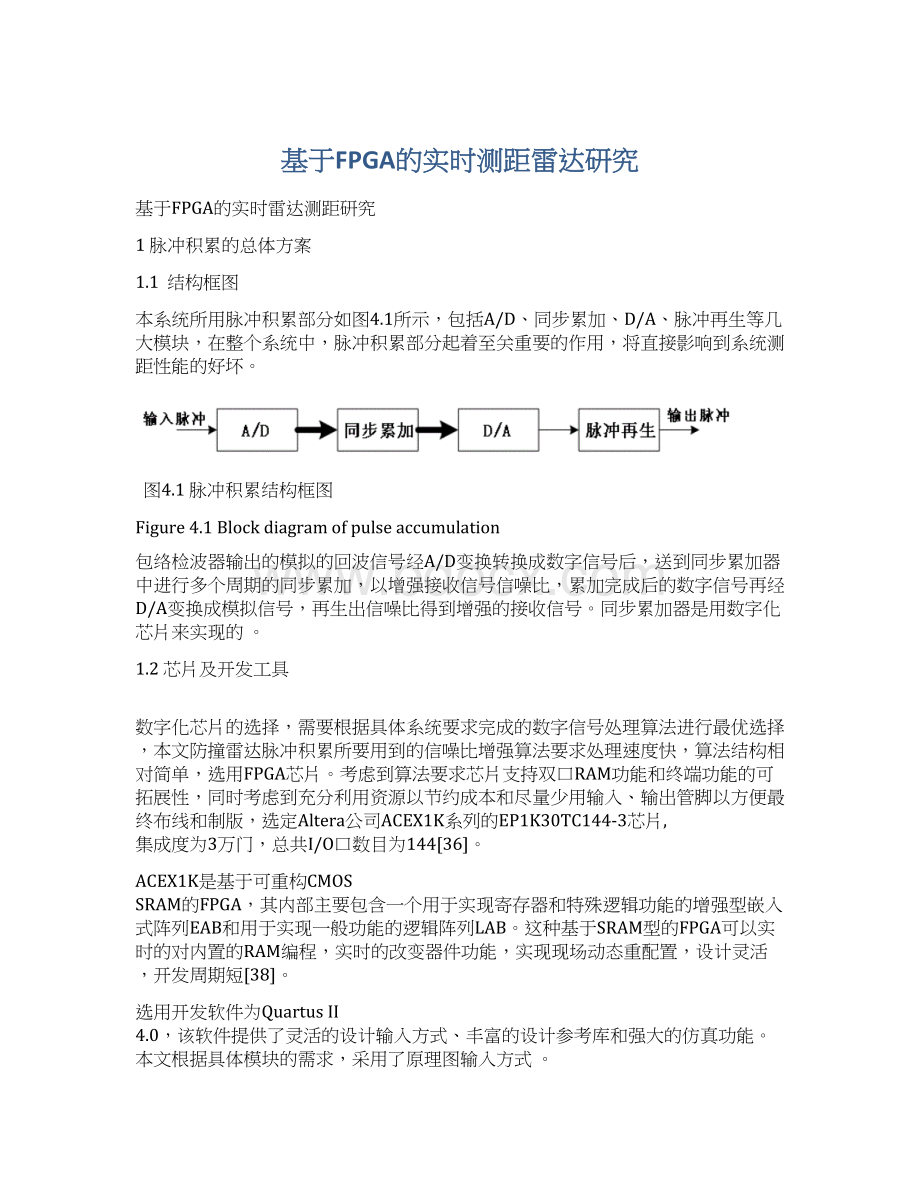

在雷达接收机的输入端,微弱的回波信号总是和噪声及其它干扰混杂在一起的。

在一般情况下,噪声是限制微弱信号检测的基本因素。

假如只有信号而没有噪声,任何微弱的信号在理论上都是可以经过任意放大而被检测到的。

雷达总是在噪声背景发现并检测目标,因此雷达检测能力实质上取决于信号的信噪比。

接收机噪声是宽频带的高斯噪声,雷达检测微弱信号的能力将受到与信号能量谱占有相同频带的噪声能量所限制。

由于噪声的起伏特性,判断信号的是否出现成为一个统计问题,必须按照某种统计检测标准进行判断。

雷达信号检测中广泛使用奈曼-皮尔逊准则,这个准则要求在给定信噪比的条件下,满足一定虚警概率

时的发现概率

最大。

这一准则的实现方法是将雷达接收机接收到的回波信号脉冲与某一预设的门限电压

进行比较,若包络幅度超过门限,则认为目标存在,否则认为目标不存在,这就是门限检测,如图4.2所示。

图4.2门限检测

Figure4.2Thresholddetection

门限检测是一种统计检测,由于信号叠加有噪声,因而输出是一个随机量。

在输出端根据振幅是否超过门限来判断有无目标存在,可能出现以下四种情况:

(1)存在目标时,判为有目标,这是一种正确判断,称为发现,它的概率称为发现概率

(DetectionRate);

(2)存在目标时,判为无目标,这是错误判断,称为漏报,它的概率称为漏报概率

(LosingAlarmRate);

(3)不存在目标时,判为无目标,称为正确不发现,它的概率称为发现概率

(AlarmNon-detectionRate);

(4)不存在目标时,判为有目标,称为虚警,它的概率称为虚警概率

(FalseAlarmRate)。

显然,这四个概率存在以下关系:

(4.1)

(4.2)

每对概率只需知道其中一个就可以了,因此,我们只讨论常用的发现概率和虚警概率。

虚警概率

通常加到接收机中频放大器上的噪声是宽带高斯噪声,其概率密度函数如下[1]:

(4.3)

是噪声电压处于

和

之间的概率;

是方差,噪声的均值为零,高斯噪声通过窄带中频滤波器(其带宽远小于中心频率)后加到包络检波器,根据随机噪声的数学分析可知,包络检波器输出端噪声电压振幅(幅值为

)的概率密度函数为

(4.4)

包络振幅的概率密度函数服从瑞利分布,设门限电平为

,噪声包络电压超过门限电平的概率分布为虚警概率

,它可以由下式求出:

(4.5)

发现概率

设振幅为

的正弦信号通高斯噪声一起输入到中频滤波器,则包络检波器输出的概率密度函数为[1]

(4.6)

式中

是总量为

的零阶修正贝塞耳函数,

(4.7)

为信号加噪声的包络,

为噪声方差,上述分布称为莱斯(Rice)分布。

则信号的发现概率

为

(4.8)

式4.8表示了发现概率与门限电平及正弦波振幅的关系,如果以功率关系来表示,信号电压与功率有如下关系,

分别表示信号和噪声功率。

(6.9)

虚警概率和发现概率的分布示意图如4.4所示。

从中可以的得出如下结论:

(1)当信噪比一定时,门限电平越高,虚警概率越小,发现概率也越小;

门限电平越低,虚警概率越大,发现概率越大。

(2)门限电平一定时,信噪比越大,发现概率密度函数的峰值点离虚警概率密度函数的峰值点越远,两条曲线相交叉部分的面积越小,产生错误判决(虚警和漏检,如下图阴影部分)的概率越小。

4.4虚警概率和发现概率的分布示意图

Figure6.4Distributionof

and

因此,提高雷达检测能力可归结为如下两个途径:

(1)在信噪比一定的情况下,选择一最佳门限

,使其在一定准则下错误判决产生的“代价”最小。

(2)提高回波信号的信噪比,从根本上减小错误判决的概率。

6.4最佳判决门限

为了便于推导说明,先对发现概率密度函数式(4.6)这一复杂积分进行近似简化。

当

时,贝塞耳函数式(4.7)

(4.10)

故当

时,由上式和式(4.7)可得

(4.11)

也就是说,在大信噪比的情况下,回波信号幅度近似为高斯分布[27]。

设雷达虚警时产生的“风险”为

,漏检时产生的“风险”为

,在门限

下所有错误判决产生的“代价”为

,则有,

(4.12)

现求一最佳门限电平

,使之判决产生的代价

最小。

由,

(4.13)

可得:

(4.14)

由于

[30],为方便计算,近似取级数前两项有:

(4.15)

可得最佳门限,

(4.16)

从上式可以看出,信噪比一定的情况下,当虚警风险大于漏检风险时(

),最佳门限较大;

当虚警风险小于漏检风险时(

),最佳门限较小,理论推导与实际情况相符。

这个最佳门限是个近似的值,在实际设计中,可根据防撞雷达预设的检测风险(

)准则以及信号的信噪比求得相应的最佳门限,使检测错误判决产生的代价最小,测距性能最好。

2.3脉冲积累

脉冲积累可以提高回波信号的信噪比。

对

个脉冲观测的结果就是一个积累的过程,积累可简单地理解为

个脉冲的叠加。

积累可以在包络检波前完成,称为检波前积累和中频积累。

信号在中频积累时要求信号间有严格的相位关系,即信号是相参的,所以又称为相参积累。

积累也可以在包络检波器以后完成,称为检波后积累或视频积累。

由于信号在包络检波后失去了相位信息而只保留下幅度信息,因而检波后积累就不需要信号间有严格的相位关系,因此又称为非相参积累[1][2]。

回波脉冲上叠加了噪声,幅度时大时小,但回波脉冲是周期性的,时间相关的,而噪声是随机的,时间无关的,多个脉冲积累后可以有效的提高信噪比,从而改善雷达的检测能力。

下面推导脉冲积累对信噪比的改善能力:

设一个周期的目标回波

由理想回波信号

和噪声

叠加而成,

(

(4.17)

其中,

为确定信号,各个周期完全相同,而

为随机信号,各个周期相互独立。

则其信噪比为,

(4.18)

个周期的目标回波简单叠加可表示为,

(4.19)

叠加后信号的信噪比为

(4.20)

由于各个周期的噪声满足统计独立条件,有

所以,

(4.22)

至此,可以得出结论,

个周期的回波积累,可使信噪比改善

倍。

上式推导是假设的理想情况,相参积累和非相参积累对信噪比的改善是不同的。

将

个等幅相参的中频脉冲信号进行相参积累,相邻周期的中频回波信号按照严格的相位关系同相相加,因此积累相加的结果信号电压可提高为原来的

倍,相应的功率提高为原来的

倍;

而噪声是随机的,相邻周期的噪声满足统计独立条件,积累的效果是平均功率相加而使总噪声功率提高为原来的

这就是说相参积累的结果可以使输出信噪比改善

个等幅脉冲在包络检波后进行理想积累时,信噪比的改善有可能达不到

这要视采用的检波方式而定,如果采用包络检波,由于包络检波器的非线性作用,信号加噪声通过检波器时,还将增加信号与噪声的相互作用项而影响输出端的信噪比,特别当检波器输入端的信噪比较低时,在检波器输出端信噪比损失更大,如果采用同步检波,则无信噪比损失,积累后信噪比的改善在

之间。

但不管采用什么检波方式,积累器输出/输入信噪比的确改善了M倍。

由于非相参积累对雷达的收发系统没有严格的相参性要求,其工程实现比较简单,故在本课题中采用包络检波后的非相参积累。

早期雷达的积累方法是依靠显示器荧光屏的余辉结合操作员的眼和脑的积累作用而完成的。

近年来,随着A/D的采样速率及处理器速度的提高,可以实现对脉冲真正意义上的积累。

3脉冲积累的实现

3.1模数转换电路

图4.4模数转换电路

Figure4.4A/Dcircuit

模数转换器选择的主要标准是采样频率。

雷达接收机的带宽为12

,根据奈奎斯特采样定理(NyquistSamplingLaw),采样频率应大于24

,系统设计采样频率为40

,因此选择了最高采样频率可达80

的模数转换器MAX1448,如图4.4所示。

MAX1448是一个10比特的模数转换器,工作电压为+2.7V-+3.6V,与FPGA+3.3V的端口电压一致,可直接互联。

A/D转换电路如图6.4所示:

A/D变换的参考电压

MAX1448A/D变换的参考电压从REFIN输入,可以用外围电路产生,也可用芯片本身产生的参考电压。

图示接法就是利用了芯片从REFOUT脚输出的内部+2.048V的精确参考电压。

时钟及控制信号

PD(PowerDownMode)接地,使A/D变换器工作在正常状态而非节能状态。

OE(OutputEnable)输出使能,当其为低时,A/D变换器的数据输出有效;

当其为高时,输出数据线为高阻状态。

OE信号由主控芯片FPAG输入,以控制采样时间。

CLK,A/D变换器的采样时钟。

采样时钟如果不稳定,发生抖动A/D变换器的性能下降,

(4.23)

为输入信号的频率,

为孔径抖动时间。

因此,要求时钟的孔径抖动(ApertureJitter)小,同时时钟的上升下降时间应小,占空比为50%。

所以,不能采用直接由晶体振荡器产生的信号作为采样时钟。

本系统中,我们先用

的有源晶体振荡器产生

振荡信号;

将其灌入FPGA中用D触发器进行2分频,分频后的信号频率为

占空比为50%,而且信号稳定度提高,上升和下降时间减小;

然后将这分频后的信号输入MAX1448中作为采样时钟。

输入耦合电路

射频变压器(RFT