数字频率计的设计设计论Word文档格式.docx

《数字频率计的设计设计论Word文档格式.docx》由会员分享,可在线阅读,更多相关《数字频率计的设计设计论Word文档格式.docx(11页珍藏版)》请在冰豆网上搜索。

本次设计主要采用计数法制成一个测量范围在0~9999Hz的频率计。

该频率计闸门信号的采样时间为1s,并采用4位数码管显示。

一、数字频率计的组成

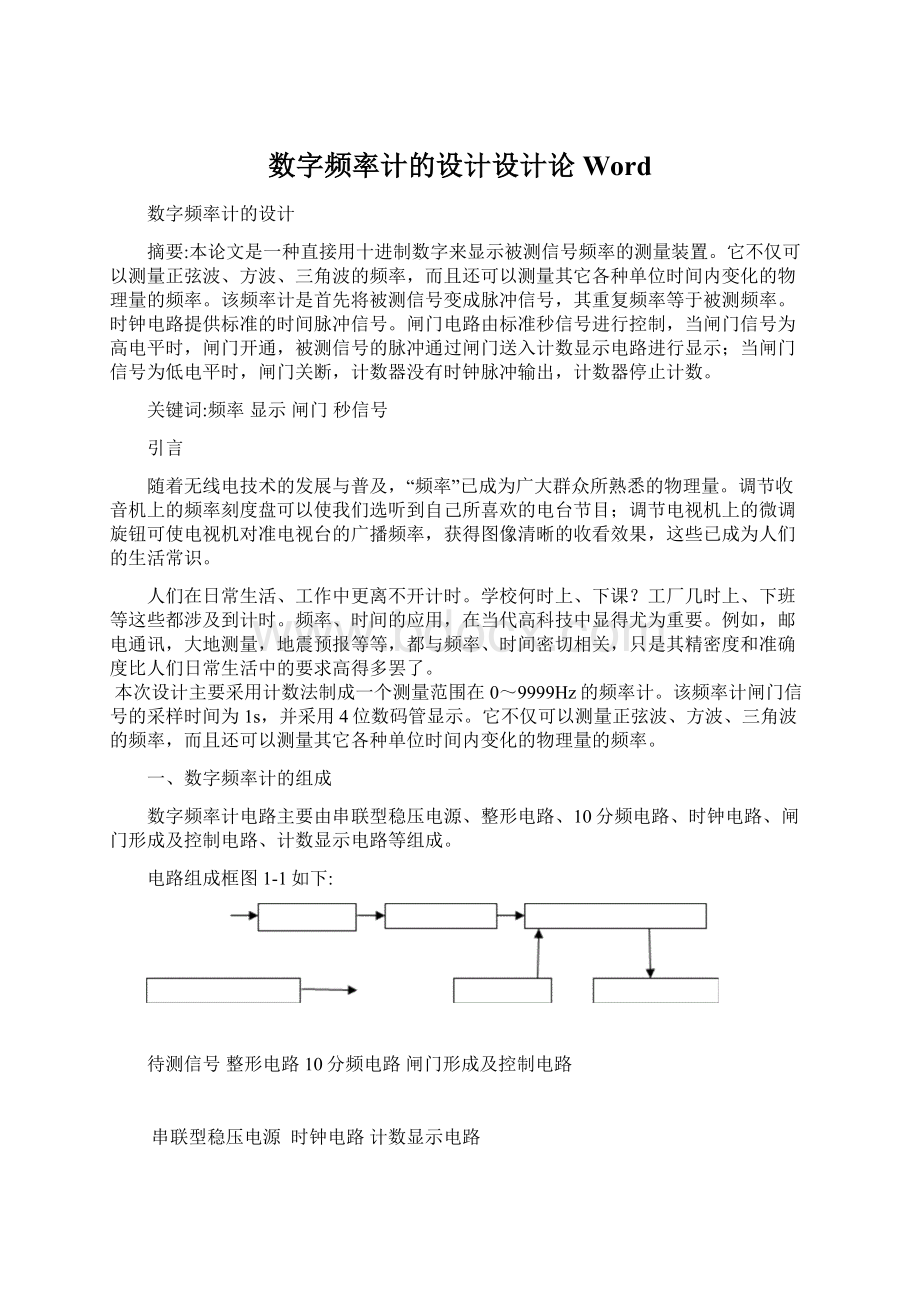

数字频率计电路主要由串联型稳压电源、整形电路、10分频电路、时钟电路、闸门形成及控制电路、计数显示电路等组成。

电路组成框图1-1如下:

待测信号整形电路10分频电路闸门形成及控制电路

串联型稳压电源时钟电路计数显示电路

电路组成框图1-1

二、设计所用集成电路简介

1.集成电路NE555概述

NE555是一种集模拟、数字于一体的中规模集成电路,它常应用于信号的产生与变化、电路的检测与控制。

芯片采用双列直插式封装,有八个管脚。

NE555引脚图2-1和功能如下

图2-1

引出端功能符号:

:

置位控置制端,也称电平触发端

复位端,低电平有效

Q:

电路的输出端

CO:

电压控制端

TH:

复位控制端

DIS:

放电端

Vcc:

电源端

GND:

接地脚

2.集成电路CD4518概述

集成电路CD4518是一个双BCD码加法计数器。

它有两个时钟输入端CP和EN,若使用时钟上升沿触发,信号就从CP端输入,同时EN端应接高电平1,若使用时钟下降沿触发,信号就从EN端输入,此时的CP端应该为低电平0,而且复位端MR也要保持低电平0,只有满足了这些条件,电路才会处于计数状态,否则计数器没办法工作。

CD4518引脚图2—2和功能如下:

图2—2

CP:

时钟输入端

MR:

消除端

EN:

计数允许控制端

1Q0-1Q3;

2Q0-2Q3:

计数输出端

GND:

接地端

VCC:

电源端

3.集成电路CD4060概述

集成电路CD4060采用16脚DIP封装,是由一个振荡器和14级二进制串行计数器位组成。

振荡器的结构可为晶体振荡电路或RC振荡电路。

它将晶体振荡器的振荡频率32768HZ信号分频为2HZ的时钟信号,送到CD4017,作为它的时钟输入信号,用来产生1S宽的闸门信号。

复位端MR为高电平时,计数器清0而且振荡器工作停止。

所有的计数器都为主-从触发器,在

的下降沿,计数器以二进制进行计数。

在时钟脉冲线上使用施密特触发器对时钟的上升和下降时间无限制。

CD4060的管脚图2-3和功能如下:

图2-3

复位端

:

时钟输入端

COUT:

时钟输出端

反向时钟输出端

Q4-Q10,Q12-Q14:

计数器输出端

正电源端

GND:

接地端

4.集成电路CD4017概述

集成电路CD4017是十进制计数/时序译码器,又称十进制计数脉冲分频器,它结构简单,造价低廉,性能稳定,工艺成熟,使用方便。

CD4017的基本功能是对CP端输入脉冲的个数进行十进制计数,并按照输入脉冲的个数顺序将脉冲分配在Y0~Y9这10个输出端。

整个输出时序就是Y0~Y9依次出现与时钟同步的高电平(一般为低电平),宽度等于时钟周期。

CD4017共有三个输入端CP、MR、EN和10个译码输出端(Y0~Y9)。

MR为复位清0端,当在MR端输入高电平或正脉冲时,计数器清0,所有输出中只有对应“0”状态时Y0端输出高电平,其余输出端(Y1~Y9)均为低电平;

时钟输入端CP有一个施密特触发器它具有脉冲整形功能,对输入时钟脉冲上升

时间和下降时间无限制,用于上升沿计数;

EN为计数有效端,用于下降沿计数,彼此间有互锁关系,若利用CP计数时,EN端应接地(低电平),而要利用EN端计数时,CP端应接高电平,反之则形成互锁;

CO为进位端,CD4017每输入10个脉冲,就可得到一个进位脉冲,所以CO也可以作为下一级计数器的时钟信号。

CD4017管脚图2-4和功能如下:

图2-4

进位端

CP:

Y0~Y9:

译码输出端

MR:

复位清0端

EN:

计数有效端

VCC:

正电源

5.集成电路CD40110概述

集成电路CD40110是可逆计数译码显示电路,它是集计数、译码、锁存、驱动为一体的四合一电路,它既可以作加法计数,又可以作减法计数。

由于电路内部有一个时钟信号预处理逻辑,因此当一个时钟输入端计数工作时,另一个时钟输入端可以是任意状态;

MR为清零端,为高电平时计数器清零;

QCO为进位脉冲输出端,作加法计数时,每当计数满10后,输出一个进位脉冲;

QBO为借位脉冲输出端,作减法计数时,每当计数满10后输出一个借位脉冲,他们

一般为高电平;

为触发器控制端,

=0时计数器工作,

=1时计数器处于禁止状态不计数;

LE为锁存控制端,当LE=0时正常显示,当LE=1时显示数被锁定。

CD40110的引脚图2-5和功能如下:

图2-5

a~g:

数码笔段输出端

LE:

锁存控制端

MR:

清零端

触发器控制端

CPU:

加计数时钟输入端

CPD:

减计数时钟输入端

QCO:

进位脉冲输出端

QBO:

借位脉冲输出端

正电源端

三、单元电路分析

1.串联型稳压电源

它可以将220V的直流电转换成稳定的直流电,给整个电路提供了6V直流稳压电源。

该电路由变压器(起降压作用)、整流、滤波、稳压几个部分组成。

当输入电压上升,输出电压随着上升,取样电路中的元件分得的电压就上升,VT3的基极电压也上升,集电极电压就会下降,导致VT2的基极电压下降,VT1的基极电压也随着下降,而VT1的集射极电压升高,使输出电压又恢复到+6V。

相反,当输入电压下降,输出电压随着下降,R3、R4、RP1分得的电压下降,VT3的基极电压下降,集电极电压就会上升,VT2的基极电压随着上升,VT1的基极电压也上升,使输出电压又恢复到+6V。

电路图3-1如下:

串联型稳压电源3-1

2.整形电路

整形电路是将待测信号如正弦波、三角波或其它呈周期性变化的波形,整形变成计数器所要求的脉冲信号,其周期不变。

施密特触发器是数字系统中常用的电路之一,它可以把变化缓慢的脉冲波形变换成为数字电路所需要的矩形脉冲。

本设计由NE555构成的施密特触发器如图3-2a所示,将高触发端TH和低触发端T

连接在一起作为信号输入端Ui。

设待测信号为三角波,输入整形电路后输出为脉冲波形,二者频率相同,波形如图3-2b所示。

当输入信号Ui<1/3Vcc时,

Uo输出为高电平;

若Ui增加,使得1/3Vcc<Ui<2/3Vcc时,电路维持原态不变,输出Uo仍为高电平;

如果输入信号增加到Ui≥2/3Vcc时,Uo从高电平翻转成低电平;

当输入信号Ui<2/3Vcc时,电路维持原态不变,输出Uo仍为低电平;

Ui继续降低到

Ui<1/3Vcc时,Uo又从低电平翻转成高电平。

输出电压Uo是一个矩形波。

由图3-2b可以看出,回差电压=2/3Vcc-1/3Vcc=1/3Vcc。

3-2a

图3-2b

3.10分频电路

分频电路的作用是对输入的脉冲信号进行分频,取得不同量程所需要的时间基准信号,实现量程控制。

CD4518为双十分频器,可对输入信号进行10、100分频,扩大测量范围。

测量范围可通过S1、S2、S3调整,S1闭合,电路未经分频电路,测量范围为0~99HZ;

S2闭合,电路为10分频,测量范围为0~999HZ;

S3闭合,电路为100分频,测量范围为0~9999HZ(S1~S3不能同时闭合)。

4.时钟电路

实现频率测量必备环节为时钟电路,它用来产生控制计数器计数的标准时间信号即闸门信号,闸门脉冲由晶体振荡器产生高稳定度的方波信号,再经分频器分频得到的,它的精度决定了频率计的频率测量精度。

在此频率计中,时钟电路由晶体振荡器和CD4060等元件组成。

晶体振荡器JT的振荡频率为32768HZ,频率较低,有利于减少分频器级数,是专为数字时钟电路设计的。

而CD4060在数字集成电路中可实现的分频次数最高,它还包含振荡电路所需的非门,使用很方便。

CD4060为14级二进制计数器,它可以将32768HZ的信号分频为2HZ的信号,而且它的两个时钟输出端直接和内部的非门串接,可以直接实现振荡和分频的功能。

VD5为发光二极管,时钟电路正常工作时,发光二极管以2HZ的频率闪烁。

5.闸门形成及控制电路

闸门电路的作用是控制计数器的输入脉冲。

时钟电路产生的2HZ时钟信号送到CD4017(十进计数器),作为它的时钟输入信号,用来产生1S宽的闸门信号,并在每一个测量周期内产生一个计数器清0信号。

1S宽的闸门信号控制CD40110接受计数脉冲的周期,CD40110在1S内接受了多少个计数脉冲,直接译码显示出计数脉冲数,而闸门控制时间为1S,所以,数码管显示的就是我们要求的被测信号的频率。

6.计数显示电路

在闸门电路导通的情况下,开始计数被测信号中有多少个上升沿,在计数的时候数码管不显示数字。

当计数完成后,此时要使数码管显示计数完成后的数字,电路里产生计数清0信号和锁存控制信号。

这些都由集计数、译码、锁存、驱动为一体的四合一电路CD40110来完成。

它不仅可作加法计数,还可以作减法计数,不仅如此,它还有计数器状态锁存,七段显示译码输出等功能。

所以,它将计数器输出的二进制代码翻译成相应的十进制数并显示出来。

显示部分的LED采用共阴极七段数码显示器。

四.整体电路分析

数字频率计实际上是一个脉冲计数器,即在单位时间里计数的脉冲个数,如图4-1计数时序波形图所示:

为闸门脉冲,假设闸门时间为1s,计数数值为N个脉冲,则被测信号

的脉冲频率为:

f=NHZ

图4-1

工作原理:

被测信号Ui首先经过整形电路,转变成计数器所需要的脉冲信号如图4-1中

,它的周期等于被测信号的周期,然后送给CD4518进行分频来扩大量程。

S1闭合最大测量范围为0~99,S2闭合最大测量范围为0~999,S3闭合最大测量范围为0~9999。

时钟电路提供准确的时间脉冲信号如图4-1中

,它是由晶体振荡器JT产生的32768HZ的信号,经过14级二进制计数器分频得到的。

它用来控制计数和保持状态。

当脉冲信号为高电平时,计数器为计数状态,当它为低电平时,计数器保持状态,数据就被送到显示器进行