nand flash 裸板驱动及其时序图详解.docx

《nand flash 裸板驱动及其时序图详解.docx》由会员分享,可在线阅读,更多相关《nand flash 裸板驱动及其时序图详解.docx(17页珍藏版)》请在冰豆网上搜索。

nandflash裸板驱动及其时序图详解

nandflash裸板驱动,介绍的比较精辟

NANDFlash的驱动程序设计:

http:

//www.usr.cc/html/99/n-599.html

1. 硬件特性:

【Flash的硬件实现机制】

Flash全名叫做FlashMemory,属于非易失性存储设备(Non-volatileMemoryDevice),与此相对应的是易失性存储设备(VolatileMemoryDevice)。

关于什么是非易失性/易失性,从名字中就可以看出,非易失性就是不容易丢失,数据存储在这类设备中,即使断电了,也不会丢失,这类设备,除了Flash,还有其他比较常见的入硬盘,ROM等,与此相对的,易失性就是断电了,数据就丢失了,比如大家常用的内存,不论是以前的SDRAM,DDRSDRAM,还是现在的DDR2,DDR3等,都是断电后,数据就没了。

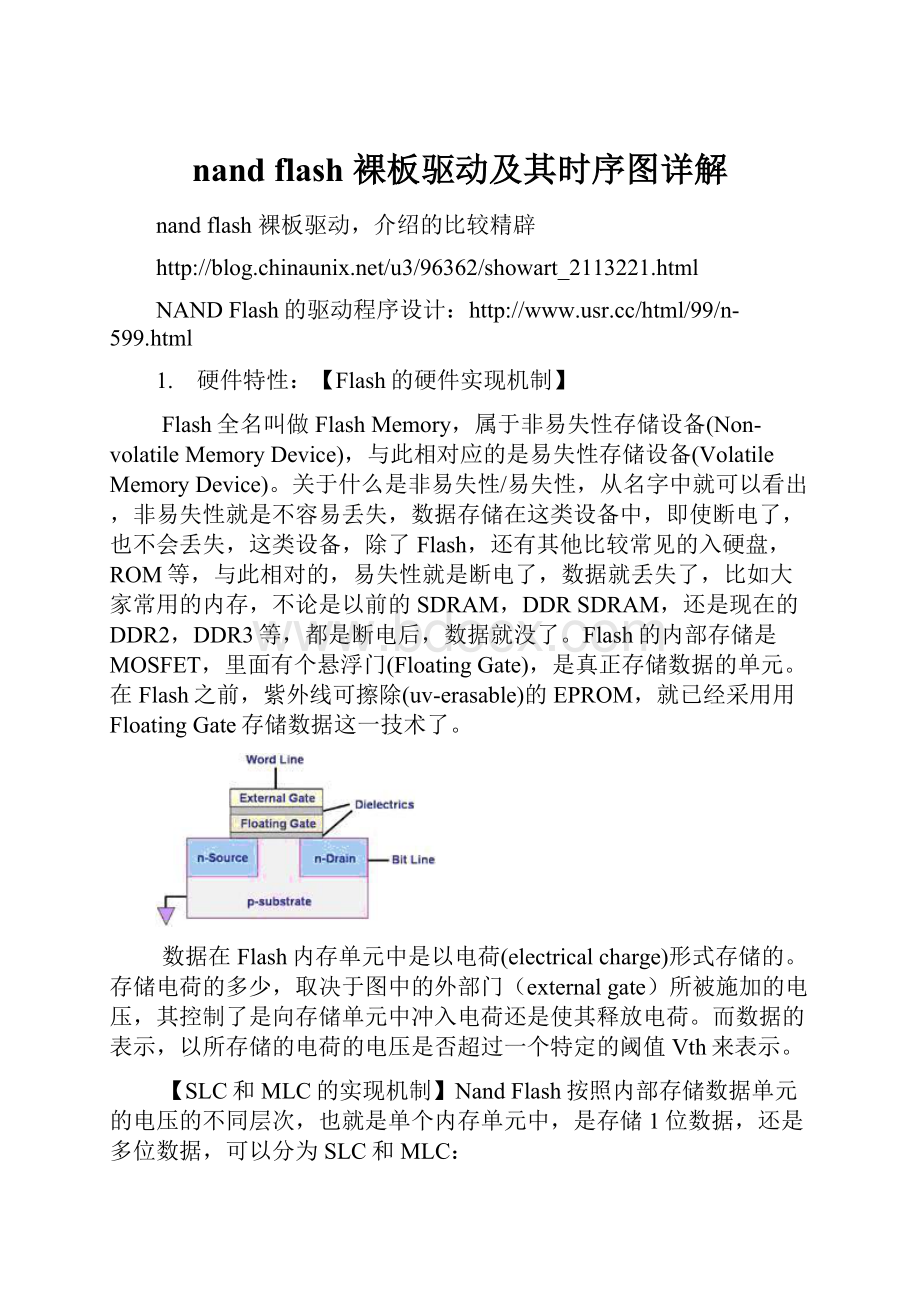

Flash的内部存储是MOSFET,里面有个悬浮门(FloatingGate),是真正存储数据的单元。

在Flash之前,紫外线可擦除(uv-erasable)的EPROM,就已经采用用FloatingGate存储数据这一技术了。

数据在Flash内存单元中是以电荷(electricalcharge)形式存储的。

存储电荷的多少,取决于图中的外部门(externalgate)所被施加的电压,其控制了是向存储单元中冲入电荷还是使其释放电荷。

而数据的表示,以所存储的电荷的电压是否超过一个特定的阈值Vth来表示。

【SLC和MLC的实现机制】NandFlash按照内部存储数据单元的电压的不同层次,也就是单个内存单元中,是存储1位数据,还是多位数据,可以分为SLC和MLC:

1. SLC,SingleLevelCell:

单个存储单元,只存储一位数据,表示成1或0.

就是上面介绍的,对于数据的表示,单个存储单元中内部所存储电荷的电压,和某个特定的阈值电压Vth,相比,如果大于此Vth值,就是表示1,反之,小于Vth,就表示0.

对于nandFlash的数据的写入1,就是控制ExternalGate去充电,使得存储的电荷够多,超过阈值Vth,就表示1了。

而对于写入0,就是将其放电,电荷减少到小于Vth,就表示0了。

关于为何NandFlash不能从0变成1,我的理解是,物理上来说,是可以实现每一位的,从0变成1的,但是实际上,对于实际的物理实现,出于效率的考虑,如果对于,每一个存储单元都能单独控制,即,0变成1就是,对每一个存储单元单独去充电,所需要的硬件实现就很复杂和昂贵,同时,所进行对块擦除的操作,也就无法实现之前的,一闪而过的速度了,也就失去了Flash的众多特性了。

2. MLC,MultiLevelCell:

与SLC相对应,就是单个存储单元,可以存储多个位,比如2位,4位等。

其实现机制,说起来比较简单,就是,通过控制内部电荷的多少,分成多个阈值,通过控制里面的电荷多少,而达到我们所需要的存储成不同的数据。

比如,假设输入电压是Vin=4V(实际没有这样的电压,此处只是为了举例方便),那么,可以设计出2的2次方=4个阈值,1/4的Vin=1V,2/4的Vin=2V,3/4的Vin=3V,Vin=4V,分别表示2位数据00,01,10,11,对于写入数据,就是充电,通过控制内部的电荷的多少,对应表示不同的数据。

对于读取,则是通过对应的内部的电流(与Vth成反比),然后通过一系列解码电路完成读取,解析出所存储的数据。

这些具体的物理实现,都是有足够精确的设备和技术,才能实现精确的数据写入和读出的。

单个存储单元可以存储2位数据的,称作2的2次方=4LevelCell,而不是2LevelCell,这点,之前差点搞晕了。

。

。

,同理,对于新出的单个存储单元可以存储4位数据的,称作2的4次方=16LevelCell。

【关于如何识别SLC还是MLC】NandFlash设计中,有个命令叫做ReadID,读取ID,意思是读取芯片的ID,就像大家的身份证一样,这里读取的ID中,是读取好几个字节,一般最少是4个,新的芯片,支持5个甚至更多,从这些字节中,可以解析出很多相关的信息,比如此NandFlash内部是几个芯片(chip)所组成的,每个chip包含了几片(Plane),每一片中的页大小,块大小,等等。

在这些信息中,其中有一个,就是识别此flash是SLC还是MLC。

下面这个就是最常见的NandFlash的datasheet中所规定的,第3个字节,3rdbyte,所表示的信息,其中就有SLC/MLC的识别信息:

http:

//www.usr.cc/html/00/n-600.html

上图是常见的NandFlash所拥有的引脚(Pin)所对应的功能,简单翻译如下:

1. I/O0~I/O7:

用于输入地址/数据/命令,输出数据

2. CLE:

CommandLatchEnable,命令锁存使能,在输入命令之前,要先在模式寄存器中,设置CLE使能

3. ALE:

AddressLatchEnable,地址锁存使能,在输入地址之前,要先在模式寄存器中,设置ALE使能

4. CE#:

ChipEnable,芯片使能,在操作NandFlash之前,要先选中此芯片,才能操作

5. RE#:

ReadEnable,读使能,在读取数据之前,要先使CE#有效。

6. WE#:

WriteEnable,写使能,在写取数据之前,要先使WE#有效。

7. WP#:

WriteProtect,写保护

8. R/B#:

Ready/BusyOutput,就绪/忙,主要用于在发送完编程/擦除命令后,检测这些操作是否完成,忙,表示编程/擦除操作仍在进行中,就绪表示操作完成.

9. Vcc:

Power,电源

10. Vss:

Ground,接地

11. N.C:

Non-Connection,未定义,未连接。

[小常识]

在数据手册中,你常会看到,对于一个引脚定义,有些字母上面带一横杠的,那是说明此引脚/信号是低电平有效,比如你上面看到的RE头上有个横线,就是说明,此RE是低电平有效,此外,为了书写方便,在字母后面加“#”,也是表示低电平有效,比如我上面写的CE#;如果字母头上啥都没有,就是默认的高电平有效,比如上面的CLE,就是高电平有效。

还有的是在字母前面加个小n,例如nRE,这也是表示低电平有效的。

【为何需要ALE和CLE】突然想明白了,NandFlash中,为何设计这么多的命令,把整个系统搞这么复杂的原因了:

比如命令锁存使能(CommandLatchEnable,CLE)和地址锁存使能(AddressLatchEnable,ALE),那是因为,NandFlash就8个I/O,而且是复用的,也就是,可以传数据,也可以传地址,也可以传命令,为了区分你当前传入的到底是啥,所以,先要用发一个CLE(或ALE)命令,告诉nandFlash的控制器一声,我下面要传的是命令(或地址),这样,里面才能根据传入的内容,进行对应的动作。

否则,nandflash内部,怎么知道你传入的是数据,还是地址,还是命令啊,也就无法实现正确的操作了.

【NandFlash只有8个I/O引脚的好处】

1. 减少外围引脚:

相对于并口(Parellel)的NorFlash的48或52个引脚来说,的确是大大减小了引脚数目,这样封装后的芯片体积,就小很多。

现在芯片在向体积更小,功能更强,功耗更低发展,减小芯片体积,就是很大的优势。

同时,减少芯片接口,也意味着使用此芯片的相关的外围电路会更简化,避免了繁琐的硬件连线。

2. 提高系统的可扩展性,因为没有像其他设备一样用物理大小对应的完全数目的addr引脚,在芯片内部换了芯片的大小等的改动,对于用全部的地址addr的引脚,那么就会引起这些引脚数目的增加,比如容量扩大一倍,地址空间/寻址空间扩大一倍,所以,地址线数目/addr引脚数目,就要多加一个,而对于统一用8个I/O的引脚的NandFlash,由于对外提供的都是统一的8个引脚,内部的芯片大小的变化或者其他的变化,对于外部使用者(比如编写nandflash驱动的人)来说,不需要关心,只是保证新的芯片,还是遵循同样的接口,同样的时序,同样的命令,就可以了。

这样就提高了系统的扩展性。

【Nandflash的一些典型(typical)特性】

1.页擦除时间是200us,有些慢的有800us。

2.块擦除时间是1.5ms.

3.页数据读取到数据寄存器的时间一般是20us。

4.串行访问(Serialaccess)读取一个数据的时间是25ns,而一些旧的nandflash是30ns,甚至是50ns。

5.输入输出端口是地址和数据以及命令一起multiplex复用的。

以前老的NandFlash,编程/擦除时间比较短,比如K9G8G08U0M,才5K次,而后来很多6.nandflash的编程/擦除的寿命,最多允许的次数,以前的nandflash多数是10K次,也就是1万次,而现在很多新的nandflash,技术提高了,比如,Micron的MT29F1GxxABB,Numonyx的NAND04G-B2D/NAND08G-BxC,都可以达到100K,也就是10万次的编程/擦除。

和之前常见的NorFlash达到同样的使用寿命了。

6.48引脚的TSOP1(K9F1208UOM)封装或 52引脚的ULGA封装

【NandFlash中的特殊硬件结构】

由于nandflash相对其他常见设备来说,比较特殊,所以,特殊的设备,也有特殊的设计,所以,有些特殊的硬件特性,就有必要解释一下:

1. 页寄存器(PageRegister):

由于NandFlash读取和编程操作来说,一般最小单位是页,所以,nandflash在硬件设计时候,就考虑到这一特性,对于每一片,都有一个对应的区域,专门用于存放,将要写入到物理存储单元中去的或者刚从存储单元中读取出来的,一页的数据,这个数据缓存区,本质上就是一个buffer,但是只是名字叫法不同,datasheet里面叫做PageRegister,此处翻译为页寄存器,实际理解为页缓存,更为恰当些。

而正是因为有些人不了解此内部结构,才容易产生之前遇到的误解:

以为内存里面的数据,通过NandFlash的FIFO,写入到NandFlash里面去,就以为立刻实现了实际数据写入到物理存储单元中了。

而实际上,只是写到了这个页缓存中,只有等你发了对应的编程第二阶段的确认命令0x10之后,实际的编程动作才开始,才开始把页缓存中的数据,一点点写到物理存储单元中去。

这也是为什么发完命令0x10之后需要等待一段时间的原因。

所以,简单总结一下就是,对于数据的流向,实际是经过了如下步骤:

图4NandFlash读写时的数据流向

【NandFlash中的坏块(BadBlock)】

NandFlash中,一个块中含有1个或多个位是坏的,就成为其为坏块。

坏块的稳定性是无法保证的,也就是说,不能保证你写入的数据是对的,或者写入对了,读出来也不一定对的。

而正常的块,肯定是写入读出都是正常的。

坏块有两种:

(1)一种是出厂的时候,也就是,你买到的新的,还没用过的NandFlash,就可以包含了坏块。

此类出厂时就有的坏块,被称作factory(masked)badblock或initialbad/invalidblock,在出厂之前,就会做对应的标记,标为坏块。

具体标记的地方是,对于现在常见的页大小为2K的NandFlash,是块中第一个页的oob起始位置(关于什么是页和oob,下面会有详细解释)的第1个字节(旧的小页面,pagesize是512B甚至256B的nandflash,坏块标记是第6个字节),如果不是0xFF,就说明是坏块。

相对应的是,所有正常的块,好的块,里面所有数据都是0xFF的。

(2)第二类叫做在使用过程中产生的,由于使用过程时间长了,在擦块除的时候,出错了,说明此块坏了,也要在程序运行过程中,发现,并且标记成坏块的。

具体标记的位置,和上面一样。

这类块叫做worn-outbadblock。

对于坏块的管理,在Linux系统中,叫做坏块管理(BBM,BadBlockManagment),对应的会有一个表去记录好块,坏块的信息,以及坏块是出厂就有的,还是后来使用产生的,这个表叫做坏块表(BBT,BadBlockTable)。

在Linux内核MTD架构下的NandFlash驱动,和Uboot中NandFlash驱动中,在加载完驱动之后,如果你没有加入参数主动要求跳过坏块扫描的话,那么都会去主动扫描坏块,建立必要的BBT的,以备后面坏块管理所使用。

(这样每次使用之之前,都会自动扫描一下,建立BBT,这样就可以跳过怀块进行别的方面的处理了)

而关于好块和坏块,NandFlash在出厂的时候,会做出保证:

1.关于好的,可以使用的块的数目达到一定的数目,比如三星的K9G8G08U0M,整个flash一共有4096个块,出厂的时候,保证好的块至少大于3996个,也就是意思是,你新买到这个型号的nandflash,最坏的可能,有3096-3996=100个坏块。

不过,事实上,现在出厂时的坏块,比较少,绝大多数,都是使用时间长了,在使用过程中出现的。

2.保证第一个块是好的,并且一般相对来说比较耐用。

做此保证的主要原因是,很多NandFlash坏块管理方法中,就是将第一个块,用来存储上面提到的BBT,否则,都是出错几率一样的块,那么也就不太好管理了,连放BBT的地方,都不好找了,^_^。

一般来说,不同型号的NandFlash的数据手册中,也会提到,自己的这个nandflash,最多允许多少个坏块。

就比如上面提到的,三星的K9G8G08U0M,最多有100个坏块。

对于坏块的标记,本质上,也只是对应的flash上的某些字节的数据是非0xFF而已,所以,只要是数据,就是可以读取和写入的。

也就意味着,可以写入其他值,也就把这个坏块标记信息破坏了。

对于出厂时的坏块,一般是不建议将标记好的信息擦除掉的。

uboot中有个命令是“nandscrub”就可以将块中所有的内容都擦除了,包括坏块标记,不论是出厂时的,还是后来使用过程中出现而新标记的。

一般来说,不建议用这个。

不过,我倒是经常用,其实也没啥大碍,呵呵。

最好用“nanderase”只擦除好的块,对于已经标记坏块的块,不擦除。

【nandFlash中页的访问顺序】在一个块内,对每一个页进行编程的话,必须是顺序的,而不能是随机的。

比如,一个块中有128个页,那么你只能先对page0编程,再对page1编程,。

。

。

。

,而不能随机的,比如先对page3,再page1,page2.,page0,page4,.。

。

。

【片选无关(CEdon’t-care)技术】没明白什么意思?

很多Nandflash支持一个叫做CEdon’t-care的技术,字面意思就是,不关心是否片选,那有人会问了,如果不片选,那还能对其操作吗?

答案就是,这个技术,主要用在当时是不需要选中芯片却还可以继续操作的这些情况:

在某些应用,比如录音,音频播放等应用中,外部使用的微秒(us)级的时钟周期,此处假设是比较少的2us,在进行读取一页或者对页编程时,是对NandFlash操作,这样的串行(SerialAccess)访问的周期都是20/30/50ns,都是纳秒(ns)级的,此处假设是50ns,当你已经发了对应的读或写的命令之后,接下来只是需要NandFlash内部去自己操作,将数据读取或写入进去到内部的数据寄存器中而已,此处,如果可以把片选取消,CE#是低电平有效,取消片选就是拉高电平,这样会在下一个外部命令发送过来之前,即微秒量级的时间里面,即2us-50ns≈2us,这段时间的取消片选,可以降低很少的系统功耗,但是多次的操作,就可以在很大程度上降低整体的功耗了。

总结起来简单解释就是:

由于某些外部应用的频率比较低,

【读(read)操作过程详解】

以最简单的read操作为例,解释如何理解时序图,以及将时序图中的要求,转化为代码。

解释时序图之前,让我们先要搞清楚,我们要做的事情:

那就是,要从nandflash的某个页里面,读取我们要的数据。

要实现此功能,会涉及到几部分的知识,至少很容易想到的就是:

需要用到哪些命令,怎么发这些命令,怎么计算所需要的地址,怎么读取我们要的数据等等。

下面,就一步步的解释,需要做什么,以及如何去做:

1.需要使用何种命令

首先,是要了解,对于读取数据,要用什么命令。

下面是datasheet中的命令集合:

图5.NandFlashK9K8G08U0A的命令集合

很容易看出,我们要读取数据,要用到Read命令,该命令需要2个周期,第一个周期发0x00,第二个周期发0x30。

2.发送命令前的准备工作以及时序图各个信号的具体含义

知道了用何命令后,再去了解如何发送这些命令。

[小常识]

在开始解释前,多罗嗦一下”使能”这个词,以便有些读者和我以前一样,在听这类虽然对于某些专业人士说是属于最基本的词汇了,但是对于初次接触,或者接触不多的人来说,听多了,容易被搞得一头雾水:

使能(Enable),是指使其(某个信号)有效,使其生效的意思,“使其”“能够”怎么怎么样。

。

。

。

比如,上面图中的CLE线号,是高电平有效,如果此时将其设为高电平,我们就叫做,将CLE使能,也就是使其生效的意思。

图6.NandFlash数据读取操作的时序图

注:

此图来自三星的型号K9K8G08U0A的nandflash的数据手册(datasheet)。

我们来一起看看,我在图6中的特意标注的①边上的黄色竖线。

黄色竖线所处的时刻,是在发送读操作的第一个周期的命令0x00之前的那一刻。

让我们看看,在那一刻,其所穿过好几行都对应什么值,以及进一步理解,为何要那个值。

(1)黄色竖线穿过的第一行,是CLE。

还记得前面介绍命令所存使能(CLE)那个引脚吧?

CLE,将CLE置1,就说明你将要通过I/O复用端口发送进入NandFlash的,是命令,而不是地址或者其他类型的数据。

只有这样将CLE置1,使其有效,才能去通知了内部硬件逻辑,你接下来将收到的是命令,内部硬件逻辑,才会将受到的命令,放到命令寄存器中,才能实现后面正确的操作,否则,不去将CLE置1使其有效,硬件会无所适从,不知道你传入的到底是数据还是命令了。

(2)而第二行,是CE#,那一刻的值是0。

这个道理很简单,你既然要向NandFlash发命令,那么先要选中它,所以,要保证CE#为低电平,使其有效,也就是片选有效。

(3)第三行是WE#,意思是写使能。

因为接下来是往nandFlash里面写命令,所以,要使得WE#有效,所以设为低电平。

(4)第四行,是ALE是低电平,而ALE是高电平有效,此时意思就是使其无效。

而对应地,前面介绍的,使CLE有效,因为将要数据的是命令,而不是地址。

如果在其他某些场合,比如接下来的要输入地址的时候,就要使其有效,而使CLE无效了。

(5)第五行,RE#,此时是高电平,无效。

可以看到,知道后面第6阶段,才变成低电平,才有效,因为那时候,要发生读取命令,去读取数据。

(6)第六行,就是我们重点要介绍的,复用的输入输出I/O端口了,此刻,还没有输入数据,接下来,在不同的阶段,会输入或输出不同的数据/地址。

(7)第七行,R/B#,高电平,表示R(Ready)/就绪,因为到了后面的第5阶段,硬件内部,在第四阶段,接受了外界的读取命令后,把该页的数据一点点送到页寄存器中,这段时间,属于系统在忙着干活,属于忙的阶段,所以,R/B#才变成低,表示Busy忙的状态的。

介绍了时刻①的各个信号的值,以及为何是这个值之后,相信,后面的各个时刻,对应的不同信号的各个值,大家就会自己慢慢分析了,也就容易理解具体的操作顺序和原理了。

3.如何计算出,我们要传入的地址

在介绍具体读取数据的详细流程之前,还要做一件事,那就是,先要搞懂我们要访问的地址,以及这些地址,如何分解后,一点点传入进去,使得硬件能识别才行。

此处还是以K9K8G08U0A为例,此nandflash,一共有8192个块,每个块内有64页,每个页是2K+64Bytes,假设,我们要访问其中的第7000个块中的第25页中的1208字节处的地址,此时,我们就要先把具体的地址算出来:

物理地址=块大小×块号+页大小×页号+页内地址=7000×128K+64×2K+1208=0x36B204B8(917636280),接下来,我们就看看,怎么才能把这个实际的物理地址,转化为nandFlash所要求的格式。

在解释地址组成之前,先要来看看其datasheet中关于地址周期的介绍:

图7NandFlash的地址周期组成

结合图7和图5中的2,3阶段,我们可以看出,此nandflash地址周期共有5个,2个列(Column)周期,3个行(Row)周期。

而对于对应地,我们可以看出,实际上,列地址A0~A10,就是页内地址,地址范围是从0到2047,而对于多出的A11,理论上可以表示2048~4095,但是实际上,我们最多也只用到了2048~2011,用于表示页内的oob区域,其大小是64字节。

对应地,A12~A30,称作页号,页的号码,可以定位到具体是哪一个页。

而其中,A18~A30,表示对应的块号,即属于哪个块。

简单解释完了地址组成,那么就很容易分析上面例子中的地址了:

0x36B204B8=00110110 10110010 00000100 10111000,分别分配到5个地址周期就是:

36 B2 04 B8

00110110 10110010 0000 0100 10111000

A11-A8 A7-A0

A19-A12

A27-A20

A30-A28

1st周期,A7~A0 :

10111000=0xB8

2nd周期,A11~A8 :

00000100=0x04(这里的高四位的0不是原数据中的,而是硬件要求的)

3rd周期,A19~A12 :

00100000=0x20

4th周期,A27~A20 :

01101011=0x6B

5th周期,A30~A28 :

00000011=0x03

注意,与图7中对应的,*L,意思是地电平,由于未用到那些位,datasheet中强制要求设为0,所以,才有上面的2nd周期中的高4位是0000.其他的A30之后的位也是类似原理,都是0。