设计三 数字频率计的设计.docx

《设计三 数字频率计的设计.docx》由会员分享,可在线阅读,更多相关《设计三 数字频率计的设计.docx(29页珍藏版)》请在冰豆网上搜索。

设计三数字频率计的设计

3数字频率计的设计

设计要求

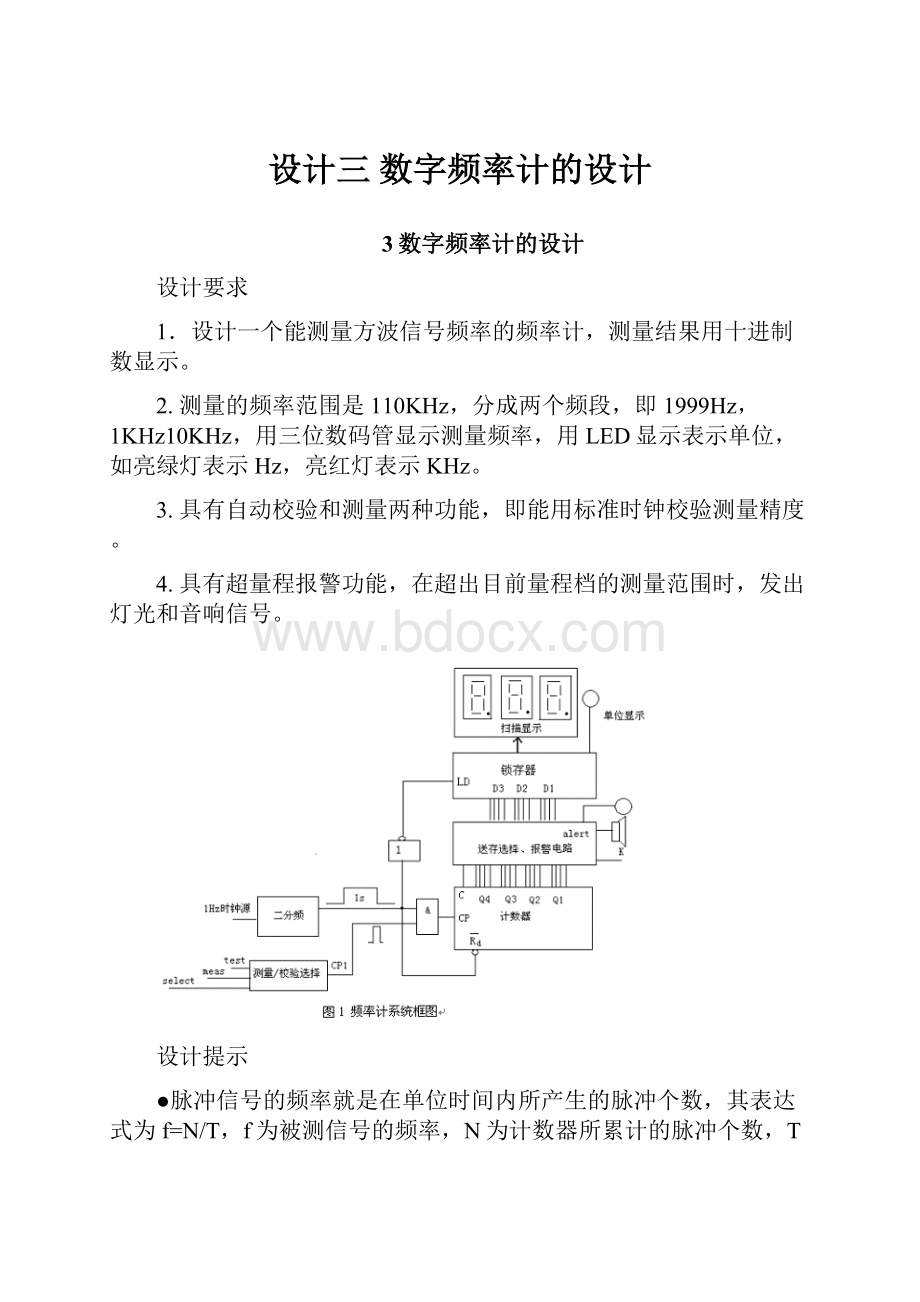

1.设计一个能测量方波信号频率的频率计,测量结果用十进制数显示。

2.测量的频率范围是110KHz,分成两个频段,即1999Hz,1KHz10KHz,用三位数码管显示测量频率,用LED显示表示单位,如亮绿灯表示Hz,亮红灯表示KHz。

3.具有自动校验和测量两种功能,即能用标准时钟校验测量精度。

4.具有超量程报警功能,在超出目前量程档的测量范围时,发出灯光和音响信号。

设计提示

●脉冲信号的频率就是在单位时间内所产生的脉冲个数,其表达式为f=N/T,f为被测信号的频率,N为计数器所累计的脉冲个数,T为产生N个脉冲所需的时间。

所以,在1秒时间内计数器所记录的结果,就是被测信号的频率。

●测量/校验选择模块*

●计数器模块

●送存选择报警模块

●锁存模块

●扫描显示模块

●测量/校验选择模块*

输入信号:

选择信号selet被测信号meas测试信号test

输出信号:

CP1

当selet=0时,为测量状态,CP1=meas;

当selet=1时,为校验状态,CP1=test。

校验与测量共用一个电路,只是被测信号CP1不同而已。

●设置1秒定时信号(周期为2秒),在1秒定时时间内的所有被测信号送计数器输入端。

●计数器对CP1信号进行计数,在1秒定时结束后,将计数器结果送锁存器锁存,同时将计数器清零,为下一次采样测量做好准备。

●设置量程档控制开关K,单位显示信号Y,当K=0时,为1999Hz量程档,数码管显示的数值为被测信号频率值,Y显示绿色,即单位为Hz;当K=1时,为1KHz10KHz量程档,被测信号频率值为数码管显示的数值乘1000,Y显示红色,即单位为KHz。

●设置超出量程档测量范围示警信号alert。

计数器由四级十进制计数构成(带进位C)。

若被测信号频率小于1KHz(K=0),则计数器只进行三级十进制计数,最大显示值为999.Hz,如果被测信号频率超过此范围,示警信号驱动灯光、扬声器报警;若被测信号为1KHz10KHz(K=1),计数器进行四位十进制计数,取高三位显示,最大显示值为9.99KHz,如果被测信号频率超过此范围,报警。

设计文档

一、原理

测频的原理归结成一句话,即在单位时间内对被测信号进行计数。

下图说明了测频的原理及误差产生的原因。

图1测频的原理

在上图中,假设时基信号为1khz,则用此法测得待测信号为1khz*7=70khz。

但从图中可以看出,待测信号应该在77khz,误差约为7/77~9.1%。

这个误差是比较大的,实际上,测量的脉冲个数的误差会在

间。

假设所测得脉冲个数为n,则所测频率的最大误差为1/(n-1)*100%。

显然,减小误差的方法就是增大n。

本频率计的要求测量结果以3位数表示,则测频误差应为1%~0.1%,则n的取值范围为:

100

n<100

即时基信号的频率为量程中最低频率的1/100(同时约为最高频率的1/1000)。

通过计算得出下表中的数据。

待测信号与时基信号的关系

待测信号/khz

时基信号/hz

10~99.9

100

1~9.99

10

二、系统框图

图2数字频率计系统框图

根据题意,各个模块的作用简述如下:

1、分频器:

由于测频时不同量程需要不同的时基信号,分频模块是必不可少的。

系统通过分频模块从晶振时钟(20MHz)分出系统所需要的几个时基信号,其中包括状态机所需时钟。

2、计数器:

从原理中可以看出,测频的本质上是计数,所以计数器也是系统中不可或缺的模块。

为实现量程的自动转换,本计数器需输出指示超量程和欠量程状态的信号。

3、状态机:

题目要求本系统可以自动转换量程,如果把每个量程看成一个状态,那么量程的切换实际上就是状态的转换。

显然,用状态机来实现是最方便的。

4、其他:

如锁存器(用来使显示数字稳定)、同步整形电路(用来处理超量程和欠量程信号,避免状态机多次转移)和七段数码管译码电路等。

三、各功能模块的实现

1状态机的设计

系统的状态机是用来自动切换量程的。

根据前面的分析,我们可以设立4个状态,状态名及其对应的量程如下表所列

状态名

对应量程

时基信号/Hz

F100K

10—99.9kHz

100

F10K

1—9.99kHz

10

OverError

超过数字频率计最高频率

100

LowError

低于数字频率计最低频率

10

假设计数器的超量程信号为over,欠量程信号为low,那么可以画出如下图所示的状态转移图。

图3状态转移图

根据此状态转移图,很容易就可以写出对应的状态机程序。

状态机见附录1

图4状态机的仿真波形

2计数器的设计

计数器的原理很简单,计数值大于999,就将超量程信号Over置1;若计数值小于100,则将欠量程信号Low置1。

本计数器在待计数信号的两个周期内完成计数与控制信号(Over与Low)的传输,在量程合适的情况下,将计数值输出。

在这两个时钟周期内,第1个时钟周期完成计数,第2个时钟周期完成控制信号的传输与计数值输出。

这样做的好处是稳定,将计数与控制信号传输分开进行,避免了时钟的跳变。

计数器的程序见附录2。

图5计数器仿真波形

3同步整形电路的设计

在实际应用中,外部输入的异步信号常常需要进行同步化(与系统时钟同步)和整形(将输入信号整形为一个时钟周期长的信号脉冲),其波形图见图6。

其程序见附录3。

图6同步整形电路仿真波形

4分频器的设计

要得到状态机及各个功能模块所需的各种频率,就必须通过分频器从已知的频率中得到,我们先实现了200分频和10分频,然后通过如下电路得到了所需的频率:

图7分频器总图

10分频、200分频和分频模块的波形仿真如下:

图8十分频器仿真波形

图9200分频仿真波形

图10分频器模块仿真波形

10分频和200分频的程序见附录4。

5锁存器的设计

在本课题中,用的是一个正沿触发的D锁存器,它有一个数据输入端d,一个时钟输入端clk和一个数据输出端q。

D锁存器的输出端只有在正脉冲沿过后,输入端d的数据才传递到输出端q。

用VHDL语言描述该D锁存器的程序见附录5。

上述D锁存器只是一个单输入输出的锁存器,通过元件例化将单输入输出的锁存器扩张成3输入输出的锁存器。

详见下图:

图11锁存器模块

图12锁存器仿真波形

图13锁存器模块仿真波形

6显示器的设计

七段数码管分为共阴极和共阳极两种。

简而言之,对共阴极来说,公共引脚要接地,想要点亮某段数码管,就在相应的引脚上加高电平;对共阳极来说正好相反,公共引脚提高电平,想要点亮某段数码管,就在相应的引脚上加低电平。

设计时用的是并行连接的七段数码管驱动程序。

并行连接,即每个数码管都由单独的译码电路控制,各数码管之间除地端GND接在一起外,其余引脚各不相关。

并行法的优点是控制简单,有几个数码管就用几个译码电路,不必修改程序,十分简单。

但当系统中所需数码管较多时,这种方法既耗资源,又占用较多的I/O口,N个数码管需占用7N个引脚(若需要小数点,则是8N个引脚)。

因此,此接法适合于系统中数码管数量不多的应用场合。

所以,本设计中用并行连接比较方便。

带使能端的译码器的程序见附录6,根据该程序通过类属映射得到显示器。

图14七段数码管仿真波形

图15显示器仿真波形

下图为数字频率计的顶层文件图。

其中clkproduct是分频模块,statemachine为状态机,counter为计数器,signallatch为同步整形电路,numlatch为琐存器,shownum为七段数码管译码电路。

图16数字频率计顶层文件

图中的输入/输出引脚的作用如下表所列。

输入/输出引脚的作用

引脚名

作用

Clock

接晶振时钟(20mhz)

Clkin

接待测信号

Dp1

接百为的小数点

Dp2

接十位的小数点

Overlight

接表征高溢出的发光二极管

Lowlight

接表征低溢出的发光二极管

Lsb[0..6]

接个位七段数码管

Middle[0..6]

接十位七段数码管

Msb[0..6]

接百位七段数码管

实际操作的设计过程如下:

(1)系统层次划分/画出系统框图

按照“自顶而下”的设计方法对系统进行划分(确定系统由哪些模块构成,各模块又由哪些子模块构成)。

(2)编码

在MAX+plusII的编辑器中写出VHDL代码。

(3)编译

编译器会对VHDL程序进行语法检查,还会产生用于防真的一些内部信息。

这一步骤通常由编译器自动完成,毋须我们干预。

如果VHDL语法有错误,编译无法通过,则须修改程序,即回到第

(2)步。

事实上,在VHDL设计过程中,常常需要往后退一步修改程序。

(4)功能仿真

VHDL仿真器允许定义输入并应用到设计中,不必生成实际电路就可以观察出。

此仿真主要用于检验系统功能设计的正确性,不涉及具体器件的特性。

例如:

libraryieee;

useieee.std_logic_1164.all;

entityshownumis

port

(

en:

instd_logic;

numina,numinb,numinc:

inintegerrange0to15;

lsb,middle,msb:

outstd_logic_vector(0to6)

);

end;

architecturestructureofshownumis

componentdisplayis

port

(en1:

instd_logic;

num:

inintegerrange0to15;

display:

outstd_logic_vector(0to6)

);

endcomponentdisplay;

begin

u1:

displayportmap(en1=>en,num=>numina,display=>lsb);

u2:

displayportmap(en1=>en,num=>numinb,display=>middle);

u3:

displayportmap(en1=>en,num=>numinc,display=>msb);

end;

这段程序是用类属映射的方法将一位七段数码管扩展成一个显示器的电路,其实显示器可以用图形的形式生成,但这里用这个方法主要是为了学习VHDL的不同设计方法。

图形方法的优点是比较直观,各个管脚的连接不容易出错,特别是当一个模块的包含许多子模块的时候,更能体现出图形方法的优越性。

又例如:

libraryieee;

useieee.std_logic_1164.all;

entityfredevider10is

generic(n:

integer:

=9);

port

(clkin:

instd_logic;

clkout:

outstd_logic

);

end;

architecturebehavioroffredevider10is

signalcounter:

integerrange0ton;

signalclk:

std_logic;

begin

process(clkin)

begin

ifrising_edge(clkin)then

ifcounter=nthen

clk<=notclk;

counter<=0;

else

counter<=counter+1;

endif;

endif;

endprocess;

clkout<=clk;

end;

上述程序是一个十分频电路,如果想得到其它倍数的分频电路可以通过修改counter的上限值N得到。

一般的计算规则是:

对一个2x的分频电路来说,counter上限值N=x-1(从0计到x-1恰好为x次,每个上升沿翻转一次就实现了2x分频)。

附录

附录1:

状态机程序

libraryieee;

useieee.std_logic_1164.all;

entitystatemachineis

port

(clock,clock10hz,clock100hz,clock100khz:

instd_logic;

low,over:

instd_logic;--欠量程信号和超量程信号

reset:

instd_logic;

en:

outstd_logic;--控制七段数码管的显示

dp1,dp2:

outstd_logic;--dp1为百位的小数点

--dp2为十位的小数点

overlight,lowlight:

outstd_logic;--待测信号频率超过总量

--的指示灯

outclock:

outstd_logic--输出时基信号

);

end;

architecturemooremachineofstatemachineis

typestate_typeis(f10k,f100k,overerror,lowerror);

signalstate:

state_type;

begin

process(clock100khz,reset)

begin

if(reset='1')then

state<=f10k;

elsifrising_edge(clock100khz)then

casestateis

whenf100k=>

ifover='1'then

state<=overerror;

elsiflow='1'then

state<=f10k;

else

state<=f100k;

endif;

whenf10k=>

ifover='1'then

state<=f100k;

elsiflow='1'then

state<=lowerror;

else

state<=f10k;

endif;

whenovererror=>

iflow='1'then

state<=f10k;

elsifover='1'then

state<=overerror;

else

state<=f100k;

endif;

whenlowerror=>

iflow='1'then

state<=lowerror;

elsifover='1'then

state<=f100k;

else

state<=f10k;

endif;

endcase;

endif;

endprocess;

process(state)

begin

casestateis

whenf100k=>

en<='1';--允许七段数码管显示数字

outclock<=clock100hz;--时基信号为100hz

overlight<='0';--待测信号频率未超过总量程

lowlight<='0';

dp1<='0';--百位上小数点不亮

dp2<='1';--十位上小数点亮

whenf10k=>

outclock<=clock10hz;

overlight<='0';

lowlight<='0';

en<='1';

dp1<='1';

dp2<='0';

whenovererror=>

en<='0';

outclock<=clock100hz;

overlight<='1';

lowlight<='0';

whenlowerror=>

en<='0';

outclock<=clock10hz;

lowlight<='1';

overlight<='0';

endcase;

endprocess;

end;

附录2:

计数器程序:

libraryieee;

useieee.std_logic_1164.all;

entitycounteris

port

(clock1,clock2:

instd_logic;

result1,result2,result3:

outintegerrange0to9;

over,low:

outstd_logic

);

end;

architecturebehaviorofcounteris

signalen,entransfer:

std_logic;

signalnum1,num2,num3:

integerrange0to9;

signalovermode:

std_logic;

begin

process(clock1)

begin

ifrising_edge(clock1)then

en<=noten;

endif;

endprocess;

process(clock2)

begin

ifrising_edge(clock2)then

ifen='1'then--en=’1’时传输数据

ifentransfer='1'then--entransfer以保证数值

--与信号只传输一次

entransfer<='0';

ifovermode='1'then--超量程的情况

low<='0';

over<='1';

overmode<='0';

elsifnum3=0then--欠量程的情况

low<='1';

over<='0';

else

low<='0';

over<='0';

result1<=num1;

result2<=num2;

result3<=num3;

endif;

num1<=0;

num2<=0;

num3<=0;

endif;

else--en=‘0‘时计数

entransfer<='1';

low<='0';

over<='0';

ifnum1=9then

ifnum2=9then

ifnum3=9then

overmode<='1';

else

overmode<='0';

num3<=num3+1;

num2<=0;

num1<=0;

endif;

else

overmode<='0';

num2<=num2+1;

num1<=0;

endif;

else

overmode<='0';

num1<=num1+1;

endif;

endif;

endif;

result1<=num1;

result2<=num2;

result3<=num3;

endprocess;

end;

附录3:

同步整形电路程序:

libraryieee;

useieee.std_logic_1164.all;

entitysignallatchis

port

(clock:

instd_logic;

signalin:

instd_logic;

signalout:

outstd_logic

);

end;

architecturepataflowofsignallatchis

signalclear,s:

std_logic;

begin

process(signalin)

begin

ifclear='1'then

s<='0';

elsifrising_edge(signalin)then

s<='1';

endif;

endprocess;

process(clock)

begin

iffalling_edge(clock)then

ifs='1'then

signalout<='1';

clear<='1';

else

signalout<='0';

clear<='0';

endif;

endif;

endprocess;

end;

附录4:

分频器程序

libraryieee;

useieee.std_logic_1164.all;

entityfredevider10is

generic(n:

integer:

=9);

port

(clkin:

instd_logic;

clkout:

outstd_logic

);

end;

architecturebehavioroffredevider10is

signalcounter:

integerrange0ton;

signalclk:

std_logic;

begin

process(clkin)

begin

ifrising_edge(clkin)then

ifcounter=nthen

clk<=notclk;

counter<=0;

else

counter<=counter+1;

endif;

endif;

endprocess;

clkout<=clk;

end;

libraryieee;

useieee.std_logic_1164.all;

entityfredevider200is

generic(n:

integer:

=99);

port

(clkin:

instd_logic;

clkout:

outstd_logic

);

end;

architecturebehavioroffredevider200is

signalcounter:

integerrange0ton;

signalclk:

std_logic;

begin

process(clkin)

begin

ifrising_edge(clkin)then

ifcounter=nthen

clk<=notclk;

counter<=0;

else

counter<=counter+1;

endif;

endif;

endprocess;

clkout<=clk;

end;

附录5:

锁存器程序

libraryieee;

useieee.std_logic_1164.all;

entityshuocunis

port(clk,d:

instd_logic;

q:

outstd_logic);

end;

architecturebehaviorofshuocunis

begin

process(clk)

begin

if(clk'eventandclk='1')then

q<=d;

endif;

endprocess;

end;

附录6:

显示器程序

libraryieee;

useieee.std_logic_1164.