中国海洋大学SOPC重点.docx

《中国海洋大学SOPC重点.docx》由会员分享,可在线阅读,更多相关《中国海洋大学SOPC重点.docx(16页珍藏版)》请在冰豆网上搜索。

中国海洋大学SOPC重点

一、概述

1.常用软件工具及用途(分工):

QuartusII、SOPCBuilder、NisoIIIDE、DSPBuilder、Matlab

2.IP核概念:

分类:

用途:

3.NISO2软核处理器特性及其描述:

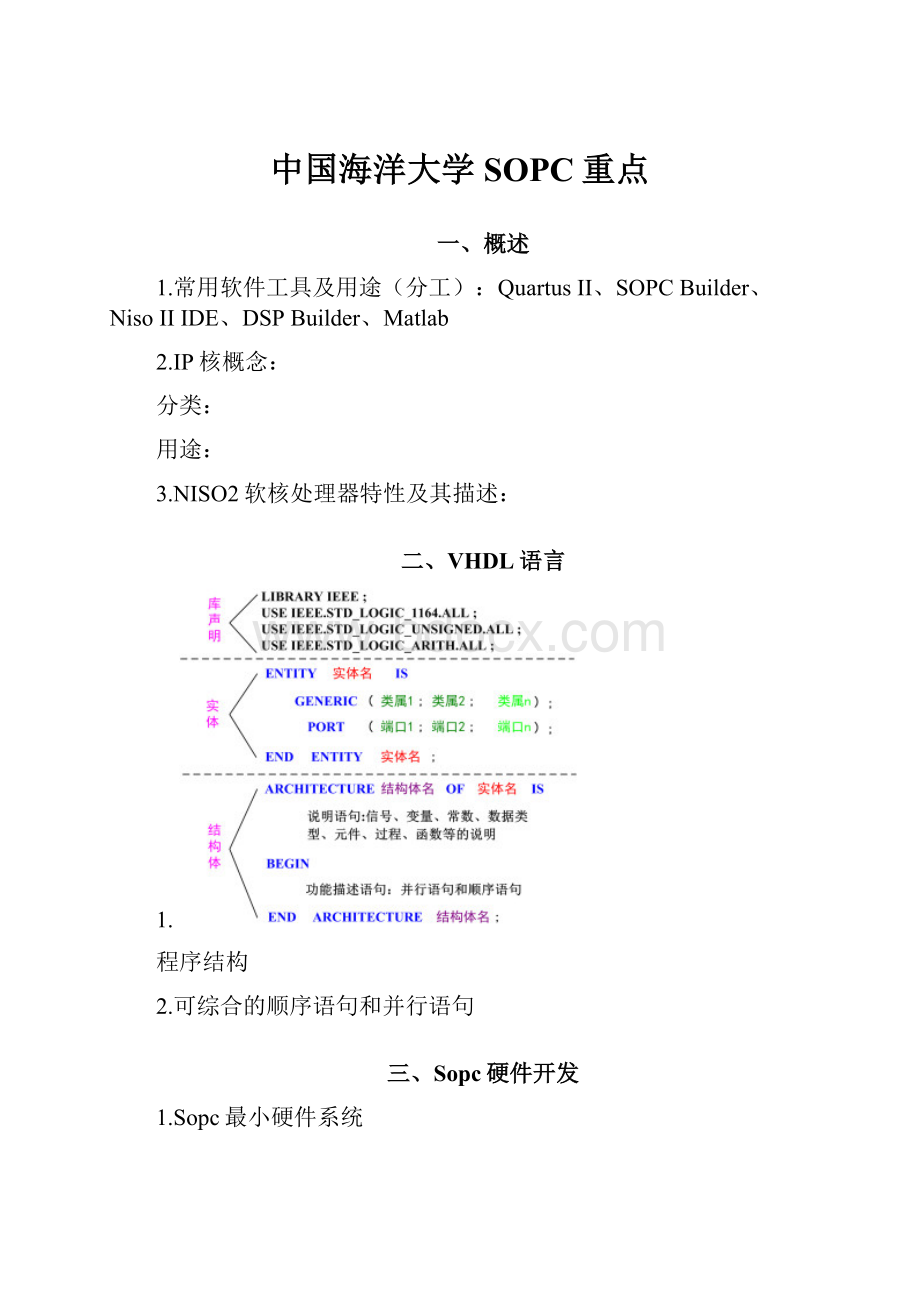

二、VHDL语言

1.

程序结构

2.可综合的顺序语句和并行语句

三、Sopc硬件开发

1.Sopc最小硬件系统

2.Sopc硬件设计流程

四、NISO2处理器体系结构

1.体系结构图

为了提高系统性能而采取的措施:

三方面

2.异常处理类型及优先级

3.NISO处理器运行模式

1)调试模式(DebugMode):

拥有最大的访问权限,可以无限制地访问所有的功能模块;

2)超级用户模式(SupervisorMode):

除了不能访问与调试有关的寄存器(bt、ba和bstatus)外,无其它访问限制;

3)用户模式(UserMode):

是超级用户模式功能访问的一个子集,它不能访问控制寄存器和一些通用寄存器。

五、Avalon总线规范

1.总线架构与传统总线架构对比

Avalon总线架构:

交换式架构,各个主机均有独立总线,主机只需抢占共享从机,某一时刻可以多个主机与多个从机交换数据。

传统总线架构:

总线仲裁控制总线主机的总线访问权,某一时刻只有一个主机使用总线,导致带宽瓶颈问题。

2.信号类型主从三态端口信号地址线及好处

地址线从主三态总助

3.传输属性

4.对Avalon总线是同步总线的理解。

Avalon接口是一个同步接口协议:

1)Avalon主端口和从端口都与Avalon总线提供的时钟CLK同步;(Avalon总线只关注其CLK的上升沿时刻的信号值)

2)所有的传输都与Avalon总线的时钟CLK同步,并在时钟CLK的上升沿启动。

(Avalon接口没有固定的或最高的性能。

接口是同步的,可以被总线提供的任意频率的时钟驱动。

最高性能取决于外设的设计和系统的实现。

不同于传统的共享总线规范,Avalon接口没有指定任何物理和电气特性)

5.Avalon总线提供了一个其他总线接口的超集,是否能够将所有外部处理器接口芯片的引脚映射成Avalon信号类型,从而实现Avalon系统与芯片的连接?

为什么?

答:

不能。

因为Avalon总线是哈佛结构的,是为哈佛结构的总线接口提供了一个超集,对非哈佛结构的外设或芯片而言,不能通过简单的引脚映射直接连接。

如8051单片机接口的CAN控制器SJA1000,需要设计总线时序桥接逻辑IP核实现Avalon总线与该控制器的接口。

6.Avalon总线、Avalon主外设、Avalon从外设之间的关系及其所带来的好处。

Avalon总线架构:

交换式架构,各个主机均有独立总线,主机只需抢占共享从机,某一时刻可以多个主机与多个从机交换数据

Avalon外设可以独立于系统中其它外设进行设计

1)Avalon主端口和从端口没有直接的连接,主、从端口都连到Avalon交换架构,由交换架构完成信号的传递;

2)主端口和交换架构之间传递的信号与从端口和交换架构之间传递的信号可能有很大的不同。

3)主从端口对的主端口和从端口可以有不同的传输属性。

Avalon总线同主/从端口通信使用各自端口指定的属性。

7.Avalon端口支持的传输属性

8.从端口传输(重点掌握)

1)基本读/写传输

2)具有固定/可变等待周期的读/写传输

3)具有建立时间、固定等待周期的读传输;具有建立时间、固定等待周期、保持时间的写传输

9.SOPC实验开发平台的CAN控制器接口IP核设计

六、DSP开发技术

1.开发流程图

1)设计输入和模型仿真:

利用Simulink建立一个模型文件(mdl文件),调用DSPBuilder和其它Simulink库中的模块,构成系统级(算法级)设计;利用Simulink的图形化仿真、分析功能,分析设计模型的正确性,完成模型仿真。

该步设计与一般的Simulink建模仿真没区别。

2)转化模型文件到硬件描述语言文件:

利用SignalCompiler模块完成模型文件到硬件描述语言文件的转换,转换之后的HDL文件是RTL级(寄存器传输级,可综合的格式)。

3)RTL级仿真:

自动流程:

ModelSim仿真;手动流程:

使用其它的仿真工具手动地进行仿真。

4)RTL级综合、网表产生、适配、时序仿真:

自动流程:

自动调用QuartusII等EDA软件;手动流程:

允许用户选择相应的软件来完成,手动流程需要更多的干预,同时提供了更大的灵活性。

5)设计编译和下载:

在QuartusII中编译用户的设计,设计下载,测试验证。

2.FIR滤波器设计

1)按FIR原理的一般设计

采用16个移位寄存器、17个乘法器、1个加法器实现,实现简单、直观,但占用逻辑资源多。

2)逻辑复用设计

数据缓存采用RAM缓存,在数据存储地址发生器的控制下,数据缓存RAM为一个环形存储,实现数据移位寄存的功能,避免长序列移位寄存器因电路延迟工作不正常的问题;

采用一个乘法器和累加器完成一个CLK1采样周期内缓存数据与滤波系数的运算,运算时钟CLK2是采样时钟CLK1的16倍频以上。

减少了乘法器、加法器的数量,从而减少了逻辑资源的占用。

七、软件设计流程

1.处理器软件开发提供的主要功能:

工程管理器、编辑器和编译器、调试器、闪存编程器

2.软件开发流程

3.闪存编程器可烧写闪存类型

4.HAL为设备驱动提供的服务层次以及描述

1)通用设备模型和驱动程序:

通用设备模型是HAL强大功能的核心,用户可采用统一的API编程访问HAL提供通用设备模型的设备。

2)头文件和访问函数:

对于部分NIOSII系统外设和一些自定制外设,HAL只提供头文件和访问函数。

5.NISO2IDE工程结构

6.对字符型设备2种访问方式及编程实例(以串口为例)

1)使用标准输入、标准输出和标准错误通道访问字符型设备

2)使用通用的访问文件的方式访问字符型设备

八、常用外设编程

1.Sopc软硬件协同设计---SPI接口A/D芯片

1)GPIO核接口方案

通过GPIO与A/D芯片连接。

SPI接口的工作时序由CPU软件程序模拟,A/D芯片的寄存器访问也由CPU软件程序实现。

特点:

硬件资源少,硬件设计简单,CPU软件复杂,CPU负担较重。

2)SPI控制器核接口方案

采用SPI控制器IP核连接A/D芯片。

SPI的工作时序由硬件逻辑,A/D芯片的寄存器访问流程由CPU软件程序实现。

特点:

与GPIO接口方案相比,硬件资源占用较大,CPU不需要处理SPI的访问时序,在一定程度上减轻了CPU的负担。

3)“用户自定制外设”接口方案

采用用户自定制外设实现A/D芯片与Avalon总线的连接。

SPI控制器负责与A/D芯片的SPI接口时序,A/D采样控制器负责A/D芯片的寄存器访问流程,CPU通过访问数据缓存获得采样数据。

特点:

与GPIO方案、SPI控制器方案相比,硬件资源占用更大,但CPU软件的负担进一步减轻,CPU对A/D芯片的访问就像访问一个数据存储器。

4)中断控制器设计(重点掌握)

九、系统高级开发技术

1.用户定制指令体系结构

2.用户定制builder元件的硬件设计

十、作业题

1.整理理解NIOSII处理器的各个配置参数的含义与效果

2.模型仿真、RTL级仿真、时序仿真的理解;

3.举例说明为什么在模型仿真、RTL级仿真后还需要时序仿真?

答:

以多进制移位寄存器设计为例,任意进制的移位寄存器在进行模型仿真和RTL级仿真时逻辑关系均是正确的,但多进制移位寄存器的工作前提是有序的时延信息,由于FPGA内部布局布线后不能保证有序的时延信息,在时序仿真时可能会发现理论上正常工作的多进制移位寄存器不能正常工作了,从而需要根据时序仿真结果调整算法级的设计。

10题填空(20空)

7问答题设计题