最新allegro152中添加测试点详解汇总.docx

《最新allegro152中添加测试点详解汇总.docx》由会员分享,可在线阅读,更多相关《最新allegro152中添加测试点详解汇总.docx(16页珍藏版)》请在冰豆网上搜索。

最新allegro152中添加测试点详解汇总

allegro152中添加测试点详解

15.2中添加测试点详解

公司cadence软件已经升级到15.2版本,测试点添加的界面和操作与14.2版本相比,发生了一些变化,本文详细介绍一下如何在15.2版本中添加测试点。

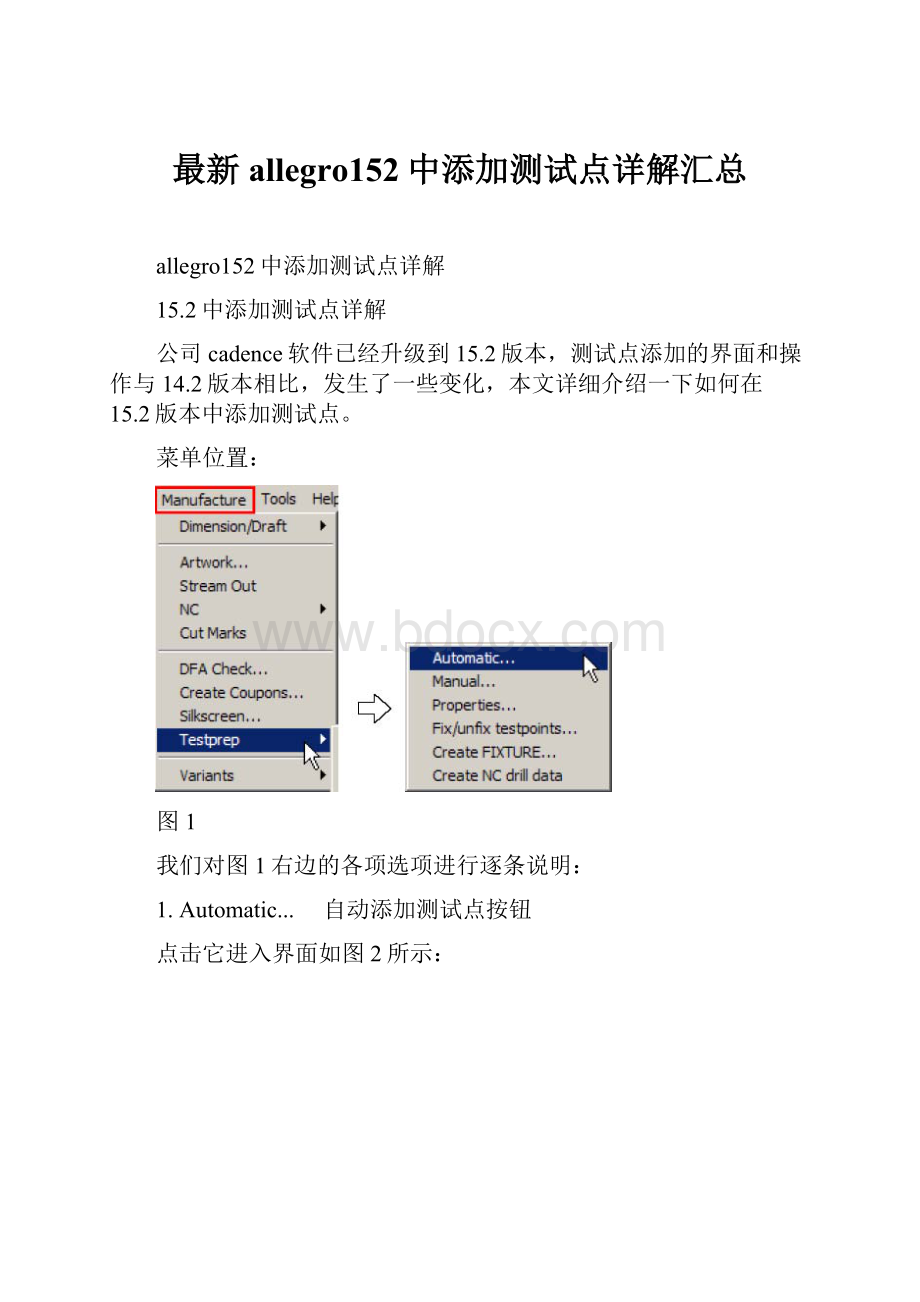

菜单位置:

图1

我们对图1右边的各项选项进行逐条说明:

1.Automatic...自动添加测试点按钮

点击它进入界面如图2所示:

图2

Allowtestdirectlyonpad:

允许直接使用通孔焊盘作为测试点

Allowtestdirectlyontrace:

用指定的表贴测试焊盘或盲孔测试焊盘(测试焊盘类型可点击parameters按钮进行指定),自动在走线上添加测试点。

必须注意,在生成测试点之处必须没有其它的焊盘或者过孔存在。

选择此项不会添加通孔类型的测试点,也不会在走线上引出一小段Stub。

Allowpinescapeinsertion:

此项和Testthruvia(可点击parameters按钮进行指定)项以及Viadisplacement项配合使用,可以给网络添加通孔测试点。

选择此项时,pcb板上必须具有routekeeping。

Testunusedpins:

指定器件没有使用的管脚可作为测试点。

Executemode:

模式选择

Overwrite:

替换所有已经存在的测试点进行重新添加。

Incremental:

进行添加测试点时不替换已经存在的测试点。

Viadisplacement:

Min:

设定一个距离管脚或过孔的最小值,以便在自动生成测试点时对过孔进行替换。

此值设为0的话,表示没有距离要求,同时运用DRC规则进行在线检测。

请注意,如果违反了DRC规则,那么将不会生成测试点。

Max:

指定一个距离管脚或过孔的最大值,以便能够自动生成测试点。

在选择图2的Generatetestpoints按钮之前,先要进行各个参数的设置,点击图2的Parameters按钮,见图3。

图3

界面功能说明:

Preferences:

Pintype:

下拉选项包括Input、Output、AnyPin、Via、AnyPnt见右

图所示。

选择AnyPnt,表示可以使用Input、Output、AnyPin、Via任意类属性的管脚作为生成测试点所用。

Padstacktype:

表示使用测试点的类型,下拉选项包括SMT/Blind、Thru、

Either,见右图所示。

选择Thru,表示生成通孔类型的测试点。

TestSMT/Blindpad:

选择表贴测试焊盘或盲孔测试点的类型。

Testthruvia:

选择通孔测试过孔类型,按照公司工艺标准,可优先选择

T_VIA0R80D0R40B_1(测试点在bottom面)。

Methodology:

Layer:

测试点位于的位置,包括Top、Bottom、Either。

依据pcb板设计的复杂程度,

如果是以Bottom层作为测试面,就选择Bottom,如果以top层作为测试面则选择top,如果两面测试,选择Either。

优先选择Bottom。

Testmethod:

指定测试每一条网络的测试探针的数目。

下拉选项包括Single、Node、Flood,选择系统默认的Single。

Bareboardtest:

光板测试。

表示在测试时无论pcb板上是否安装有器件。

如果选中此项,只要器件管脚焊盘在pcb的测试板面被定义成测试焊盘,那么在此板面的所有器件的管脚将均符合测试条件。

同时,选项AllowUnderComponentandComponentRepresentation功能将被屏蔽掉。

这样会带来隐患,生成一些不合格的测试点,像测试点可能会位于测试面的器件之下。

如果不选中此项,器件管脚只能在非元件面被测试(指正面插件器件焊盘可在背面测试)。

因此在生成测试点操作时,如果器件只存在于pcb板的顶层,可以选中此项。

如果pcb板的顶层和底层均有器件存在,那么不可选择此项。

Replacevias:

自动将过孔替换成测试点。

在替换过程中,系统会自动检查过孔的周边电

气情况以防止出现DRC,如果出现DRC,将不执行替换操作。

Disableclinebubbling:

用来设置在自动或者手动的添加测试点时,如果一个过孔被替换成测试点,周边的连接线是否自动进行绕行以避免产生DRC。

一般要选择该项,使系统不对走线进行自动绕行,然后在添加完测试点后检查每个DRC并手动的修改走线,否则系统在自动绕线时会产生一些不理想的走线效果。

见图4。

图4

选择此项效果见上左图所示,不选此项效果见上右图所示。

Restrictions:

Testgrid:

定义删格属性以便在删格上添加测试点。

0代表没有删格约束。

Minpadsize:

定义生成测试孔在测试面的焊盘的最小值。

此值需要和上面的选项Testthruvia中的测试孔在测试面的焊盘的最小值保持一致,比如上面定义了测试焊盘为T_VIA0R80D0R40B_1,则此值为0.9。

如果选择小于此值的话,在测试点报告中会存在误报,即将一些不是测试孔的过孔认为是测试孔而在报告中出现。

Minspacing:

定义相邻的两个测试点的距离。

请注意,指的是中心距离而不是边缘距离。

此值和多种因素有关,包括和测试夹具、测试点尺寸、pcb板厚、探针间隔等均有关系。

Allowundercomponent:

能否将测试点放置在器件底下,下拉菜单见右图

Componentrepresentation:

来设置器件的覆盖区域和外形,用来判断测试点和器件之间的间距是否满足要求,分为Assembly和Placebound,下拉菜单见右图,目前公司库中的Placebound大于Assembly,因此选择Placebound将更为妥当。

Text:

Display:

是否为测试点添加标号。

(一般情况这项不选,这项如果选上的,在PCB的Manufactuting/Probe_Bottom或者Probe_Top层会出现很多网络字符,很难在PCB上看得清楚哪些网络添加了测试点,哪些没有添加,不选则Display,在Manufactuting/Probe_Bottom或者Probe_Top层就可以看到三角符号的标示,有则已定义为测试点。

)

net-Alphabetic:

按照字母顺序来为同一条网络的多个测试点添加标号,第27个标号从AA起。

需要注意,如果你删除了其中的一个测试点,下一个测试点不会自动填补而依旧顺延,比如有测试点GND-A、GND-B、GND-C,GND-D,你删除了GND-C那么GND-D不会变成GND-C,而依旧会是GND-D。

net-Numeric:

按照数字的增量(步进值为1)为同一条网络的多个测试点添加标号。

需要注意,如果你删除了其中的一个测试点,下一个测试点不会自动填补而依旧顺延,比如有测试点GND-1、GND-2、GND-3,你删除了GND-3那么GND4不会变成GND-3而依旧会是GND-4。

StringNumeric:

该项设置可将Pcb板上所有测试点标识以一个任意输入的字符串来开始命名(缺省的字符串为TP),其后缀从1开始依次增加(步进值为1),最后的N近似为单板上所有测试点的个数。

Rotation:

指定添加丝印标号的方向,有0,90,180或者270度可选。

Offset:

指定添加丝印标号相对于测试点在X、Y轴方向上的偏移量。

通过上面对各个选项的详细叙述,结合公司的工艺标准,推荐在进行自动添加测试点的操作时,对参数的设置入图5所示。

(需要注意的是:

自动加测试点前应该在相关区域设置禁止加测试点区,比如B面BGA正下方不准绿油开窗,在加测试点前应该在此加一块Shape,Class和Subclass分别指定于Manufacturing和Noprobebottom。

)

图5

点击close按键,在图2中点击Generatetestpoints按键,即可进行自动添加测试点的操作。

而且会在Allegro的命令栏中显示添加的结果。

注意此值的选取:

按照公司的标准,在首次自动添加测试点操作时,此值选择1.8,手工将自动操作失败的测试点添加完成后,最后检查时此值可设为1.4。

自动添加测试孔操作完成后,会出现两种情况:

全局网络测试点添加成功,此时可以查看命令栏中显示信息:

部分网络自动添加测试点失败,此时Fail值会有数字显示,那么就需要我们对这些网络进行手工添加。

2.Manual...手动添加测试点按钮

选择该命令后,Allegro界面右边控制面板中Options项显示如图6所示:

图6

Add:

手工添加测试点。

分为两种情况,其一,网络上已经具备过孔,通过调整优化走线,

使用此命令可以直接将过孔替换成测试孔。

其二,网络上没有过孔,需要手工在合适位置通过布线的命令添加过孔,然后再使用此命令将添加的过孔替换成测试孔。

或者手工直接在合适位置通过布线的命令添加测试孔,但是还必须使用此命令将测试孔属性添加上去。

Add(Scanandhighlight):

选择此项可以逐个地扫描未加测点的网络并将其高亮,同时窗

口会自动跳到包含这条网络的视窗,同时Allegro视窗下方的命令栏会显示没有测试点的网络。

然后在此网络上进行手工添加测试点的操作。

点击鼠标右键可进行Done、Cancle或Next操作。

Delete:

删除已经存在的测试点,执行此项操作后,鼠标点击选中的测试过孔将恢复成系统自动替换成测试孔以前的过孔(试验证明,14.2版本的pcb板即使在15.2的环境下执行此操作,将只能被删除掉测试孔属性而不会替换过孔)。

Swap:

将测试点属性交换到另外的一个焊盘或过孔上。

Query:

点击你关注的测试点后,会显示该测试点的属性。

Properties:

点击此键,Allegro界面右边控制面板中Options项显示如图7所示:

图7

Mode栏和Property搭配使用:

Add:

添加Property栏选中内容的属性。

Delete:

删除Property栏选中内容的属性。

Query:

显示测试点属性。

需要注意,以上3条命令都是对选中的整条网络进行操作的。

Property:

Net:

NO_TEST:

此项可以定义某条或多条网络不需要测试点属性。

TESTPOINT_QUANTITY:

定义同网络上的测试点数目为多少。

默认为1。

Symbol:

TESTPOINT_ALLOW_UNDER:

定义测试点是否可以位于某个器件之下,左键点击器件进行定义。

3.Property:

用来设置网络的一些和测试点相关的属性。

功能和上述相同。

4.Fix/unfixtestpoints:

对整板所有的测试点进行锁定和解除锁定操作,如图8所示:

图8

5.CreateFIXTURE:

用来生成测试点的夹具文件。

选择该命令后,界面如图9所示。

如果以前没有执行过这个命令,点击界面中的Createfixture按钮后系统会自动在Manufacturing的大类中添加两个subclass,Fixture_Top和Fixture_Bottom,以方便后面检查使用,如图10所示。

如果对测试点进行了修改,可重新执行该命令,注意选中OverwriteexistingFIXTUREsubclass复选项即可生成新的测试点夹具。

图9

图10

6.CreateNCdrilldata:

生成测试点的转孔数据。

TOP层的测试点和BOTTOM层的

测试点数据是分开的,分别命名为top_probe.drl和bottom_probe.drl。

需要提醒的是,15.2在Constraints的DesignConstraints…窗体里也加了测点的相关DRC检查,可以方便设计者进行测试点的自检。

如图11所示:

图11

添加测点相关信息的Report报表输出,如图12所示:

图12

执行Report将会有相应报告产生。

附:

手工添加测试孔时注意以下几点:

1.测试点边缘距离其它的过孔边缘极限尺寸:

0.5mm。

图示中亮线距离

2.测试点边缘距离铜线边缘极限尺寸0.2mm。

图示中亮线所示距离

3.测试孔中心距离安装孔中心极限尺寸4.5mm。

图示中亮线所示距离

4.测试孔间的中心距为1.5mm

图示中亮线所示距离

5.测试孔不能位于底面器件的placebound下。

6.测试孔边缘距离底面器件最大边缘(chip类为丝印,sot类为焊盘)极限间距为:

0.76mm

分别为图示中亮线所示距离

因此,我们根据上诉规则也可在Allergo的Cns中进行设置:

这样进行手工添加测试孔时即可在线DRC了。

EDA设计部西安设计室

2005.05