实验三实现Tomasulo算法模拟器.docx

《实验三实现Tomasulo算法模拟器.docx》由会员分享,可在线阅读,更多相关《实验三实现Tomasulo算法模拟器.docx(15页珍藏版)》请在冰豆网上搜索。

实验三实现Tomasulo算法模拟器

实验三实现Tomasulo算法模拟器

一、实验目的

1.加深对指令级并行性及其开发的理解;

2.加深对Tomasulo算法的理解;

3.掌握Tomasulo算法在指令流出、执行、写结果各阶段对浮点操作指令以及load和store指令进行什么处理;

4.掌握采用了Tomasulo算法的浮点处理部件的结构;

5.掌握保留站的结构;

6.给定被执行代码片段,对于具体某个时钟周期,能够写出保留站、指令状态表以及浮点寄存器状态表内容的变化情况。

二、实验要求

设计和实现一个Tomasulo算法模拟器。

1.基本要求:

针对程序中直线型代码,可乱序执行、乱序完成。

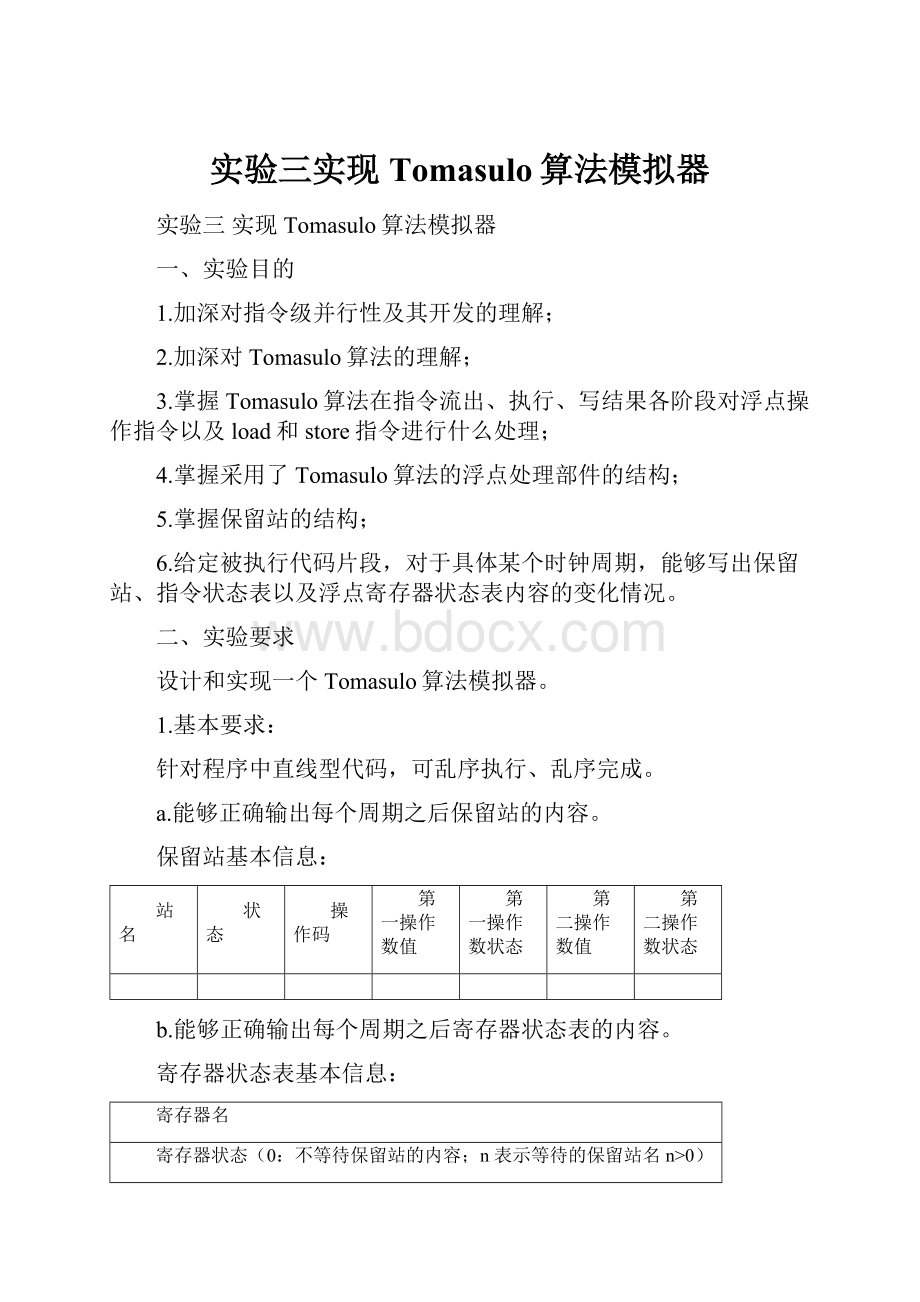

a.能够正确输出每个周期之后保留站的内容。

保留站基本信息:

站名

状态

操作码

第一操作数值

第一操作数状态

第二操作数值

第二操作数状态

b.能够正确输出每个周期之后寄存器状态表的内容。

寄存器状态表基本信息:

寄存器名

寄存器状态(0:

不等待保留站的内容;n表示等待的保留站名n>0)

寄存器内容(状态为0时,该值才有意义)

c.能够正确输出每个周期之后指令状态表的内容(指令分为浮点运算指令和load/store指令),指令状态分为流入,执行和写回。

指令状态表基本信息

标志出每条指令流出、执行、写回这三个阶段所在的周期号

2.较高要求:

a.实现带界面的模拟器,可动态输入指令并配置相关信息(e.g指令各个状态周期数,运算部件数目),并能正确输出上述基本要求中的相关信息。

b.实现带“再定序缓冲”的Tomasula算法模拟器,支持分支指令

三、实验报告

1.给定指令流输入测试

L.DF6,21(R2)

L.DF2,20(R3)

MUL.DF0,F2,F4

SUB.DF8,F6,F2

DIV.DF10,F0,F6

ADD.DF6,F8,F2

假设浮点功能部件的延迟时间:

加减法2个周期,乘法10个周期,load/store2个周期,除法40个周期。

而指令的流入和写回为1个周期。

a.给出第5个时钟周期后保留站的内容:

算法模拟器模板——保留站内容:

算法模拟器个人——保留站内容:

分析:

第5个时钟周期流出了5条指令,其中load指令2条,mult指令1条,sub指令1条,divd指令1条。

其中mult和sub指令与ld产生相关,相关寄存器编号为F2。

M1与M2代表寄存器F6和F2数据已准备好。

2条load指令执行完毕并且已经写回。

b.给出在第10个周期后,保留站,寄存器状态表的信息

算法模拟器模板——保留站内容:

算法模拟器个人——保留站内容:

算法模拟器模板——寄存器状态表信息:

算法模拟器个人——寄存器状态表信息:

分析:

第10个时钟周期6条指令均已流出,且2条load指令执行完毕并且写回。

sub指令也已执行完毕并写回,目前保留站中剩下add、mult、div3条指令。

add指令正在执行阶段最后一个时钟周期,没有写回。

div指令等待mult指令的结果。

乘法指令还有5个时钟周期执行完毕。

2.实验设计思想

(1).模块划分及类成员定义

由所给条件可知,界面点击执行按钮后,自动弹出4个界面,一个load缓存站,一个保留站,一个寄存器状态信息表和一个指令状态信息表。

因此,为这四个模块设计五个类:

a.LoadStation

定义成员:

缓存站名称Qi,当前组件状态Busy,地址计算Addr,立即数或计算结果value。

b.ReservationStation

定义成员:

当前保留站名称Qi,指令操作的类型Op,当前保留站工作状态Busy,第一个源操作数Vj,第二个源操作数Vk,产生第一个源操作数的保留站名称Qj,产生第二个源操作数的保留站名称Qk。

c.RegisterStation

定义成员:

以当前寄存器为目的操作寄存器的保留站或缓存站名称Qi,寄存器名称state,寄存器中的值value。

d.Instruction

定义成员:

当前指令名称name,目的操作寄存器opr1,源操作数一opr2,源操作数二opr3。

e.InstructionStation

定义成员:

当前指令所在保留站或缓存站名称Qi,当前指令所处的状态state,指令执行所需要的时间,关联指令队列中的指令instruction。

以上5个类中,4个与Jpanel相关,只有InstructionStation(指令状态)为控制类,包含控制成员state。

并在公有方法init()中初始化类为对象,并赋初值。

如下图(图中包含注释说明):

(2).算法设计

算法设计的第一阶段为流程划分:

根据指令流入的方式、执行方式以及写回方式,初期定义为三个阶段,第一阶段为发射阶段,第二阶段为执行阶段,第三阶段为写回阶段。

在细化设计的过程中,执行阶段被分为两个过程,第一个过程为开始执行指令,第二个过程为完成执行指令。

表现在面板中为两次刷新,第一次刷新设置开始时间+“->”,第二次刷新加上完成时间。

因此,算法过程被细化为四个流程

a.发射

b.执行1

c.执行2

d.写回

a.发射阶段流程说明

1)获取当前发射指令

循环查询指令队列,取序号最小的指令。

根据指令类型循环查询保留站或缓存站,如有空闲为(Busy=no),发射指令。

下图为遍历指令队列,查询适合发射的指令。

空闲保留站查询方法图置于第2小点中。

2)根据指令类型分类处理

第一类为Load指令:

上图中第一步判断是否有可用的空闲load缓存站,下图说明判断方法。

若存在空闲位,则继续执行。

赋值说明:

设置Busy位为yes,将指令中第一个源操作数赋值给缓存站value位,load指令中表示立即数,将保留站名称赋值给指令状态中的Qi,保存该指令的当前物理位置。

第二类为Float运算指令:

同样的,先查询是否存在空闲保留站。

运算部分发射阶段代码较多,不过大部分为不同位的设置,流程相同。

赋值说明1:

将使用的保留站Busy位置为yes,将该指令的名称赋值给保留站对象Op成员,并在面板中显示。

循环查询源操作数来源,如果有前序指令的目的寄存器值作为源操作数,将其保留站值赋予Qj或Qk。

以上方法通过查询寄存器表实现。

如下图

赋值说明2:

如果寄存器表中对应的值还没有计算出对应的结果,则获取产生结果的保留站名称。

如果结果已计算出,则直接将结果值写入Vj或者Vk。

若无寄存器相关,则直接将操作的寄存器名称赋给Vj或者Vk。

下图为获取发射指令的目的寄存器名称,并在寄存器状态表中更新。

最后一步为修改指令状态并显示当前发射周期。

b.执行1阶段流程说明

第一类指令load:

赋值说明1:

当load缓存站中的名称与指令对应的名称相匹配,开始执行,对于load指令来说是计算访存地址。

并将改地址结果存在缓存站对应的Addr。

下图为load指令执行时间每时钟递减的判断执行函数。

如执行时间值依旧大于0,则显示执行过程提示:

开始时间+“->”。

如执行时间等于0,则进入指令完成状态。

并获取当前时钟周期。

第二类指令float运算:

赋值说明1:

float运算进行的条件是两个源操作数Vi和Vk都有值,执行时只需将剩余执行时间显示在time栏用于显示递减过程即可。

下图为执行时间递减,与load相似,不做分析。

c.执行2阶段流程说明

第一类指令load:

将计算结果赋值给load缓存站中的value值。

执行时间减一,如执行时间为0,则将当前时钟周期值显示并且设置状态为3。

如下图。

第二类指令float运算:

将当前剩余执行时间值显示在面板中。

下图为时间值为0时的time的清零操作。

d.写回阶段流程说明

第一类指令load:

写回阶段刷新load站,重新将Busy设置为no,其他值置空。

第二类指令float运算:

刷新保留站,Busy设置为no,其他值置空。

下图为写回完毕后执行的更新寄存器和修改保留站中目的寄存器的操作。

赋值说明:

对于寄存器,将计算结果值置为M+m。

对于保留站,将Vj或者Vk赋予寄存器表中的值,而Qj或者Qk置为空值。

3.实验结果分析

选取两条指令以特定的时钟周期分析

MUL.DF0,F2,F4

SUB.DF8,F6,F2

(1)选取第4个时钟周期

两条指令均已流出。

此时保留站显示其需要Load2,Load1的值已完成存储为M1。

此时寄存器状态表,Load2还未有值写回。

此时Load缓存站,Load2完成计算地址的过程,将要写回。

(2)选取第6个时钟周期

两条指令均已开始执行。

寄存器中Load1和Load2均已准备好

保留站:

mult指令还剩余9个执行周期,sub指令还剩余1个执行周期