2812寄存器映射.docx

《2812寄存器映射.docx》由会员分享,可在线阅读,更多相关《2812寄存器映射.docx(23页珍藏版)》请在冰豆网上搜索。

2812寄存器映射

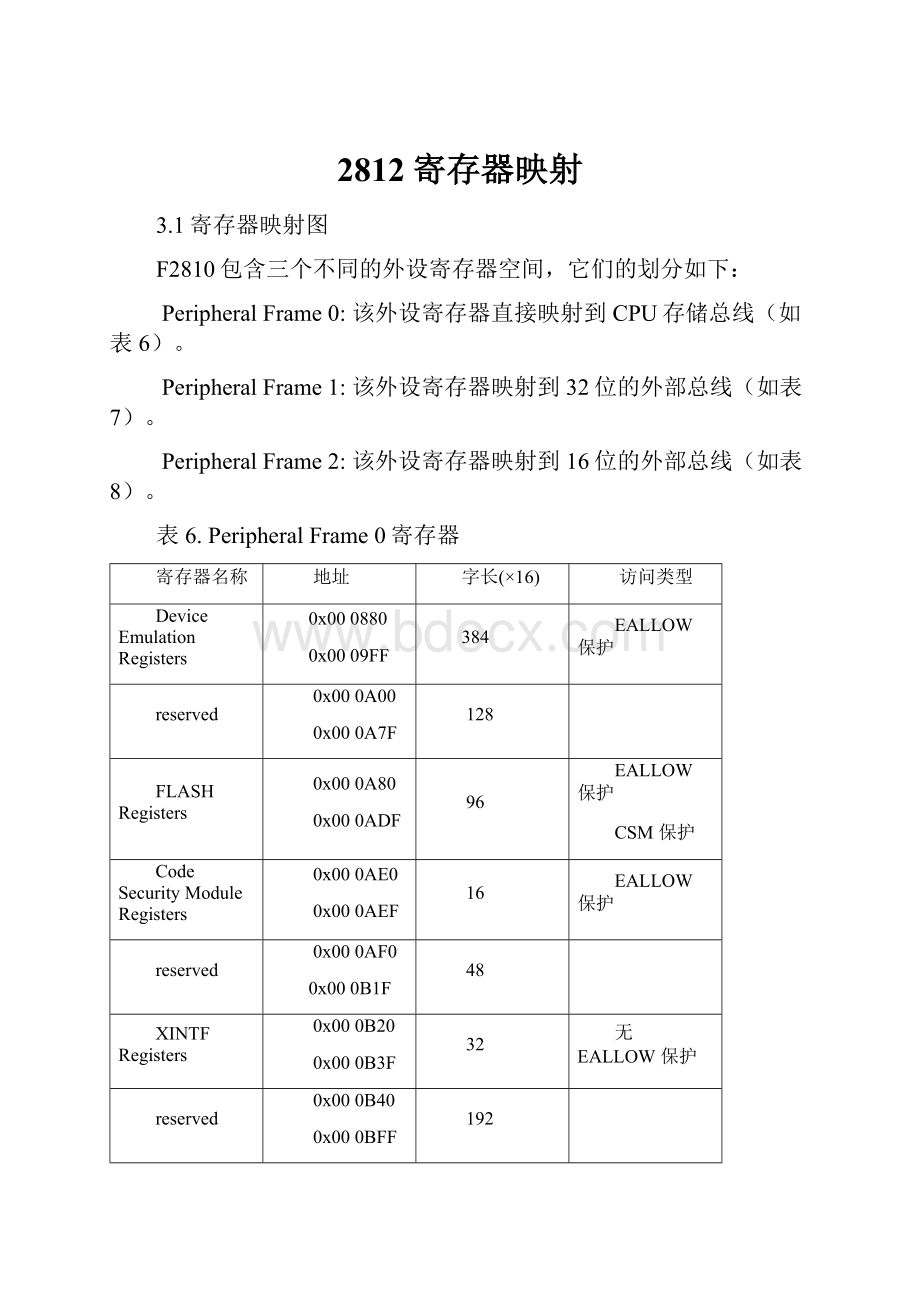

3.1寄存器映射图

F2810包含三个不同的外设寄存器空间,它们的划分如下:

PeripheralFrame0:

该外设寄存器直接映射到CPU存储总线(如表6)。

PeripheralFrame1:

该外设寄存器映射到32位的外部总线(如表7)。

PeripheralFrame2:

该外设寄存器映射到16位的外部总线(如表8)。

表6.PeripheralFrame0寄存器

寄存器名称

地址

字长(×16)

访问类型

DeviceEmulationRegisters

0x000880

0x0009FF

384

EALLOW保护

reserved

0x000A00

0x000A7F

128

FLASHRegisters

0x000A80

0x000ADF

96

EALLOW保护

CSM保护

CodeSecurityModuleRegisters

0x000AE0

0x000AEF

16

EALLOW保护

reserved

0x000AF0

0x000B1F

48

XINTFRegisters

0x000B20

0x000B3F

32

无EALLOW保护

reserved

0x000B40

0x000BFF

192

CPU-TIMER0/1/2Registers

0x000C00

0x000C3F

64

无EALLOW保护

reserved

0x000C40

0x000CDF

160

PIERegisters

0x000CE0

0x000CFF

32

无EALLOW保护

PIEVectorTable

0x000D00

0x000DFF

256

EALLOW保护

reserved

0x000E00

0x000FFF

512

1.在Frame0中的寄存器允许16位和32位的数据访问。

2.如果寄存器处于EALLOW保护,数据将不能写入,除非用户执行EALLOW指令。

而执行EDIS指令将禁止写操作。

这样就可以阻止偏移代码损坏寄存器内容。

3.flash程序存储器受代码安全模块保护(CSM)。

表7.PeripheralFrame1寄存器

寄存器名称

地址

字长(×16)

访问类型

eCANRegisters

0x006000

0x0060FF

256

(128×32)

某些eCAN控制寄存器(和其它eCAN控制寄存器中的某些位)有EALLOW保护

eCANMailboxRAM

0x006100

0x0061FF

256

(128×32)

无EALLOW保护

reserved

0x006200

0x006FFF

3584

1.eCAN控制寄存器只允许32位的读写操作。

表8.PeripheralFrame2寄存器

寄存器名称

地址

字长(×16)

访问类型

reserved

0x007000

0x00700F

16

SystemControlRegissters

0x007010

0x00702F

32

EALLOW保护

reserved

0x007030

0x00703F

16

SPI-ARegisters

0x007040

0x00704F

16

无EALLOW保护

SCI-ARegisters

0x007050

0x00705F

16

无EALLOW保护

reserved

0x007060

0x00706F

16

ExternalinterruptRegisters

0x007070

0x00707F

16

无EALLOW保护

reserved

0x007080

0x0070BF

64

GPIOMuxRegisters

0x0070C0

0x0070DF

32

EALLOW保护

GPIODataRegisters

0x0070E0

0x0070FF

32

无EALLOW保护

ADCRegisters

0x007100

0x00711F

32

无EALLOW保护

reserved

0x007120

0x0073FF

736

EV-ARegisters

0x007400

0x00743F

64

无EALLOW保护

reserved

0x007440

0x0074FF

192

EV-BRegisters

0x007500

0x00753F

64

无EALLOW保护

reserved

0x007540

0x00774F

528

SCI-BRegisters

0x007750

0x00775F

16

无EALLOW保护

reserved

0x007760

0x0077FF

160

McBSPRegisters

0x007800

0x00783F

64

无EALLOW保护

reserved

0x007840

0x007FFF

1984

1.PeripheralFrame2仅允许16位数据的访问。

所有32位的数据访问都被忽略(无效的数据可能会返回或写入)。

3.2仿真控制寄存器

这些寄存器主要用于控制C28×CPU的保护模式,和监测某些重要设备的信号。

寄存器定义如表9。

表9.仿真控制寄存器

寄存器名称

地址

字长(×16)

描述

DEVICECNF

0x000880

0x000881

2

控制器的配置寄存器

DEVICEID

0x000882

0x000883

2

控制器的ID寄存器

PROTSTART

0x000884

1

保护模块首地址寄存器

PROTRANGE

0x000885

1

保护模块地址范围寄存器

reserved

0x000886

0x0009FF

378

表10.DEVICECNF寄存器各位的定义

位

名称

方式

复位

描述

1:

0

reserved

R/W

1,1

仅供测试用

2

reserved

R=0

0

3

VMAPS

R

0/1

VMAP配置状态位说明VMAP状态

4

reserved

R=0

0

5

R

0/1

复位输入信号状态,直接和

输入引脚相连

6

reserved

R=1

1

7

reserved

R/W

0

14:

8

reserved

R=0

0:

0

15

reserved

R/W

0

仅供测试用

16

reserved

R=1

1

17

reserved

R=1

1

18

reserved

R=1

1

19

ENPROT

R/W

1

使能读写保护模式位,该位置1

时,按照PROSTART和PROTRANGE寄存器规定开启读写保护模式;

该位置0时,禁止该保护模式

31:

20

spares

R=0

0

表11.DEVICEID寄存器各位的定义

位

名称

方式

复位

描述

15:

0

PARTID

R

由控制器决定

这16位用来说明不同型

号的控制器,具体如下:

0x0001:

F2810控制器

0x0002:

F2812控制器

31:

16

REVID

R

0x000

(forfirstsilicon)

这16位用来对特别部分的硅的修订数目说明,这个数目总是从?

的0x0000开始,逐步递增

在PROSTART和PROTRANGE寄存器设定的保护模块的存储器地址范围中,CPU的读操作是跟在写操作的后面(操作是按指令次序执行,而不是按指令的流水线执行)。

这对于某些外围操作的保护是必须的。

例:

下面的代码段执行对寄存器1(REG1)的写操作,然后对寄存器2(REG2)的读操作。

在处理器的存储总线上,当模块保护被禁止,读操作将在写操作之前被执行,如下所示:

MOV@REG1,AL--------+

TBIT@REG2,#BIT_X--------|------>Read

+----->Write

如果模块保护被使能,读操作将在写操作之后执行,如下所示:

MOV@REG1,AL--------+

TBIT@REG2,#BIT_X----+|

|+------->Write

+----------->Read

注:

C28×CPU对同一个储存地址自动在读操作之前进行写操作。

而上面描述的保护机制主要针对不是同一个地址,但是在一个给定的存储区域(它是由PROTSTART和PROTRANGE寄存器定义的)。

表12.PROTSTART和PROTRANGE寄存器

寄存器名称

地址

位

方式

复位

描述

PROTSTART

0x000884

16

R/W

0x0100

PROTSTART寄存器确定其模块的首地址,它是与处理器低22位地址中的16个重要位有关

PROTRANGE

0x000885

16

R/W

0x00FF

PROTRANGE寄存器确定模块的大小(从首地址开始),从64个字长,以2的倍数增加(64,128,256,512,1K,2K,4K,8K,16K,…,2M)

注:

这些寄存器在复位后的预设值用来覆盖存储器中的外围帧1,2和XINTF1的区域

表13.PROTSTART有效值

寄存器各位值

模块首地址

寄存器值

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

0X000000

0X0000

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0X000040

0X0001

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

1

0X000080

0X0002

0

0

0

0

0

0

0

0

0

0

0

0

0

0

1

0

0X0000C0

0X0003

0

0

0

0

0

0

0

0

0

0

0

0

0

0

1

1

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

0X3FFF00

0XFFFC

1

1

1

1

1

1

1

1

1

1

1

1

1

1

0

0

0X3FFF40

0XFFFD

1

1

1

1

1

1

1

1

1

1

1

1

1

1

0

1

0X3FFF80

0XFFFE

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

0

0X3FFFC0

0XFFFF

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

注:

最快估计寄存器值的算法是将有效模块的首地址除以64(十进制)。

表14.PROTRANGE有效值

寄存器各位值

模块大小

寄存器值

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

64

0X0000

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

128

0X0001

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

1

256

0X0003

0

0

0

0

0

0

0

0

0

0

0

0

0

0

1

1

512

0X0007

0

0

0

0

0

0

0

0

0

0

0

0

0

1

1

1

1K

0X000F

0

0

0

0

0

0

0

0

0

0

0

0

1

1

1

1

2K

0X001F

0

0

0

0

0

0

0

0

0

0

0

1

1

1

1

1

4K

0X003F

0

0

0

0

0

0

0

0

0

0

1

1

1

1

1

1

8K

0X007F

0

0

0

0

0

0

0

0

0

1

1

1

1

1

1

1

16K

0X00FF

0

0

0

0

0

0

0

0

1

1

1

1

1

1

1

1

32K

0X01FF

0

0

0

0

0

0

0

1

1

1

1

1

1

1

1

1

64K

0X03FF

0

0

0

0

0

0

1

1

1

1

1

1

1

1

1

1

128K

0X07FF

0

0

0

0

0

1

1

1

1

1

1

1

1

1

1

1

256K

0X0FFF

0

0

0

0

1

1

1

1

1

1

1

1

1

1

1

1

512K

0X1FFF

0

0

0

1

1

1

1

1

1

1

1

1

1

1

1

1

1M

0X3FFF

0

0

1

1

1

1

1

1

1

1

1

1

1

1

1

1

2M

0X7FFF

0

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

4M

0XFFFF

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

注:

不是所有的寄存器值都是有效的,PROSTART表示的首地址值必须是地址范围值的倍数。

例如:

如果一个模块的大小设为4K,那么首地址只能在4K的边界处。

3.3系统配置器设置

本节主要介绍系统的各种配置寄存器的地址和功能,并对配置寄存器内的各位值进行了详细的说明。

图9显示各种不同时钟和复位信号

注:

CLKIN是输入到CPU时钟信号,SYSCLKOUT是CPU的输出时钟,两者频率相同。

图9。

时钟和复位图

锁相环,时钟,看门狗和低功率模块受表33中寄存器控制

表33.锁相环,时钟,看门狗和低功率模块寄存器

寄存器名

地址

字长(×16)

功能描述

reserved

0x007010

0x007017

8

reserved

0x007018

1

reserved

0x007019

1

HISPCP

0x00701A

1

高速外围时钟对HSPCLK时钟的预定选择寄存器

LOSPCP

0x00701B

1

低速外围时钟对HSPCLK时钟的预定选择寄存器

PCLKCR

0x00701C

1

外围时钟控制寄存器

reserved

0x00701D

1

LPMCR0

0X00701E

1

低功率模式控制寄存器0

LPMCR1

0X00701F

1

低功率模式控制寄存器1

reserved

0x007020

1

PLLCR

0x007021

1

锁相环控制寄存器

SCSR

0x007022

1

系统控制和状态寄存器

WDCNTR

0x007023

1

看门狗计数寄存器

reserved

0x007024

1

WDKEY

0x007025

1

看门狗复位关键字寄存器

reserved

0x007026

0x007028

3

WDCR

0x007029

1

看门狗控制寄存器

reserved

0x00702A

0x00702F

6

注:

1.上面的寄存器仅当执行EALLOW指令时,才能被访问。

2.锁相环控制寄存器(PLLCR)仅通过

信号复位一个已知状态。

PCLKCR寄存器主要是针对F2810和F2812控制器的各种外围模块,使能/禁止其时钟信号。

表34对PCLKCR各位进行了说明。

表34.PCLKCR寄存器各位定义

位

名称

方式

复位

描述

0

EVAENCLK

R/W

0

如果该位被置位,它将给EV-A模块提供高速的时钟(HSPLCK)。

对于低功率的操作,该位通过手动或复位置0

1

EVBENCLK

R/W

0

如果该位被置位,它将给EV-B模块提供高速的时钟(HSPLCK)。

对于低功率的操作,该位通过手动或复位置0

2

reserved

R=0

0

保留位

3

ADCENCLK

R/W

0

如果该位被置位,它将给ADC模块提供高速的时钟(HSPLCK)。

对于低功率的操作,该位通过手动或复位置0

7:

4

reserved

R=0

0:

0

8

SPIAENCLK

R/W

0

如果该位被置位,它将给SPI模块提供低速的时钟(LSPLCK)。

对于低功率的操作,该位通过手动或复位置0

9

reserved

R=0

0

保留位

10

SCIAENCLK

R/W

0

如果该位被置位,它将给SCI-A模块提供低速的时钟(LSPLCK)。

对于低功率的操作,该位通过手动或复位置0

11

SCIBENCLK

R/W

0

如果该位被置位,它将给SCI-B模块提供低速的时钟(LSPLCK)。

对于低功率的操作,该位通过手动或复位置0

12

MCBSPENCLK

R/W

0

如果该位被置位,它将给McBSP模块提供低速的时钟(LSPLCK)。

对于低功率的操作,该位通过手动或复位置0

13

reserved

R=0

0

保留位

14

ECANENCLK

R/W

0

如果该位被置位,它将给CAN模块提供系统时钟。

对于低功率的操作,该位通过手动或复位置0

15

reserved

R=0

0

保留位

注:

如果外围模块没有被使用,那么该模块的时钟被关掉,节约能量。

系统控制和状态寄存器包含看门狗溢出位和看门狗中断使能/禁止位。

表35描述了SCSR寄存器各位的功能。

表35.SCSR寄存器各位定义

位

名称

方式

复位

描述

0

WDOVERRIDE

R/W=1

1

如果该位置1,用户可以改变WDCR寄存器中的WDDIS位来禁止WD工作(可参考后面的看门狗模块);如果该位被清0,它将保持到下一次复位出现,可通过向这一位写1来清0。

用户可以对该位进行读取。

1

WDENINT

R/W

0

如果该位置1,看门狗复位(

)输出信号被禁止,而看门狗中断(

)输出信号被使能;如果该位置0,看门狗复位(

)输出信号被使能,而看门狗中断(

)输出信号被禁止。

置0是复位的预设值(

)

2

WDINTS

R

1

看门狗中断状态位。

该位反映了看门狗模块中的

信号的当前状态。

15:

3

reserved

R=0

0:

0

HISPCP和LOSPCP寄存器用来配置各自的高/低速外围时钟。

见表36和表37,前者是对HISPCP各位的定义,后者是对LOSPCP各位的定义。

表36.HISPCP寄存器各位定义

位

名称

方式

复位

描述

2:

0

HSPLCK

R/W

0,0,1

这些位配置高速外围时钟对系统时钟频率的选择

000HSPCLK=SYSCLKOUT/1

001HSPCLK=SYSCLKOUT/2

010HSPCLK=SYSCLKOUT/4

011HSPCLK=SYSCLKOUT/6

100HSPCLK=SYSCLKOUT/8

101HSPCLK=SYSCLKOUT/10

110HSPCLK=SYSCLKOUT/12

111HSPCLK=SYSCLKOUT/14

HSPCLK=SYSCLKOUT/(HSPCLK×2)

=SYSCLKOUT(当HISPCP值为0时)

15:

3

reserved

R=0

0:

0

表37.LOSPCP寄存器各位定义

位

名称

方式

复位

描述

2:

0

LSPLCK

R/W

0,1,0

这些位配置低速外围时钟对系统时钟频率的选择

000LSPCLK=SYSCLKOUT/1

001LSPCLK=SYSCLKOUT/2

010LSPCLK=SYSCLKOUT/4

011LSPCLK=SYSCLKOUT/6

100LSPCLK=SYSCLKOUT/8

101LSPCLK=SYSCLKOUT/10

112LSPCLK=SYSCLKOUT/12

113LSPCLK=SYSCLKOUT/14

LSPCLK=SYSCLKOUT/(LSPCLK×2)

=SYSCLKOUT(当LOSPCP值为0时)

15:

3

reserved

R=0

0:

0

注:

在复位后,HSPCLK时钟频率为SYSCLKOUT的1/2,LSPCLK时钟频率为SYSCLKOUT的1/4

3.4中断和中断源

3.4.1中断的概念

“中断”是处理器与外部设备交换信息的一种方式。

处理器在执行正常程序的过程中,当现某些异常事件或某些外部请求时,处理器就暂时中断正在执行的正常程序,而转去执行对异常事件或某种外设请求的处理操作。

当处理完毕后,CPU再回到被暂时中断的程序,接着往下继续执行。

这个过程称为中断。

中断是用以提高计算机工作效率的一种手段,能较好地发挥处理器的能力。

通常,DSP的运算速度相当高,一条指令的平均时间以纳秒为单位,因此,快速的CPU与慢速的外设设备在传送数据的速率上存在着矛盾。

这样采用中断技术后,仅当外设设备完成一个输入输出操作后,才向CPU请求中断。

这样CPU在大部分时间