计算机组成原理课程设计实验报告分解.docx

《计算机组成原理课程设计实验报告分解.docx》由会员分享,可在线阅读,更多相关《计算机组成原理课程设计实验报告分解.docx(13页珍藏版)》请在冰豆网上搜索。

计算机组成原理课程设计实验报告分解

计算机组成原理课程设计实验报告

实验一

一、实验名称

验证74LS181运算和逻辑功能。

二、实验目的

(1)掌握算术逻辑单元(ALU)的工作原理;

(2)熟悉简单运算器的数据传送通路;

(3)画出逻辑电路图及布出美观整齐的接线图;

(4)验证4位运算功能发生器(74LS181)组合功能。

三、实验原理

ALU(算术逻辑单元)能进行多种算术运算和逻辑运算。

一个4位的ALU—74LS181运算功能发生器能进行16种算术运算和逻辑运算。

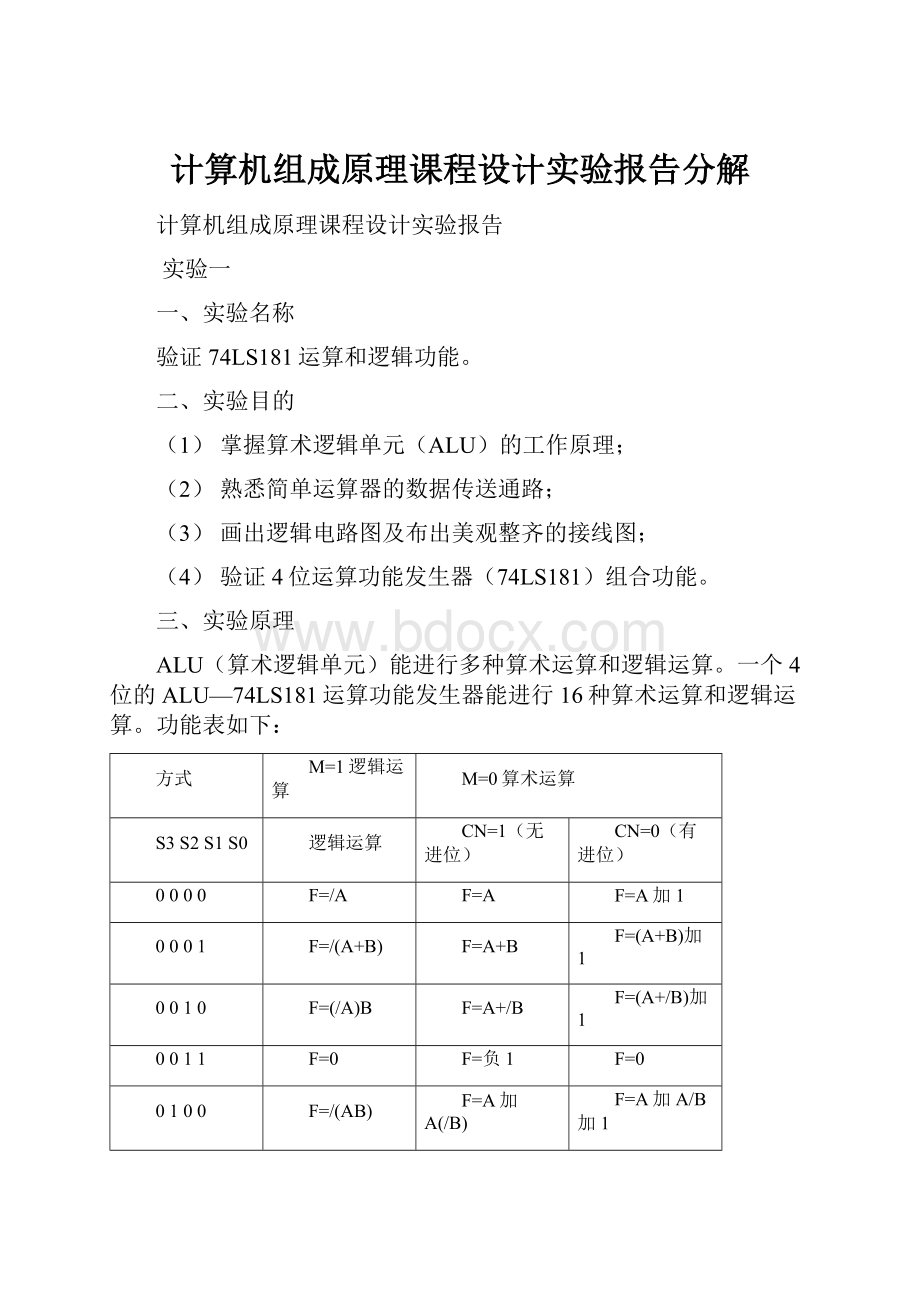

功能表如下:

方式

M=1逻辑运算

M=0算术运算

S3S2S1S0

逻辑运算

CN=1(无进位)

CN=0(有进位)

0000

F=/A

F=A

F=A加1

0001

F=/(A+B)

F=A+B

F=(A+B)加1

0010

F=(/A)B

F=A+/B

F=(A+/B)加1

0011

F=0

F=负1

F=0

0100

F=/(AB)

F=A加A(/B)

F=A加A/B加1

0101

F=/B

F=(A+B)加A/B

F=(A+B)加A/B加1

0110

F=A⊕B

F=A减B减1

F=A减B

0111

F=A/B

F=A(/B)减1

F=A(/B)

1000

F=/A+B

F=A加AB

F=A加AB加1

1001

F=/(A⊕B)

F=A加B

F=A加B加1

1010

F=B

F=(A+/B)加AB

F=(A+/B)加AB加1

1011

F=AB

F=AB减1

F=AB

1100

F=1

F=A加A

F=A加A加1

1101

F=A+/B

F=(A+B)加A

F=(A+B)加A加1

1110

F=A+B

F=(A+/B)加A

F=(A+/B)加A加1

1111

F=A

F=A减1

F=A

(上表中的“/”表示求反)

ALU—74LS181引脚说明:

M=1逻辑运算,M=0算术运算

引脚

说明

M状态控制端

M=1逻辑运算;M=0算术运算

S3S2S1S0运算选择控制

S3S2S1S0决定电路执行哪一种算术

A3A2A1A0

运算数1,引脚3为最高位

Cn最低位进入输入

Cn=0有进位,Cn=1无进位

Cn+4本片产生的进位信号

Cn+4=0有进位,Cn+4=1无进位

F3F2F1F0

F3F2F1F0运算结果,F3为最高位

四、实验内容

1、首先看懂74LS181各个引脚的功能;

8个数据输入端(~A0、~A1、~A2、~A3,~B0、~B1、~B2、~B3,其中八个输入端中A3和B3是高位)。

四个控制端S0、S1、S2、S3,这四个控制端主要控制两个四位输入数据的运算,例如加、减、与、或。

CN端处理进入芯片前进位值,M控制芯片进行算术运算还是逻辑运算。

F0、F1、F2、F3是四个二进制输出端。

2、画出4位ALU验证示意图;

3、对实验数据进行验证:

验证74LS181型4位ALU的逻辑算术功能,填写下表:

S3S2S1S0

数据1

数据2

算术运算(M=0)

逻辑运算(M=1)

CN=1

CN=0

0000

AH

5H

F=AH

F=BH

F=5H

0001

AH

5H

F=FH

F=0H

F=0H

0010

AH

5H

F=AH

F=BH

F=5H

0011

AH

5H

F=FH

F=0H

F=0H

0100

FH

1H

F=DH

F=EH

F=EH

0101

FH

1H

F=DH

F=EH

F=EH

0110

FH

1H

F=DH

F=EH

F=EH

0111

FH

1H

F=DH

F=EH

F=EH

1000

FH

FH

F=EH

F=FH

F=FH

1001

FH

FH

F=EH

F=FH

F=FH

1010

FH

FH

F=EH

F=FH

F=FH

1011

FH

FH

F=EH

F=FH

F=FH

1100

5H

5H

F=AH

F=BH

F=FH

1101

5H

5H

F=AH

F=BH

F=FH

1110

5H

5H

F=4H

F=5H

F=5H

1111

5H

5H

F=4H

F=5H

F=5H

五、总结及心得体会

此次实验通过一个简单运算器的形式,让我掌握电路设计和分析的方法和能力;清楚的明白了74LS181芯片各个引脚的功能,知道如何通过控制开关来进行各种运算。

这个实验也为我接下来进行实验二打下了坚实的基础。

不至于在纷繁的电路图中迷失方向,只有弄明白个个芯片的功能及如何控制,才会得出正确的结果。

实验二

一、实验名称

运算器

2、实验目的

(1)熟练掌握算术逻辑单元的应用方法;

(2)进一步熟悉简单运算器的数据传送原理;

(3)画出逻辑电路图及布出美观整齐的接线图;

(4)熟练掌握有关数字元件的功能和使用方法;

(5)熟练掌握子电路的创建及使用。

三、实验原理

本实验仿真单总线结构的运算器,原理如图所示。

电路图中,上右下三方的8条模拟8位数据总线;K8产生所需数据;74244层次块为三态门电路将部件与总线连接或断开,切忌总线上只能有一个输入;两个74273层次块作为暂存工作寄存器DR1和DR2;两个74374层次块作为通用寄存器组;众多的开关作为控制电平或打入脉冲;众多的8段代码管显示相应位置的数据信息;核心为8位ALU层次块。

四、实验内容

(1)说明整个电路工作原理;

芯片X1,X2控制数据输入;左边的一组开关是控制各个模块的是否存储数据;芯片X6和X7分别控制暂存工作寄存器X3和X12的数据输入;显示器U19与U20,U23与U24显示芯片X6,X7输出数据;显示器U21与U22,U25与U26显示暂存工作寄存器X3和X12的中储存的数据;X6、X7、X3、X12构成的模块的功能是存储即将运算的数据;芯片X4和X8作为通用工作寄存器是用来存储数据,显示器U27与U28,U31与U32显示芯片X4,X8中存储的数据;芯片X5,X11是运算处理模块,通过控制右边的开关来控制由X3、X12输入的数据进行各个运算;显示器U29与U30是用来显示数据运算结果的。

(2)说明74LS244N的功能及其在电路中作用,及输入信号G有何作用;74LS244N三态门电路,主要用于将部件与总线连接或断开,从而设置各个寄存器的值,切记总线只有一个输入;输入信号G是使能控制端,低电平有效。

(3)说明74LS273N的功能及其在电路中作用,及输入信号CLK有何作用;

74LS273部件作为暂存工作寄存器,暂时保存要进行运算的信号。

CLR的作用即清零,清除保存到该寄存器的信号。

(4)说明74LS374N的功能及其在电路中作用,及输入信号CLK和OC的作用;

74374部件作为通用寄存器GR1和GR2,在此电路中是保存和传送信号。

OC的作用是OUTPUTCONTROL控制输出。

(5)K8产生如任意数据存入通用寄存器GR1;

通过双击与74LS273(0)相连的单脉冲,即把数据存入到了GR1,并在相应的LED上显示出来。

(6)K8产生如任意数据存入通用寄存器GR2;

同(5)。

(7)完成GR1+GR2→GR1;

(8)GR1-GR2→GR2;

(9)GR1∧GR2→GR1;

(10)GR1∨GR2→GR2;

(11)GR1⊕GR2→GR1;

(12)~GR1→GR2;

(13)~GR2→GR1。

运算公式

数据

S3S2S1S0

CN

M

GR1+GR2→GR1

12+23=35

1001

1

0

GR1-GR2→GR2

32-23=12

0110

0

0

GR1∧GR2→GR1

35∧12=10

1011

X

1

GR1∨GR2→GR2

10∨12=12

1110

X

1

GR1⊕GR2→GR1

10⊕12=02

0110

X

1

~GR1→GR2

~02=FD

0000

X

1

~GR2→GR1

~FD=02

0101

X

1

五、总结及心得体会

这次实验的内容是简单运算器的设计和使用,本次实验室主要要求是掌握三态门的使用和原理,掌握暂存工作寄存器74LS273N的原理和使用以及掌握通用寄存器74LS374的原理和运用。

需要注意的是本次试验所用到的所有芯片的时钟信号均是低电平有效的。

需要强调的是任何时候数据总线上必须只有一个数据信号。

通过本次实验,我较为熟练地掌握了算术逻辑单元(ALU)的应用方法,并且清楚的理解和掌握了简单运算器的数据传送原理,对于74LS273、74LS374和74LS181这三块芯片也有了系统地掌握,一个最大的收获就是熟悉了如何创建子电路和使用子电路。

这为我进行实验三提供了宝贵经验。

实验三

1、实验名称

乘法实现

2、实验目的

本实验为开放性实验,根据原理图实现乘法的电路设计及运行。

实现4位*4位的乘法。

3、实验原理

如图是实现原码一位乘法运算的基本硬件配置框图,根据改图用移位相加方法实现乘法,自行选择器件设计电路并运行。

原码一位乘法运算的基本硬件配置图

原码一位乘法运算的基本硬件配置图

本次实验选用74LS181作为加法器,用74LS194作为移位寄存器,手动开关作为计数器,实现4位*4位的乘法。

4、实验内容

(1)说明整个电路工作原理;

有两组开关分别控制乘数与被乘数的数据输入;U1674LS273N对乘数进行右移(第一次不要右移,只要控制开关录入数据),其中SL控制端是用来控制乘数右移添1或0也就是把部分积的最后一位进行保存;U1674LS273N输出的最后一位输入U1574LS181N到与被乘数进行相乘,这是为了控制与部分积相加的数;U974LS181N是进行求部分积的运算,U574LS194N与U1174LS274N对部分积进行移位与保存;U6显示器显示结果前4位的16进制的表示,U18显示器显示后4位的16进制的表示。

(2)加法器模块及后4位输出模块

U1674LS273N对乘数进行右移(第一次不要右移,只要控制开关录入数据即可),加法器U974LS181N把把部分积的最后一位链接到U574LS194N的SL端(SL控制端是用来控制乘数右移添1或0)也就是把部分积的最后一位进行保存;U1674LS273N输出的最后一位输入U1574LS181N到与被乘数进行相乘,这是为了控制与部分积相加的数。

(3)部分积的运算模块

U974LS181N作为加法器,输出端CN4是进位端,可以把进位取反后作为最高位直接保存,不用移位。

U574LS194N作为移位寄存器只移后3位;最后把结果输入到U574LS273N储存。

五、总结及心得体会

本次实验主要考察队芯片的理解运用,设计电路的模块分析以及整个电路的连贯性,应当注意的是芯片的使用过程中的芯片工作电平有效状态。

本实验尚有缺陷存在,由于本实验为添加符号产生模块S,所以原理图只能支持整数运算而不支持小数的乘法运算。

通过本次实验,我真正地理解了各个芯片的功能、作用以及应用,整个电路设计需要耐心和细心,切勿急躁,否则连错一根线就会导致错误并且还不容易找出来费时又费力。

同时,在电路设计过程当中,电路的整体性分析是至关重要的。