直流电机PWM控制的FPGA实现.docx

《直流电机PWM控制的FPGA实现.docx》由会员分享,可在线阅读,更多相关《直流电机PWM控制的FPGA实现.docx(22页珍藏版)》请在冰豆网上搜索。

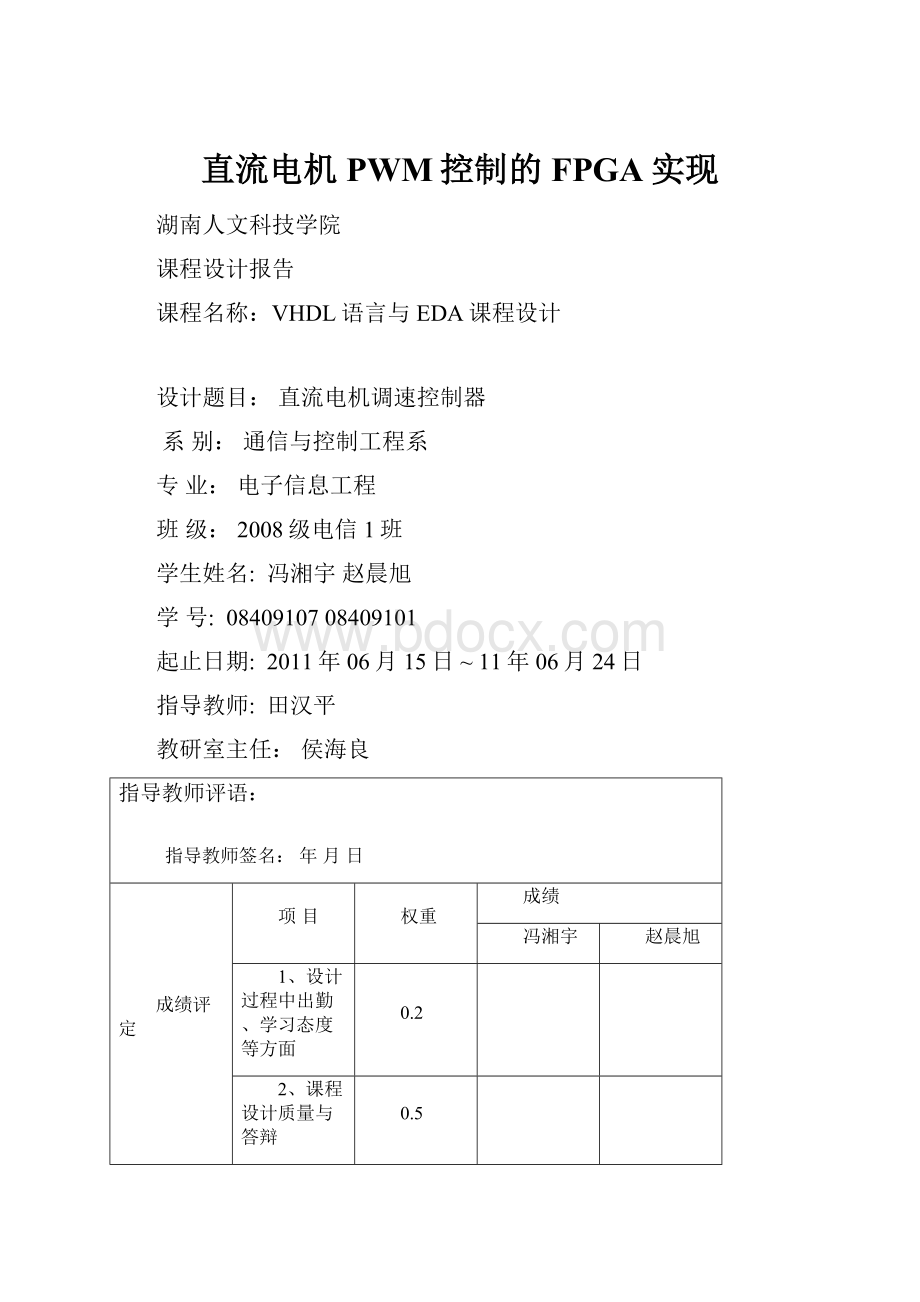

直流电机PWM控制的FPGA实现

湖南人文科技学院

课程设计报告

课程名称:

VHDL语言与EDA课程设计

设计题目:

直流电机调速控制器

系别:

通信与控制工程系

专业:

电子信息工程

班级:

2008级电信1班

学生姓名:

冯湘宇赵晨旭

学号:

0840910708409101

起止日期:

2011年06月15日~11年06月24日

指导教师:

田汉平

教研室主任:

侯海良

指导教师评语:

指导教师签名:

年月日

成绩评定

项目

权重

成绩

冯湘宇

赵晨旭

1、设计过程中出勤、学习态度等方面

0.2

2、课程设计质量与答辩

0.5

3、设计报告书写及图纸规范程度

0.3

总成绩

教研室审核意见:

教研室主任签字:

年月日

教学系审核意见:

主任签字:

年月日

摘要

文章详细地介绍了直流电机的类型、结构、工作原理、PWM调速原理以及FPGA集成芯片。

并对直流电机PWM调速系统方案的组成、硬件电路设计、程序设计及系统仿真分别进行了详细的叙述。

拟开发的直流电机PWM调速装置具有调速范围宽、低功耗、可实现在线调试等特点。

本系统是以FPGA为其控制核心,输入电路以键盘作为输入方式向FPGA控制系统发出控制命令,以有源晶振构成的时钟电路发出信号。

控制系统接收命令后直接向H型桥式驱动电路发出PWM控制信号。

输出电路主要实现正反转、起停控制、速度在线可调功能。

本设计已通过了实验仿真。

关键词:

直流电机;PWM;FPGA;有源晶振

设计要求1

1、方案论证与对比1

1.1方案一1

1.2方案二2

2、设计原理及其实现过程3

2.1设计总原理3

2.2设计总原理图5

2.3模块设计和相应模块程序5

2.3.1PWM脉冲调制信号电路模块5

2.3.2二进制计数器电路模块7

2.3.3数字比较器模块7

2.3.4细分计数器电路模块8

2.3.5逻辑控制模块9

2.4电路的总仿真图11

2.4.1正/反转控制仿真11

2.4.2启/停控制仿真11

2.4.3加/减速仿真12

2.4.4仿真结果分析13

3、课程设计结论及心得体会13

4、仪器仪表清单14

5、参考文献15

6、致谢15

附录电路完整程序程序15

直流电机调速控制器设计

设计要求

设计一个直流电机PWM调速控制器,并能进行正反转控制;

1、方案论证与对比

1.1方案一

基于单片机的直流电机PWM调速方案

图1基于单片机控制的PWM调速系统

如图1所示为基于单片机的直流电机PWM调速方案的系统方框图。

D/A转换器接在单片机AT89C51的P0引脚上,由软件编程的产生的信号从P0脚输出经D/A转换器后输出周期性线性增加的锯齿波电压,同时在模拟比较器另一端接给定的参考电压。

当锯齿波电压小于参考电压时输出低电平,当锯齿波电压大于参考电压时输出高电平。

改变滑动电阻的值便可以改变参考电压的大小,从而改变PWM波形中高电平的宽度,改变直流电机的占空比,改变直流电机的速度。

关于电机运动方向控制,本设计在单片机的P2口引出两个端口P2.1、P2.2控制直流的方向。

其控制的原理是在PWM波形输出端加上两个与门,其分别与电机的方向控制端P2.1、P2.2相与,其具体的连接如图2.5。

当P2.1、P2.2输出02H控制模型(P2.1=1,P2.2=0)时,三极管V1和V4导通,V2和V3截止,电机全速正转。

当P2.1、P2.2输出01H模型(P2.1=0,P2.2=1)时,V1和V4截止,V2和V3导通,电机全速反转。

在这里需要注意的问题的是,当输出全为1时,电机刹车,全为0时,电机滑行。

工作状态表如下:

表1电机工作状态真值表

P2.1

P2.2

状态

V1

V2

V3

V4

1

0

正转

1

0

0

1

0

1

反转

0

1

1

0

1

1

刹车

1

1

1

1

0

0

滑行

0

0

0

0

从以上的分析可知基于单片机的直流电机PWM调速方案要用到D/A转换器、模拟比较器,外围电路比较复杂。

1.2方案二

基于FPGA的直流电机调速方案

图2基于FPGA的直流电机调速系统

如图2.所示为基于FPGA的直流电机调速方案的方框图,FPGA中的数字PWM控制基于单片机PWM控制不同,用FPGA产生PWM波形,只需要FPGA内部资源就可以实现,如数字比较器、锯齿波发生器等均为FPGA内部资源,我们只要直接调用就可以。

外部端口U_D、EN1、Z/F、START接在键盘电路上,CLK2和CLK0接在外部时钟电路上,所用到的时钟频率为100MHz和50MHz,其具体的连接方式如图3。

其工作原理是:

设定值计数器的设置PWM的占空比。

当U/D=1时,输入CLK2,使设定值计数器的输出值增加,PWM的占空比增加,电机转速加快;当U/D=0时,输入CLK2,使设定值计数器的输出值减小,PWM的占空比减小,电机转速变慢。

在CLK0的作用下,锯齿波计数器输出周期性线性增加的锯齿波。

当计数值小于设定值时,数字比较器输出高电平;当计数值大于设定值时,数字比较器输出低电平,由此产生周期性的PWM波形。

旋转方向控制电路控制直流电动机转向和启/停,该电路由两个2选1的多路选择器组成,Z/F键控制选择PWM波形是从正端Z进入H桥,还是从负端F进入H桥,以控制电机的旋转方向。

当Z/F=1时,PWM输出波形从正端Z进入H桥,电机正转。

当Z/F=0时,PWM输出波形从负端F进入H桥,电机反转。

Start键通过“与”门控制PWM输出,实现对电机的工作停止/控制。

当START=1时,与门打开,允许电机工作。

当START=0时,与门关闭,电机停止转动。

H桥电路由大功率晶体管组成,PWM输出波形通过方向控制电路送到H桥,经功率放大以后对直流电机实现四象限运行。

并由EN1信号控制是否允许变速[4]。

与基于单片机的直流电机PWM调速方案相比,基于FPGA的直流电机PWM控制省去了外接的D/A转换器和模拟比较器,FPGA外部连线很少,电路更加简单,便于控制。

兼于FPGA的直流电机PWM控制具有精度高,反应快,外部连线少,电路简单,便于控制等优点,因此本设计采用基于FPGA的直流电机PWM控制方案[2]。

2、设计原理及其实现过程

2.1设计总原理

如图3所示,基于FPGA的直流电机PWM控制电路主要由四部分组成:

控制命令输入模块、控制命令处理模块、控制命令输出模块、电源模块。

键盘电路、时钟电路是系统的控制命令输入模块,向FPGA芯片发送命令,FPGA芯片是系统控制命令的处理模块,负责接收、处理输入命令并向控制命令输出模块发出PWM信号,是系统的控制核心。

控制命令输出模块由H型桥式直流电机驱动电路组成,它负责接收由FPGA芯片发出的PWM信号,从而控制直流电机的正反转、加速以及在线调速。

电源模块负责给整个电路供电,保证电路能够正常的运行。

图3FPGA直流电机PWM控制电路

在图3中所示的FPGA是根据设计要求设计好的一个芯片,其内部逻辑电路如图4。

START是电机的开启端,U_D控制电机加速与减速,EN1用于设定电机转速的初值,Z_F是电机的方向端口,选择电机运行的方向。

CLK2和CLK0是外部时钟端,其主要作用是向FPGA控制系统提供时钟脉冲,控制电机进行运转。

通过键盘设置PWM信号的占空比。

当U_D=1时,表明键U_D按下,输入CLK2使电机转速加快;当U/D=0,表明键U_D松开,输入CLK2使电机转速变慢,这样就可以实现电机的加速与减速。

Z_F键是电机运转的方向按键,当把Z_F键按下时,Z_F=1,电机正转;反之Z/F=0时,电机反转。

START是电机的开启键,当START=1,允许电机工作;当START=0时,电机停止转动。

H桥电路由大功率晶体管组成,PWM输出波形通过由两个二选一电路组成的方向控制电路送到H桥,经功率放大以后对直流电机实现四象限运行。

并由EN1信号控制是否允许变速[5]。

2.2设计总原理图

图5总电路设计图

2.3模块设计和相应模块程序

2.3.1PWM脉冲调制信号电路模块

PWM脉宽调制信号产生电路由可控的加减计数器CNTA、5位二进制计数器CNTB、数字比较器LPM_COMPARE三部分组成。

可控的加减计数器做细分计数器,确定脉冲宽度。

当U/D=1时,输入CLK2,使设定值计数器的输出值增加,PWM的占空比增加,电机转速加快;当U/D=0,输入CLK2,使设定值计数器的输出值减小,PWM的占空比减小,电机转速变慢。

5位二进制计数器在CLK0的作用下,锯齿波计数器输出周期性线性增加的锯齿波。

当计数值小于设定值时,数字比较器输出高电平;当计数值大于设定值时,数字比较器输出低电平,由此产生周期性的PWM波形。

其内部逻辑图如图6所示。

图6FPGA中的PWM脉宽调制信号产生电路

可控的加减计数器CNTA中的端口U_D控制计数器的方向,EN1是计数器的使能端,控制计数器初值的变化。

U_D=1时,加减计数器CNTA在脉冲CLK2的作用下,每来一个脉冲,计数器CNTA加1,U_D=0时,每来一个脉冲,计数器CNTA减1。

使能端EN1设定计数器值的初值,当EN1由1变为0的时候,无论U_D如何表化,计数器的值都不会发生变化,这样就完成了计数器的设定值,其仿真波形如图7所示。

图7细分计数器的仿真波形

2.3.2二进制计数器电路模块

CNTB是一个简单的5位二进制计数器,它的工作原理和CNTA的原理很相似,我们只是在CNTA的时钟端加了一个使能端EN1控制其加减的方向。

而CNTB的时钟端没有加使能端,所以每来一个脉冲计数器加1,因为CNTB是一个5位的二进值计数器,所以当计数器的值当大于32时,计数器又重新从0开始记数,从而产生周期性的线性增加的锯齿波。

其仿真波形如图8。

图85位二进制计数器仿真波形

2.3.3数字比较器模块

数字比较器是产生PWM波形的核心组成部件,可控的加减计数器CNTA和5位二进制计数器CNTB同时加数字比较器LPM-COMPARE两端作为两路输入信号,当计数器CNTB输出值小于细分计数器CNTA输出的规定值时,比较器输出高电平;当CNTB输出值大于细分计数器CNTA输出的规定值时,比较器输出低电平。

改变细分计数器的设定值,就可以改变PWM输出信号的占空比。

为了便于观察防真波形,我在CNTB的输出加上B[4..0],仿真波形如图9。

图9数字比较器的仿真波形

2.3.4细分计数器电路模块

细分计数器CNTA是一个双向计数器,可以进行加减计数,由U_D控制其加/减计数方向,CLK是计数时钟输入端。

为了便于连续变速控制,在计数器的CLK端通过“与”门,加入了CLK2外部变速控制附加时钟,并由EN1信号控制是否允许变速。

在本次设计中直流电机转速进行了32级细分。

其仿真波形如图4.6,细分计数器的初值我设为08H,也就是十进值的8,当计数器CNTB的值小于8时,AGB输出高电平,当计数器CNTB的值大于8时,AGB的输出值为低电平,从而产生PWM波形。

图10A[4..0]=08H时电机加速PWM波形

通过改变细分计数器的值就可以改变PWM的占空比,从而改变直流电机的速度。

在图11中占空比D=8/32=0.25,在图4.7中占空比D=4/32=0.125。

通过以上两组数据比较以及分析仿真波形我们可以看出,只要改变使能端电平的高低,便可以改变细分计数器的值,也就是改变细分计数器CNTA的初值,从而可以改变直流电机的占空比,改变直流电机的速度。

图11A[4..0]=04H时电机减速PWM波形

调节PWM波的占空比是电机调速的重要手段,若脉宽计数器CNTA的值逐渐增大,输出脉冲的开启时间变大,PWM占空比逐渐变大,功率器件输出给电机电枢的能量增加,电机加速。

若脉宽计数器定时器CNTA的值减小,输出脉冲的开启时间变小,PWM占空比逐渐变小,功率器件输出给电机电枢的能量减少,电机减速。

当电机得到加速信号,占空比增大至它可调范围的最大值后保持,电机得到减速信号,占空比减小至它的可调范围的最小值后保持。

2.3.5逻辑控制模块

如图12所示FPGA中的工作/停止控制和正/反转方向控制电路,其两个二选一多路选择器加上两个与门根据逻辑原理组合而成。

START键通过“与”门控制PWM输出,实现对电机的工作/停止控制。

当START端接高电平时,表示电源接通,电机开始运转;当START端接低电平时,电机停止运转。

Z/F键控制选择PWM波形是从正端Z进入H桥,还是从负端F进入H桥,以控制电机的旋转方向。

当Z/F=1时PWM输出波形从正端Z进入H桥,电机正转。

当Z/F=0时PWM输出波形从负端F进入H桥,电机反转。

仿真如图13所示。

图12FPGA中的工作/停止控制和正/反转方向控制电路

图13正/反转工作控制电路波形

当START=1时,与门打开,允许电机工作。

当START=0时,与门关闭,电机停止转动。

仿真如图14所示。

图14 工作/停止电路波形

2.4电路的总仿真图

2.4.1正/反转控制仿真

键盘Z_F是电机的方向控制键。

当要求电机正转时,只需要按下键Z_F,表示Z_F输出高电平,即Z_F=1,电机正转,如图17所示。

当键Z_F松开时,Z_F=0时,电机反转,如图15、图16所示。

图17电机正转

图15电机反转

图16电机正反转

2.4.2启/停控制仿真

START键是电机的启动键,当按下START键时,START=1,电机进入运行状态,如图18所示。

反之,START=0时,电机停止,如图19、图20所示。

图18启动仿真波形

图19停止仿真波形

图20启/停仿真波形

2.4.3加/减速仿真

键盘EN1控制电机是否允许变速。

所以通过改变EN1便可以改变设定值H[4..0]的值,也就是设定值的初值,从而改变了直流电机的占空比,改变直流电机的速度,达到调速的目的。

因为CNTB是5位的计数器,所在本设计中直流电机转速细分为32级。

如图21的占空比为2/32=0.0625,同理通过按键EN1该变H[4..0]的值便得到如图22、23的PWM仿真波形,其占空比依次为0.125、0.25,也就是占空比增大,电机的速度增加。

根据以上的数据比较与仿真波形的分析可以看出,电机的速度在逐渐的增加。

所以通过改变EN1的值可以改变直流电机的PWM占空比,从而改变直流电机的速度。

图21H[4..0]=02H仿真波形

图22H[4..0]=04H仿真波形

图23H[4..0]=08H仿真波形

2.4.4仿真结果分析

通过2.5.1到2.5.3的仿真波形分析可知,本设计中的各项功能够很好的实现。

在时钟脉冲的作用下,计数器CNTA和CNTB都能按照事先设定好的规则进行计数。

CNTA是可控的加减计数器,U_D控制其计数的方向,EN1用于设定其初值,当NE1由高电平变为低电平时,就完成了设定值。

CNTB是5位二进制计数器,其在时钟脉冲CLK0的作用下一直加数,当它加到32时就自动返回到0再重新加数。

两路计数器同时加到数字比较器LMP_COMPARE上,当CNTB的值小于设定值时,数字比较器输出高电平,当CNTB的值大于设定值时,数字比较器输出低电平。

因此改变设定值的大小就可以改变PWM波形的大小,也就是完成了电机的调速。

Z_F是电机的方向按键,选择PWM波形的进入方向,当其为1时,电机正转,反之,反转。

至于电机的控制,是在它的输入端加上两个与门来控制电机的启动与停止。

其具体的操作如下:

当按下键Z_F键时,电机正转,松开键时,电机反转。

当按下键START时,电机开始工作,松开时,电机停止工作。

通过按键EN1的闭合与断开可以改变H[4.0]的值从而改变直流电机的PWM占空比,达到改变直流电机速度的目的。

本设计采用VHDL设计FPGA脉宽调制控制方案,计算机仿真和对直流电机控制的结果表明,该电路能有效地产生PWM控制信号控制电机的转速,控制精度由FPGA中的数字比较器决定。

在本设计中,采用的数字比较器为5位,若增加数字比较器的位数,就可以提高电机转速的控制精度。

电路中省去了D/A转换器使电路变得更加简洁,同时也降低控制器的成本。

FPGA内部采用状态机结构,遇到干扰时,能很快从异常状态转入正常工作状态,保证了控制系统具有高的可靠性。

从以上的仿真中可以看出,基于FPGA的直流电机的控制能够达到很好的预期效果。

3、课程设计结论及心得体会

本次EDA课程设计题目为直流电机调速器设计,实现用PWM对于电机的控制。

此次课设需要用硬件描述语言(VHDL)编写程序,并在QuartusII软件平台上进行程序的编译和仿真,锁定引脚并下载到可编程逻辑器件(试验箱)中,进行硬件的测试。

此次EDA课程设计历时两周时间,两人一组合作进行系统的设计。

程序的编写我们采用元件例化的形式,经过思考和相互间的分析讨论,将整个系统划分3个功能模块,彼此配合进行3个功能模块设计和程序的编写。

其间,我们亦遇到许多问题,诸如整个系统核心模块计数过程的实现,时钟频率的设定等等。

经历两周时间的不懈努力和队友之间愈加默契的配合,我们终于完成预定的目的。

虽然其中遇到很多困难,很多问题,但在我们两人相互支持和鼓励想下,都能够得以顺利的找到解决办法或者改进的方法,并在合作中相互提高,彼此进步,在困难在中体会到合作的乐趣。

EDA技术对于我们电子信息工程专业的学生来说是一本很重要的专业技术课程,EDA技术极大地提高了电路设计的效率和可操作性,减轻了设计者的劳动强度,是一门实际应用很广泛的技术。

现在对EDA的概念或范畴用得很宽。

包括在机械、电子、通信、航空航天、化工、矿产、生物、医学、军事等各个领域,都有EDA的应用。

目前EDA技术已在各大公司、企事业单位和科研教学部门广泛使用。

例如在飞机制造过程中,从设计、性能测试及特性分析直到飞行模拟,都可能涉及到EDA技术。

所以,EDA课程的学习对于我们自身素质和能力的提高有十分重要的积极作用,应该很认真的学习。

4、仪器仪表清单

器件

型号/参数

数量

SOPC/EDA开发系统

GW48

1套

微型计算机

联想

1台

QuartusⅡ软件

6.0

1套

表一仪器仪表清单

5、参考文献

[1]潘松著.EDA技术实用教程(第二版).北京:

科学出版社,2005.

[2]康华光主编.电子技术基础模拟部分.北京:

高教出版社,2006.

[3]阎石主编.数字电子技术基础.北京:

高教出版社,2003.

6、致谢

这次课程设计感谢指导老师田汉平的悉心教导,也感谢其他老师对我们的帮助,同时感谢课程设计带队的老师们。

特别提出的是在本课题方案的选择上,岳老师给予了我们很多建议,且在解决课程设计遇到的困难上,岳老师田老师给了我们很大的帮助。

同样感谢同学们的通力合作,成功不是属于一个人的,而是属于大家的。

附录电路完整程序程序

LIBRARYIEEE;

USEIEEE.STD_LOGIC_1164.ALL;

USEIEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITYCNTAIS

PORT(CLK:

INSTD_LOGIC;

U,T:

INSTD_LOGIC;

EN:

INSTD_LOGIC;

M:

OUTSTD_LOGIC;

CQ:

OUTSTD_LOGIC_VECTOR(4DOWNTO0));

ENDCNTA;

ARCHITECTUREBEHAVOFCNTAIS

SIGNALCQL:

STD_LOGIC_VECTOR(4DOWNTO0);

SIGNALU_TEM:

STD_LOGIC;

SIGNALT_TEM:

STD_LOGIC;

BEGIN

PROCESS(CLK)

BEGIN

IFCLK'EVENTANDCLK='1'THEN

U_TEM<=U;

T_TEM<=T;

IFEN='1'THEN

IFU_TEM='0'ANDU='1'THEN

IFCQL="11111"THEN

CQL<="11111";

ELSE

CQL<=CQL+1;

ENDIF;

ELSIFT_TEM='0'ANDT='1'THEN

IFCQL="00000"THEN

CQL<="00000";

ELSE

CQL<=CQL-1;

ENDIF;

ENDIF;

ELSIFEN='0'THEN

M<='1';

ENDIF;

ENDIF;

ENDPROCESS;

CQ<=CQL;

ENDBEHAV;

LIBRARYIEEE;

USEIEEE.STD_LOGIC_1164.ALL;

USEIEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITYCNTBIS

PORT(CLK0,M:

INSTD_LOGIC;

Q:

OUTSTD_LOGIC_VECTOR(4DOWNTO0));

ENDCNTB;

ARCHITECTUREBEHAV1OFCNTBIS

SIGNALQL:

STD_LOGIC_VECTOR(4DOWNTO0);

BEGIN

PROCESS(CLK0)

BEGIN

IFCLK0'EVENTANDCLK0='1'THEN

IFM='1'THEN

IFQL=33THEN

QL<="00000";

ELSE

QL<=QL+1;

ENDIF;

ENDIF;

ENDIF;

ENDPROCESS;

Q<=QL;

ENDBEHAV1;

LIBRARYIEEE;

USEIEEE.STD_LOGIC_1164.ALL;

ENTITYCOMPIS

PORT(datab,dataa:

INSTD_LOGIC_VECTOR(4DOWNTO0);

m:

INSTD_LOGIC;

agb:

OUTSTD_LOGIC);

ENDCOMP;

ARCHITECTUREBEHAV2OFCOMPIS

BEGIN

PROCESS(dataa,datab,m)

BEGIN

IFm='1'THEN

IFdataa>databTHEN

agb<='1';

ELSE

agb<='0';

ENDIF;

ELSEagb<='0';

ENDIF;

ENDPROCESS;

ENDBEHAV2;