简易DDS频率合成器设计.docx

《简易DDS频率合成器设计.docx》由会员分享,可在线阅读,更多相关《简易DDS频率合成器设计.docx(13页珍藏版)》请在冰豆网上搜索。

简易DDS频率合成器设计

第一章系统分析与设计方案

1.1DDS设计原理介绍

DDS即DirectDigitalSynthesizer数字频率合成器,是一种基于全数字技术,从相位概念出发直接合成所需波形的一种频率合成技术,是一种新型的数字频率合成技术。

具有相对带宽大、频率转换时间短、分辨力高、相位连续性好等优点,很容易实现频率、相位和幅度的数控调制,广泛应用于通讯领域。

1.2直接数字式频率合成器(DDS)的基本结构

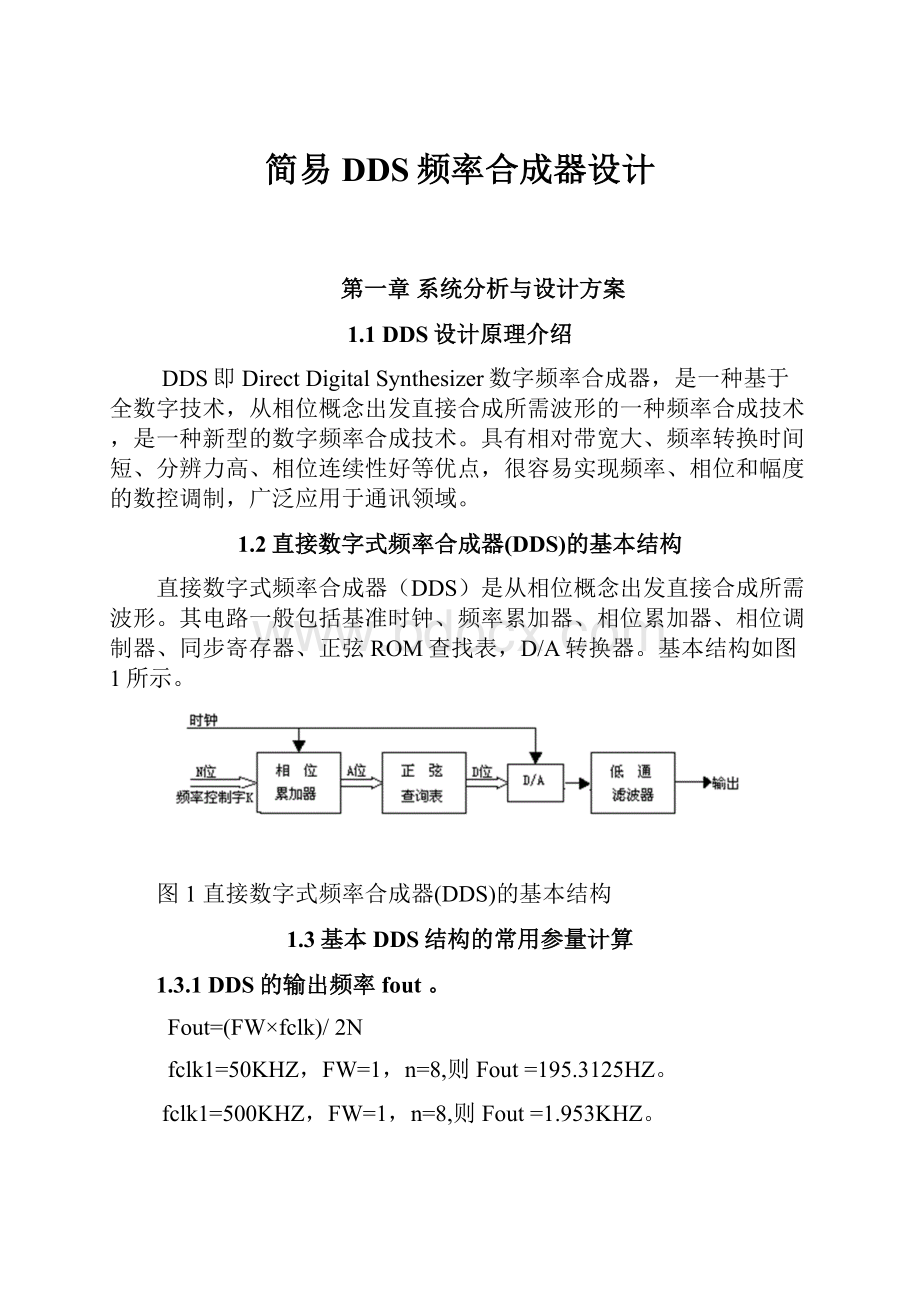

直接数字式频率合成器(DDS)是从相位概念出发直接合成所需波形。

其电路一般包括基准时钟、频率累加器、相位累加器、相位调制器、同步寄存器、正弦ROM查找表,D/A转换器。

基本结构如图1所示。

图1直接数字式频率合成器(DDS)的基本结构

1.3基本DDS结构的常用参量计算

1.3.1DDS的输出频率fout。

Fout=(FW×fclk)/2N

fclk1=50KHZ,FW=1,n=8,则Fout=195.3125HZ。

fclk1=500KHZ,FW=1,n=8,则Fout=1.953KHZ。

1.3.2DDS产生的相位。

(PW×2π)/2N

1.3.3DDS的频率分辨率。

Fout=fclk/2N

1.3.4DDS的频率输入字FW计算。

FW=2N×(fout/fclk)

1.4DDS的工作原理

1.4.1相位累加器与频率控制字FW

每来一个时钟脉冲fclk,N位加法器将频率控制字FW与累加寄存器输出的累加相位数据相加,把相加后的结果送至累加寄存器的输入端。

累加寄存器一方面将在上一时钟周期作用后所产生的新的相位数据反馈到加法器的输入端,使加法器在下一时钟的作用下继续与频率控制字FW相加;另一方面将该值作为存储器的地址输出相应的波形数据。

最终经D/A转换成所需要的模拟波形。

相位累加器在基准时钟的作用下,进行线性相位累加,当相位累加器加满量时就会产生一次溢出,这样就完成了一个周期,此周期即为DDS的频率周期。

DDS的输出信号频率:

Fout=(FW×fclk)/2N,通过设定相位累加器的位数和频率控制字可确定输出频率。

1.4.2相位控制字PW

每来一个时钟脉冲fclk,加法器将相位控制器PW与累加寄存器输出的数据相加,把相加后的结果作为波形存储器(ROM)的相位取样地址,这样就可以把存储在波形存储器内的波形取样值(二进制编码)经查找表查出,完成相位到幅值转换。

波形存储器的输出送到D/A转换器,将数字量转换成所要求合成频率的模拟量信号。

第二章软件设计

2.1VerilogHDL程序

2.1.18位加法器程序代码

moduleadder8(sum,a,b);

outputsum;

inputa,b;

wire[3:

0]a;

wire[3:

0]b;

wire[7:

0]sum;

assignsum=a+b;

endmodule

2.1.216位加法器程序代码

moduleadder16(sum,a,b);

outputsum;

inputa,b;

wire[7:

0]a;

wire[7:

0]b;

wire[15:

0]sum;

assignsum=a+b;

endmodule

2.1.38位寄存器程序代码

modulereg8(din,q,clk);

output[7:

0]q;

input[7:

0]din,input,clk;

reg[7:

0]q;

always@(posedgeclk)begin

q=din;

end

endmodule

2.1.416位寄存器程序代码

modulereg16(din,q,clk);

output[15:

0]q;

input[15:

0]din;

inputclk;

reg[15:

0]q;

always@(posedgeclk)begin

q=din;

end

endmodule

2.1.5dds代码程序

moduledds(clk0,fword,pword,fout,pout);

output[7:

0]fout,pout;

input[7:

0]fword,pword;

inputclk0;

wire[7:

0]lin8b,sin8b;

wire[15:

0]f16b,d16b,din16b;

assignf16b[15:

8]=fword;

assignf16b[7:

0]=8'b00000000;

adder16u1(.a(f16b),.b(d16b),.sum(din16b));

reg16u2(clk(clk0),.in(din16b),.qout(d16b));

romu3(d16b[15:

8],fout);

adder8u4(.a(pword),.b(d16b[15:

8]),.sum(lin8b));

reg8u5(.clk(clk0),.in(lin8b),.qout(sin8b));

romu6(sin8b,pout);

endmodule

2.1.6ROM的创建

首先选择ROM数据文件编辑窗,即在File菜单中选择“New”,并在New窗中选择“Otherfiles”项,并选“MemoryInitializationFile”,点击OK后产生ROM数据文件大小选择窗。

这里采用2点8位数据的情况,可选ROM的数据数Number为256,数据宽Wordsize取8位。

点击“OK”,将出现空的mif数据表格,表格中的数据为10进制表达方式,任一数据对应的地址为左列于顶行数之和)。

将波形数据填入此表中,完成后在File菜单中点击“Saveas”,保存此数据文件。

第三章实验仿真

3.1原理图

3.1.1ROM

ROM深度256,数据位8位如图2所示

图2ROM深度256,数据位8位

3.1.2八位加法器

图3八位加法器

3.1.3十六位加法器

图4十六位加法器

3.1.4八位寄存器

图5八位寄存器

3.1.5十六位寄存器

图6十六位寄存器

3.2仿真波形

adder8波形如图3所示

图7adder8波形

adder16波形如图4所示

图8adder16波形

reg8波形如如图5所示

图9reg8波形

reg16波形如图6所示

图10reg16波形

rom波形如如图7所示

图11rom波形

ddsf1p0波形如如图8所示

图12ddsf1p0波形

ddsf2p0波形如如图9所示

图13ddsf2p0波形

ddsf8p0波形如如图10所示

图14ddsf8p0波形

ddsf32p0波形如如图11所示

图15ddsf32p0波形

ddsf1p64波形如如图12所示

图12ddsf1p64波形

ddsf1p128波形如如图13所示

图13ddsf1p128波形

ddsf1p192波形如如图14所示

图14ddsf1p192波形

3.3D/A转换电路

图15DAC0830引脚图图16DAC0832的逻辑结构

3.3.1DAC0832结构及工作原理

DAC0832是8分辨率的D/A转换集成芯片。

这个DA芯片以其价格低廉、接口简单、转换控制容易等优点,在电子产品中得到广泛的应用。

D/A转换器由8位输入锁存器、8位DAC寄存器、8位D/A转换电路及转换控制电路构成。

引脚图及主要内部逻辑结构图15、16所示。

根据对DAC0832的数据锁存器和DAC寄存器的不同的控制方式,DAC0832有三种工作方式:

直通方式、单缓冲方式和双缓冲方式。

DAC0832是采用CMOS工艺制成的单片直流输出型8位数/模转换器。

如图4-82所示,它由倒T型R-2R电阻网络、模拟开关、运算放大器和参考电压VREF四大部分组成。

,输出的模拟量与输入的数字量成正比,这就实现了从数字量到模拟量的转换。

一个8位D/A转换器有8个输入端(其中每个输入端是8位二进制数的一位),有一个模拟输出端。

输入可有28=256个不同的二进制组态,输出为256个电压之一,即输出电压不是整个电压范围内任意值,而只能是256个可能值。

3.3.2D/A转换电路模块

ROM中存储数据,采用查表法输出的数字信号经过D/A转换器DAC0832和OP07转换和运放后产生0V到5V之间范围的电压范围。

3.4实验结果

实验数据如表1所示

FW

fout

PW

相位

fclk1=50KHz

1

195.3Hz

0

0rad

2

390.6Hz

4

781.2Hz

64

1.57rad

8

1.562KHz

fclk2=500KHz

1

1.953KHz

128

3.14rad

2

3,906KHz

4

7.812KHz

192

4.71rad

8

15.62KHz

表1实验结果表格

3.5调试过程

3.5.1对adder8、adder16、reg8、reg16的调试

对这4个部分的调整主要针对仿真波形的参数设定,加法器的endtime设定为20us,寄存器设定为10us。

且各个仿真波形的时钟要设定统一。

且这4个波形的输入变量都设置为10进制,结果便于观察,以上仿真图都验证了结果的正确性。

3.5.2.D/A转换电路的调试

其中接电源时用到了+12V、12V,所以对应管脚一定检查清楚,还有最后测输出电压时,DAC0832的数据端都置高时,Vout=5V,当只有最高位接地时Vout=2.5V。

3.5.3.输出波形的调试

在接开发板之前要做fword,pword,fout,pout的引脚锁定及器件选择。

然后做仿真波形,仿真波形无误后再将示波器的输入接上图电路板的输出。

观察示波器输出的正弦波形。

第四章心得体会

通过此次系统课程设计的学习,掌握了很多EDA课程内容与实际应用结合的知识。

这一点也是感触最深的一点,刚开始学习EDA,感觉非常摸不到学习的门路,即使认真听老师讲课了,仍然还是觉得这些新的知识非常难以理解,以前都没有接触过的;但是通过没星期这样长时间系统的实验,觉得知识不是简单的浮于课本上,对EDA课程的认识也变得越来越透明。

尤其是对Quartus软件的使用,比之前掌握的更加熟练。

软件使用过程中生成模块的不同方法,以及使用过程中该注意的方法都慢慢掌握。

同时在做的过程中发现自己很多的问题,尤其是小细节方面,试验过程中自己出现的问题比如有:

刚开始用软件的时候总是忘了先建一个工程,以至于自己的工程下很多文件也显得很凌乱,刚开始居然以为同一顶层文件下的不同模块是在不同的工程内,所以导致编译出错;在编写程序的时候字母的大小写没有注意,但错过一次之后就不会再犯这种错误了。

还有程序或原理图都弄好后要整体编译;再仿真波形的时候一定要使时钟保持一致,各参数也选择好。

第五章参考文献

1.蒋立平编著.《数字电路》.南京理工大学出版社

2.南京理工大学电子技术中心编.《EDA设计实验指导书》

3.付文红、花汉兵编著.《EDA技术与实验》.机械工业出版社

4.王毅评、张振荣编著.《VHDL编程与仿真》.北京人民邮电出版社

5.潘松、黄继业编著.《EDA技术实用教程》.北京科学出版社

6.邹彦编著.《EDA技术与数字系统设计》.北京电子工业出版社

7.谭会生、瞿遂春等编.《EDA技术综合应用实例与分析》.西安电子科技大学出版社