verilog四位BCD加法器实验报告.docx

《verilog四位BCD加法器实验报告.docx》由会员分享,可在线阅读,更多相关《verilog四位BCD加法器实验报告.docx(7页珍藏版)》请在冰豆网上搜索。

verilog四位BCD加法器实验报告

1.实验目的

1进一步熟悉modelsim仿真工具的使用方法。

2学会设计验证的方法和流程。

3编写一个4位BCD加法器,并且用modelsim对其仿真。

2.实验任务

进一步熟悉modelsim仿真基本流程。

并完成一个4位BCD加法器,用modelsim对其仿真。

3.实验内容及步骤

3.1实验内容

进一步熟悉modelsim仿真基本流程:

1建一个工作库②编译设计文件③运行仿真④调试结果

实验步骤:

1.启动modelsim。

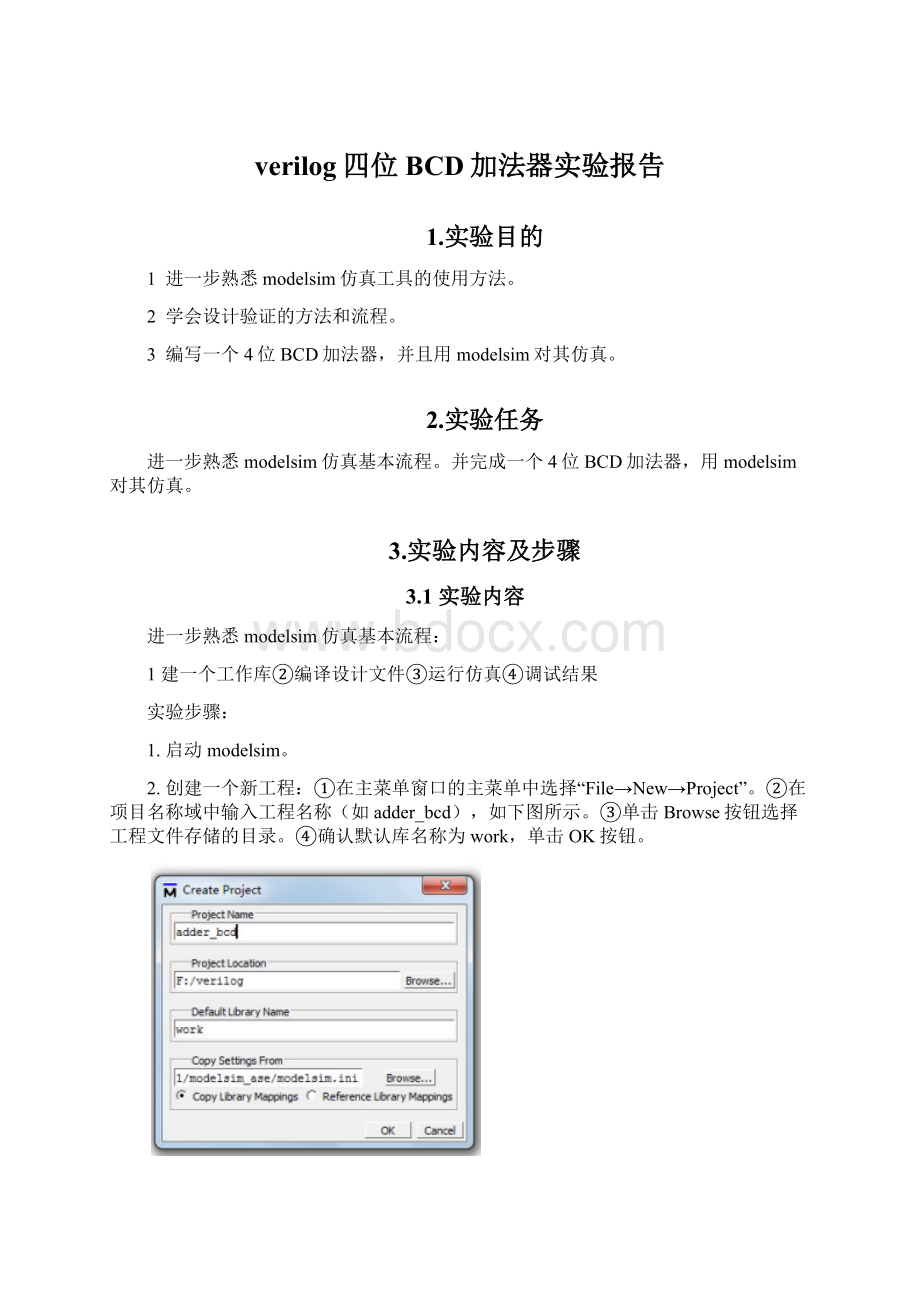

2.创建一个新工程:

①在主菜单窗口的主菜单中选择“File→New→Project”。

②在项目名称域中输入工程名称(如adder_bcd),如下图所示。

③单击Browse按钮选择工程文件存储的目录。

④确认默认库名称为work,单击OK按钮。

3.创建新设计的文件:

①单击OK按钮接受工程设置后,在主窗口的工作区将出现一个工程标签,同时弹出向工程添加项目的对话框。

单击“CreateNewFile”,在新弹出的窗口中,输入文件名(如adder_1bit),特别需要注意的是,“Addfileastype”里边要选择“verilog”类型。

②如果还需要写新的模块,在project对话框中点右键,选择“AddtoProject→NewFile”。

在弹出的对话框中输入新的文件名(如adder_bcd_1bit;adder_bcd_4bit;test),同样注意“Addfileastype”里边要选择“verilog”类型。

4.向工程输入有效的设计单元:

把设计的源文件输入到工程里边。

5.在主窗口中选择“Compile→CompileAll”完成工程的编译。

对于modelsim正确编译的设计文件,都打上“√”标志;对于编译失败的情况,打上“×”标志,此时可在右侧的脚本状态窗中查看出错信息,修正后再编译。

6.完成工程正确的编译后,在主窗口中单击Library标签,进入编译库页,打开work库,双击测试单元(如test),加载测试单元。

对mycount点右键,选择“Addtowave”。

然后就会出现Wave窗口,单击run就会运行并出现波形图。

7.仿真结束时,在主菜单中选择“Simulate→EndSimulate”,结束仿真。

3.2本次所实现的功能描述

4位BCD加法器,1位BCD用4位二进制数来表示,故4位BCD相加应为16位2进制数相加。

先写1位二进制加法器(adder_1bit),用与门实现。

然后写1位BCD加法器(adder_bcd_1bit),即4位二进制加法器,把1位二进制加法器实例化四次。

下来写4位BCD加法器(adder_bcd_4bit),把1位BCD加法器实例化四次。

最后写测试模块(test)。

完成了16位二进制数相加。

3.3本次实验的设计方案

moduleadder_1bit(a,b,cin,sum,cout);

inputa,b,cin;

outputsum,cout;

wires1,m1,m2,m3;

and(m1,a,b),(m2,b,cin),(m3,a,cin);

xor(s1,a,b),(sum,s1,cin);

or(cout,m1,m2,m3);

endmodule

moduleadder_bcd_1bit(a,b,cin,sum,cout);

input[3:

0]a,b;

inputcin;

output[3:

0]sum;

outputcout;

wirecin1,cin2,cin3;

wirecount;

wire[3:

0]sum1;

adder_1bitf0(.a(a[0]),.b(b[0]),.cin(cin),.sum(sum1[0]),.cout(cin1));

adder_1bitf1(.a(a[1]),.b(b[1]),.cin(cin1),.sum(sum1[1]),.cout(cin2));

adder_1bitf2(.a(a[2]),.b(b[2]),.cin(cin2),.sum(sum1[2]),.cout(cin3));

adder_1bitf3(.a(a[3]),.b(b[3]),.cin(cin3),.sum(sum1[3]),.cout(count));

assignsum=((sum1>4'b1001)|(count==1'b1))?

(sum1+4'd6):

sum1;

assigncout=((sum1>4'b1001)|(count==1'b1))?

1'b1:

1'b0;

endmodule

moduleadder_bcd_4bit(a,b,cin,sum,cout);

input[15:

0]a,b;

inputcin;

output[15:

0]sum;

outputcout;

wirecin1,cin2,cin3;

wire[15:

0]sum;

wirecout;

adder_bcd_1bitadder1(.a(a[3:

0]),.b(b[3:

0]),.cin(cin),.sum(sum[3:

0]),.cout(cin1));

adder_bcd_1bitadder2(.a(a[7:

4]),.b(b[7:

4]),.cin(cin1),.sum(sum[7:

4]),.cout(cin2));

adder_bcd_1bitadder3(.a(a[11:

8]),.b(b[11:

8]),.cin(cin2),.sum(sum[11:

8]),.cout(cin3));

adder_bcd_1bitadder4(.a(a[15:

12]),.b(b[15:

12]),.cin(cin3),.sum(sum[15:

12]),.cout(cout));

endmodule

moduletest;

reg[15:

0]a,b;

regcin;

wire[15:

0]sum;

wirecout;

adder_bcd_4bitmytest(.a(a),.b(b),.cin(cin),.sum(sum),.cout(cout));

always#21cin=~cin;

initialbegin

a=16'b0;

b=16'b0;

cin=1'b0;

#7a=16'b0000_0000_0000_0110;b=16'b0000_0000_0000_0101;

#7a=16'b0000_0000_1100_0010;b=16'b0000_0000_0000_0010;

#7a=16'b0000_1110_0000_0000;b=16'b0000_0110_0000_0000;

#7a=16'b1010_0000_0000_0000;b=16'b0101_0000_0000_0000;

#7a=16'b1001_0010_1100_0010;b=16'b0101_1010_0111_0101;

end

endmodule

3.4本次实验设计的结果

①在主窗口中单击Library标签,进入编译库页,打开work库,双击测试单元test.

2加载测试单元。

对mytest点右键,选择“Addtowave”。

3后就会出现Wave窗口,单击run就会运行并出现波形图。

4.实验总结

此次实验使我进一步熟悉了modelsim仿真工具的使用。

做了几个设计之后,现在也能熟练应用了,对moelsim有了基本的了解。

记得上次实验还不会写激励模块,但是这次实验已经能很轻松地写出来了。

真的学会之后才发现,激励模块要比建模模块好写多了。

难怪老师说激励模块很简单呢。

这次比上次的进步就是modelsim的使用更加熟练了,此外,上次出现的问题这次也没再出现了。

当然,这次实验也有新的问题出现。

其一,给同一个变量sum两次赋值,导致多驱动的发生。

其二,assign语句等式左边的变量和实例化里边的变量要定义为wire类型。

这是一个不该出现的问题,因为老师上课已经强调过了,我自己也做了笔记,可是还是出现这样的问题。

听了是一方面,真正会应用是另外一方面,所以以后一定要多动手,真正会使用才算把知识学到手。

其三,课前准备工作一定要做好,务必要把此次实验所要仿真的设计设计好。

实验课课堂上是让你使用modelsin编译仿真的,没有时间再去设计。

所以以后一定要注意,课前把设计写好。