日本人写的《晶体管电路设计》非常牛逼.docx

《日本人写的《晶体管电路设计》非常牛逼.docx》由会员分享,可在线阅读,更多相关《日本人写的《晶体管电路设计》非常牛逼.docx(23页珍藏版)》请在冰豆网上搜索。

日本人写的《晶体管电路设计》非常牛逼

8.1.1晶体管的开关

图8.1是一例发射极接地放大电路,这种电路能够通过输入信号(电压)连续地———模拟地控制流过集电极发射极间电流,获得输出电压。

但是开关电路,如图8.2所示是一种计数地接通/断开晶体管的集电极发射极间的电流作为开关使用的电路。

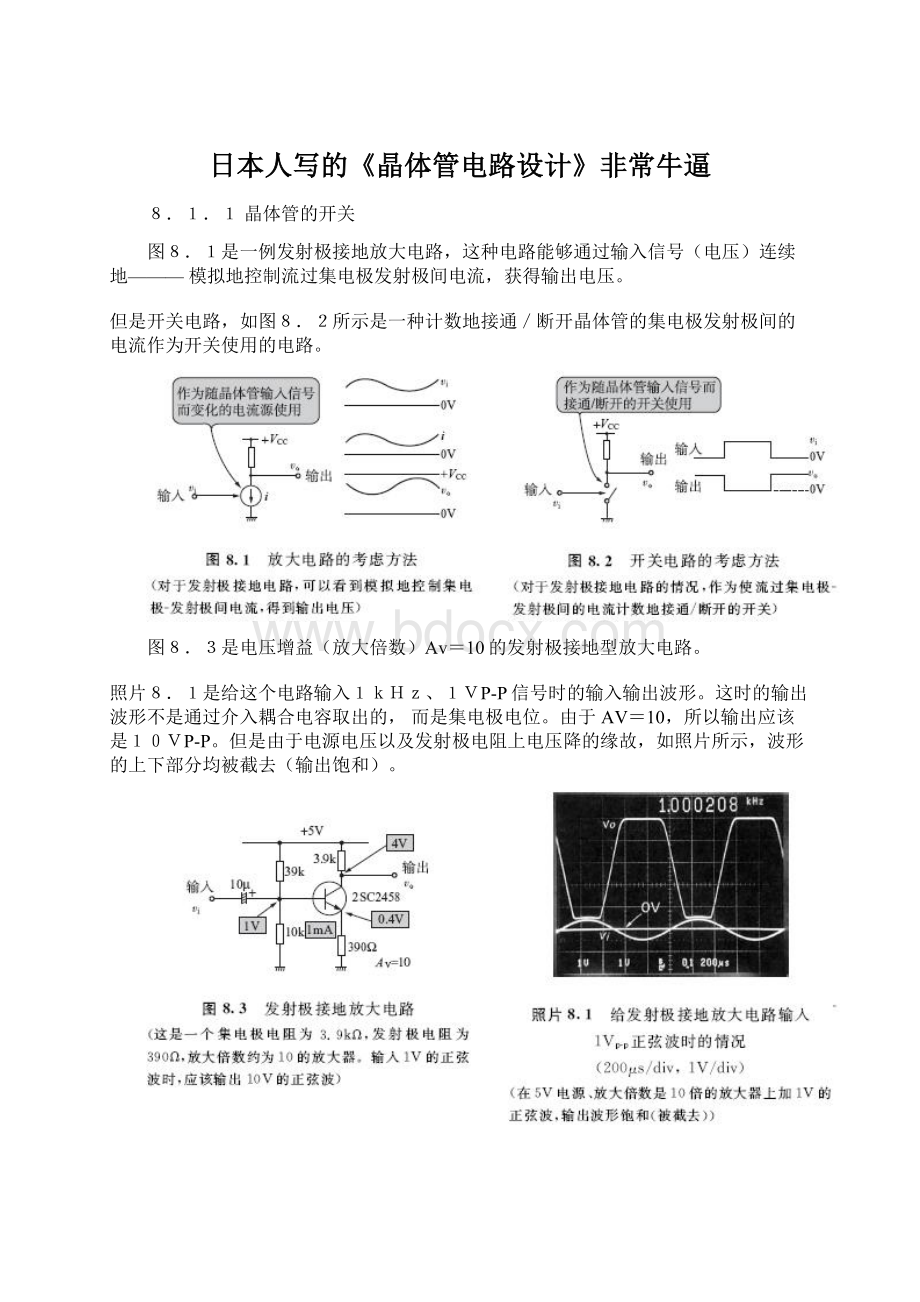

图8.3是电压增益(放大倍数)Av=10的发射极接地型放大电路。

照片8.1是给这个电路输入1kHz、1VP-P信号时的输入输出波形。

这时的输出波形不是通过介入耦合电容取出的,而是集电极电位。

由于AV=10,所以输出应该是10VP-P。

但是由于电源电压以及发射极电阻上电压降的缘故,如照片所示,波形的上下部分均被截去(输出饱和)。

输出波形的上半周被截去的情况是由于输出电平与电源电压相等,所以集电极电阻上没有了电压降,也就是说晶体管的集电极发射极间没有电流流过(集电极电流为零)。

换句话说,晶体管处于截止状态。

相反,输出波形的下半周被截去的情况是因为输出电平处于更接近GND电平的电位(集电极电阻上的电压降非常大),晶体管的集电极电流处于最大值。

也就是说,晶体管处于导通状态。

这样的开关电路只要利用输入信号使输出波形被限幅就可以实现(使晶体管处于接通/断开状态就可以),所以可以认为只要放大电路具有非常大的放大倍数,或者加上很大的输入信号就可以。

但是,这样的开关电路必须是直流的接通/断开状态(这样的用途非常多),所以必须具有一定的直流的放大倍数。

8.1.2从放大电路到开关电路图

8.4是从发射极放大电路演变到开关电路的示意图 。

首先为了获得直流增益(放大倍数),从图8.4(a)的一般发射极放大电路中去掉输入输出的耦合电容C1、C2,得到图8.4(b)的电路。

进一步为了提高放大倍数,去掉发射极电阻E,变成图8.4(c)的电路。

这样一来,也就没有必要加基极偏置电压。

当输入信号为0V时,晶体管处于截止状态 ,所以集电极就没有必要流过无用的电流———空载电流。

因此,如图8.4(d)所示去掉偏置用的R1。

为了确保没有输入信号时晶体管处于截止状态,需要保留使基极处于GND电位的电阻R2。

但是,图8.4(d)的电路中如果输入信号超过+0.6V,晶体管基极发射极间的二极管将处于导通状态,就开始有基极电流流过。

也就是说,这样的状态不能限制电流,会有非常大的基极电流流过。

因此,如图8.4(e)所示还需要插入限制基极电流的电阻R3。

这样就可以将发射极接地放大电路变形成开关电路。

8.1.3观测开关波形

图8.5是上述电路代入了具体数值的实际开关电路,照片8.2是给这个电路输入1kHz、2VP-P的正弦波时的输入输出波形。

输入信号是正弦波。

但是由于电路的放大倍数足够大,所以输出波形变成了方波。

当输入信号电平在+0.6V以下时体管处于截止状态,输出电平是+5V(电源电压)。

当超过+0.6V时,晶体管处于导通状态,输出基本上是GND电平。

通常开关电路的输入信号只是控制开关的接通/断开,所以采用与接通/断开电平相对于的二值信号,即方波。

经常用TTL或CMOS等数字电路的输出直接控制开关电路。

照片8.3是给图8.5的电路输入1kHz、0V/+5V方波时的输入输出波形。

由于用0V/+5V的方波使晶体管于接通/断开状态,所以输出波形也是+5V/0V的方波。

这个电路可以认为是发射极接地放大电路的变形,所以与放大电路一样,输入输出信号的相位是反转的。

从照片8.3看到的输入输出波形简直就是数字电路中倒相器(NOT电路)的输入输出波形。

所以这个电路可以作为倒相器使用。

但是,

为了能够像数字IC那样高速动作还需要作一些改进。

这将在后面介绍。

如果电源设置为+15V,由于输入信号是0V/+5V的CMOS(TTL)电平,所以可以作为向0V/+15V的CMOS电平变换的逻辑电平变换电路。

当然反过来也可以由0V/+15V变换为

0V/+5V。

8.1.4如果集电极开路

图8.5的电路中集电极连接着负载电阻L。

如图8.6所示,当不连接负载电阻时这个电路的集电极就原封不动地变成输出端。

把这个电路叫做开路集电极,它广泛应用于以继电器或灯泡等为外部负载的开关电路。

如图8.6所示,在使用NPN晶体管的电路中,如果在电位高于GND的电源与集电极(输出端)之间连接负载,这时就像是吸入负载电流。

在使用PNP晶体管的电路中,如果在比正电源电位低的电源(在图8.6(b)中是GND)与集电极间连接负载,这 时就像负载电流在流出。

因此,这个开路集电极能够接通/断开负载电流而与负载连接几伏的电源没有关系,所以是一个对于开关外部负载非常方便的电路。

8.2发射极接地型开关电路的设计

上面图8.5所示电路的设计指标如下。

输入采用0V/+5V的4000B系列CMOS逻辑电路的信号,接通/断开5mA的负载电流(+5V电源上连接RL=1kΩ)。

8.2.1开关晶体管的选择

由于负载电流(集电极电流)的指标是5mA,所以晶体管集电极电流IC的最大额定值必须大于5mA。

当晶体管处于截止状态时,连接负的电源的电压(这里是+5V)加在集电极发射极之间和集电极基极之间。

因此应选择集电极发射极间和集电极基极间电压最大额定值VCEO、VCBO大于连接负载的电源电压的晶体管。

这里按照VCEO>+5V,VCBO>+5V,C>5mA的条件,选择2SC2458(东芝)。

表8.1是2SC2458器件的特性。

顺便指出,使用PNP晶体管时的电路就变成图8.7那样。

当然使用时并不介意选择NPN晶体管还是PNP晶体管。

图8.5的电路已经在集电极与+5V电源间连接了负载(RL=1kΩ),所以是根据这个电源电压和负载电流来决定晶体管的。

在开路集电极的场合选择的方法也完全相同。

由外部负载连接的电源电压和从输出端(集电极)吸入或流出的最大负载电流共同选择晶体管。

8.2.2当需要大的负载电流时

发射极接地型开关电路的负载电流就是集电极电流,所以必须能够从输入端提供大于1/hFE的基极电流。

对于图8.5的电路由于负载电流小,只有5mA,所以没有什么问题。

但是当负载电流达数百毫安以上时驱动基极的电路(接续输入端的电路)就有可能无法提供足够的基极电流。

在这种情况下,需要采用称为“超

晶体管”的hFE非常大的晶体管(例如2SC3113(东芝)的hFE可达到600~3600),或者如图8.8所示将两个晶体管达林顿连接。

如图8.8所示,采用达林顿连接时Tr1的发射极电流全部变成Tr2的基极电流,所以总的hFE是各自晶体管的hFE之积(hFE1·hFE2)。

例如,如果hFE1=hFE2=100,那么总的hFE就是10000,用1mA的基极电流就能够开关10A的集电极电流。

但是在计算达林顿连接电路的基极电流时需要注意的是,当晶体管导通时基极发射极之间的电压降是1.2~1.4V(两个VBE)。

图8.9是一例采用达林顿连接的开关电路,是一个电灯开关电路。

由于晶体管是达林顿连接,所以可以用0.5mA的基极电流开关0.9A的负载。

在设计大负载电流的电路时,还需要注意晶体管的集电极发射极间饱和电压VCE(sat)。

尽管晶体管处于导通状态时的集电极发射极间电阻值非常小,但还不是零,所以当集电极电流流过时会产生电压降。

这就是集电极饱和电压VCE(sat)sat是saturation的简写)。

图8.10是2SC2458的集电极流过100mA的负载电流时的开关电路。

照片8.4是给这个电路输入1kHz,0V/+5V控制信号时的集电极波形

。

这个电路中,VCE(sat)=0.16V。

晶体管处于导通状态时的功率损耗是VCE(sat)与集电极电流之积,它们全部变成热损耗。

所以当负载电流大时,必须注意晶体管的发热问题。

另外如图8.9所示,当发射极接地型开关电路中采用达林顿连接时,Tr2的集电极发射极间电压并不是VCE(sat)而是Tr2的VBE(=0.6~0.7V)。

这是因为Tr2的集电极电位如果不是与Tr1的发射极电位(=Tr2的基极电位)同电位,那么Tr1的基极集电极间的PN结将处于导通状态。

因此,采用达林顿连接处理大电流时,特别要注意晶体管的热损耗问题(0.6~0.7V×集电极电流=热损耗)。

8.2.3确定偏置电路R1、R2

如果能使基极电流达到集电极电流的1/hFE倍,晶体管将处于导通状态。

考虑到hFE的分散性或者基极电流受温度影响而变化等因素(因为VBE具有温度特性,所以基极电流也随温度变化),应该使流过的基极电流稍大些。

这叫做过驱动,通常设定为按所使用晶体管hFE的最低值计算得到的基极电流的1.5~2倍以上。

由表8.1得知2SC2458的hFE最低值是70,图8.5中电路的负载电流为5mA,所以可以设定流过的基极电流大于0.1mA((5mA/70)×1.5)~0.14mA((5mA/70)×2)。

如图8.11所示,由于基极电位是+0.6V,所以输入信号为+5V时R1上产生的电压降为4.4V(但是要注意,达林顿连接时基极电位为+1.2V)。

按照上述条件,为使晶体管处于导通状态要求流过的基极电流为0.2mA,所以R1=22kΩ(=4.4V/0.2mA)(但是忽略了流过R2的电流)。

R2是输入端开路时确保晶体管处于截止状态的电阻。

如果R2过大,将容易受噪声的干扰,过小则在晶体管处于导通状态时会有无用电流流过R2。

这里设定R2=22kΩ(与R1值相同)。

最近,已经有些厂家产生出如图8.12所示那样内藏有偏置电阻的晶体管产品。

R1、R2电阻也有各种取值。

如果使用内藏电阻的晶体管将会减少电路的元件数目,这对于开关电路是很方便的。

8.2.4开关速度慢———s量级

照片8.5是给图8.5的电路输入100kHz、0V/+5V方波时的输入输出波形。

当输入信号

从0变化到+5V时,晶体管立即由截止状态变化到导通状态,输出信号

也立即响应,从+5V变化到0V。

但是,当

从+5V变化到0V时,晶体管从导通状态变化到截止状态时却花费时间,

从V变化到+5V时间滞后了

。

晶体管处于导通状态时有基极电流流过,所以在基区内积累有电子。

因此,在这种状态下即使输入信号变成了0V,基区中的电子并不能立即消失(电荷存储效应)。

而且在基极限流电阻R1的作用下,也不可能立即从基区取出全部电子,这就是造成时间滞后的原因。

在开关调节器之类使负载高速开关的应用电路中,这种时间滞后是很不利的。

8.3如何提高开关速度

使用晶体管开关时,上述图8.5电路的开关速度往往不能满足要求。

许多应用需要高的开关速度。

这里就提高速度的基本技术进行实验。

8.3.1使用加速电容

图8.13是给基极限流电阻R1并联小容量电容器的电路。

这样,当输入信号上升、下降时能够使R1电阻瞬间被旁路并提供基极电流,所以在晶体管由导通状态变化到截止状态时能够迅速从基区取出电子(因为R1被旁路),消除开关的时间滞后。

这个电容器的作用是提高开关速度,所以称为加速电容。

照片8.6是给图8.13的电路输入100kHz、0V/+5V方波时的输入输出波形。

可以看出由于加速电容的作用,已经看不到照片8.5中的时间滞后。

照片8.6中还看得不很清楚,实际上晶体管由截止状态到导通状态的时间也缩短了。

由于所使用的晶体管以及基极电流、集电极电流值等因素,加速电容的最佳值是各不相同的。

因此,加速电容的值要通过观测实际电路的开关波形决定。

对一般的晶体管来说,容量约为数十皮法至数百皮法。

8.3.2肖特基箍位

提高晶体管开关速度的另一个方法是利用肖特基二极管箍位。

这种方法是74LS、74ALS、74AS等典型的数字ICTTL的内部电路中所采用的技术。

图8.14是对图8.5的电路进行肖特基箍位的电路。

所谓肖特基箍位在基极集电极之间接入肖特基二极管。

这种二极管不是PN结,而是由金属与半导体接触形成具有整流作用的二极管,其特点是开关速度快,正向电压降VF比硅PN结小,准确地说叫做肖特基势垒二极管。

这里的肖特基二极管采用1SS286(日立)。

照片8.7是给图8.14的电路输入100kHz、0V/+5V方波时的输入输出波形。

可以看出其效果与接入加速电容(参见照片8.6)时相同,晶体管从导通状态变化到截止状态时没有看到时间滞后。

图8.15是图8.14的电路中晶体管处于导通状态(输出为0V)时的动作。

如图8.16所示,肖特基二极管的正向电压降VF比晶体管的VBE小(图8.14电路中的VF≈0.3V),所以本来应该流过晶体管的大部分基极电流现在通过D1被旁路掉了。

这时流过晶体管的基极电流非常小,所以可以认为这时晶体管的导通状态很接近截止状态。

因此,如照片8.7所示从导通状态变化到截止状态时的时间滞后非常小(基极电流小,所以电荷存储效应的影响小)。

照片8.7中,输出波形由0V变化到+5V时之所以波形上升沿不很陡,是由于R1与晶体管密勒效应构成低通滤波器的影响,与电荷存储效应没有关系。

8.3. 3如何提高输出波形的上升速度

照片8.8是图8.14所示的电路中R1=1kΩ时的开关波形(输入信号是100kHz、0V/+5V的方波)。

可以看出当R1小时由于低通滤波器的截止频率升高,所以输出波形从0V变化到+5V时的上升速度加快了。

加速电容是一种与减小R1值等效的提高开关速度的方法(减小R1值,也会加快输出波形的上升速度)。

肖特基箍位可以看作是改变晶体管的工作点,减小电荷存储效应影响,提高开关速度的方法。

由于肖特基箍位电路不像接入加速电容那样会降低电路的输入阻抗,所以当驱动开关电路的前级电路的驱动能力较低时,采用这种方法很有效。

在设计这种电路时需要注意肖特基二极管的反向电压V R的最大额定值。

肖特基二极管中某些器件的V R最大额定值非常低(高频电路中应用的某些器件仅为3V)。

图8.14的电路中因为晶体管截止时电源电压原封不动地加在D1上,所以必须使用V R的最大额定值大于5V的器件(1SS286是25V)。

8.4. 1给射极跟随器输入大振幅

射极跟随器是电压放大倍数为1的放大电路。

这种电路具有直流增益,利用输入大振幅的方波可以起到与开关电路相同的作用。

图8.17示出将射极跟随器演变为开关电路的过程。

首先,为了获得直流增益从图8.17(a)一般的射极跟随器中去掉输入输出耦合电容C1和C2,变成图8.17(b)所示的电路。

由于没有必要给基极加偏置电压(因为输入信号为0V时晶体管处于截止状态),所以如图8.17(c)所示再去掉R1。

但是,为了确保没有输入信号时晶体管处于截止状态,所以保留使基极处于GND电位的电阻R2。

这样就把射极跟随器变成了开关电路。

图8.18的电路是给图8.17(c)的电路赋予具体电路常数值的射极跟随器型开关电路。

照片8.9是给这个电路输入1kHz、4VP-P的正弦波时的输入输出波形。

当输入信号

的振幅在+0.6V以下时晶体管处于截止状态,所以只有i的正半周波形作为输出波形

出现。

而且

的振幅值总比

低0.6V(晶体管的VBE)。

照片8.10是给图8.18的电路输入1MHz、0V/+5V方波时的输入输出波形。

因为输出波形就是晶体管的发射极电位,所以它追随输入信号,输出的是0V/+4.4V的方波。

也就是说由于这个电路是射极跟随器的变形,所以输入输出信号的相位也与放大电路的情况相同,都是同相的。

8.4.2开关速度

8.3节曾经讲到如果发射极接地型开关电路中不采用加速电容等技术,就不能够提高开关速度。

但是,这里的射极跟随器型开关电路继承了射极跟随器频率特性好的优点。

如照片8.10所示,即使1MHz的频率也能够很容易地实现开关。

尽管图8.5和图8.18中使用的晶体管是相同的。

射极跟随器型开关电路的重要特点就是能够实现高速开关。

与发射极接地型开关电路相比,由于不需要限制基极电流的电阻(因为基极电流必须是负载电流的1/hFE),所以它的另一个优点就是元件少。

图8.18的电路是在发射极连接负载电阻RL。

不过也有不连接负载电阻的电路,如图8.19那样发射极原封不动地成了输出端。

与发射极接地型开关电路的开路集电极相对应,把这种电路叫做开路发射极电路。

它应用于高速开关外部负载的场合。

8.4.3设计开关电路的指标

图8.18的电路的设计指标如下。

这是应用0V/+5V的4000B系列CMOS逻辑电路的信号对5mA的负载电流进行接通/断开的电路。

8.4.4晶体管的选择

负载电流(发射极电流)的指标是5mA,所以晶体管的集电极电流(=发射极电流)的最大额定值必须大于5mA。

因为必须由4000B系列CMOSIC提供基极电流,所以为了将基极电流抑制在0.1mA(一般不怎么能够从4000B系列CMOSIC中取出电流

),而负载电流是5mA,所以hFE必须在50(=5mA/0.1mA)以上。

另外,晶体管处于截止状态时电源电压(在这里是+5V)是加在集电极发射极间和集电极基极间,所以所选择晶体管的集电极发射极间和集电极基极间的最大额定值VCEO、VCBO必须大于电源电压。

按照IC>5mA,hFE>50,VCEO>5V,VCBO>5V的条件,与发射极接地时情况相同选择2SC2458(东芝)。

当然使用

PNP晶体管也无妨,不过这时的电路变成图8.20所示的那样。

开路发射极的设计也完全相同,由加在外部负载上的电压以及从输出端(发射极)流出或者吸入的最大负载电流为根据选择晶体管。

射极跟随器型开关电路的负载电流原封不动地就是发射极电流,所以必须给输入端提供它的1/hFE的基极电流。

但是当负载电流大时,有可能无法提供驱动输入端电路所必要的基极电流。

在这种情况下,仍然和发射极接地时的办法一样,或者采用超

晶体管,或者如图8.21所示将晶体管达林顿连接使用。

但是,达林顿连接时需要注意发射极电位要比基极电位低1.2~1.4V(两个VBE)。

射极跟随器型开关电路中当晶体管处于导通状态时,发射极电位比基极电位低0.6~0.7V。

因此,即使基极电位与集电极电位(即电源电压)相等,晶体管的集电极发射极间电压VCE还是0.6~0.7V(达林顿连接时是1.2~1.4V)。

这个VCE与集电极电流=

发射极电流)之积就是晶体管的热损耗,所以当负载电流大时应该注意晶体管的发热问题。

8.4.5偏置电阻1的确定

R1是当输入端开路时为确保晶体管处于截止状态所使用的电阻。

当R1值大时容易受噪声的影响,反之,当R1值小时将有无用电流从输入端流入R1。

这里设定R1=10kΩ。

8.5.1继电器驱动电路

图8.22是用晶体管驱动继电器的电路。

继电器是磁性机械开关元件,是用逻辑信号开关各种信号时使用的元件。

照片8.11示出各种继电器。

由继电器的大小决定能够开关的信号的大小。

图8.22的电路就是把图8.5电路中的负载电阻置换为继电器的开关电路。

这个电路必须注意的是在继电器线圈上并联有二极管。

当开关的负载为电动机或者继电器等电感性负载时,在截断流过负载的电流时(晶体管进入截止状态时)会产生反电动势(楞茨定则)。

这时产生的电压非常大。

当这种电压超过晶体管的集电极基极间、集电极发射极间电压的最大额定值VCBO、VCEO时,晶体管将会被击穿。

因此实际上如图8.22所示,给负载(线圈)并联接续二极管(注意如果二极管的方向与图示方向相反,后果将很严重!

)。

这样一来,由于开关截止时产生的反电动势,当集电极的电位变为电源电压(图8.22中为+12V)+0.6V(二极管的正向电压降)时,二极管处于导通状态,使反电动势闭合(也可以认为集电极电位被箍位在电源电压+0.6V)。

也就是说,由于集电极的电位不高于电源电压+0.6V,所以能够防止晶体管被击穿。

这个晶体管叫做续流二极管或者闭合二极管。

照片8.12是图8.22的电路中没有接续流二极管时的集电极波形(控制信号是150Hz、0V/+5V的方波)。

继电器线圈产生的反电动势电压达到了140V!

大大超过2SC2458的最大额定值VCBO=VCEO=50V。

在这种状态下,开关晶体管难免会被击穿。

照片8.13是接续了续流二极管时(参见图8.22)的集电极波形,这个续流二极管采用硅二极管1SS176(最大反向电压是35,最大正向电流是300mA,东芝)。

可以看出由于续流二极管使反电动势闭合,所以没有产生高于电源电压的电压(照片中看不清楚,实际上继电器断开时的瞬间电压是电源电压+0.6V)。

8.5.2LED显示器动态驱动电路(发射极接地)

图8.23是7段LED发光二极管驱动电路。

这种7段LED在用数字显示数字电路的BCD输出时应用得很多,是一种很常见的电路。

照片8.14是一例7段LED。

在LED显示器的场合,如果位数(LED的器件数)多,那么将有很多静态电流流过LED,消耗许多功率。

因此经常采用一位一位依次点灯的动态点灯方式。

动态点灯时在某一位点灯期间其他各位都处于熄灯状态(通常只有一位处于点灯状态),所以能够降低功耗。

图8.23的电路是由上方采用PNP晶体管的开路集电极电路与下方采用NPN晶体管达林顿连接的开路集电极电路以及中间夹入的LED构成的电路。

上方是与段(器件)相对应的开关,下面是与数字(位)相对应的开关。

只有当上下两方都处于导通状态时LED才会有电流流过而发光。

下方的位开关中会流过7个段的电流,因此采用达林顿连接以保证能够吸收大电流。

图8.24是图8.23电路的控制信号的工作波形。

通过DG0~DG2数字信号依次为+5V,对位进行扫描。

这时,a~

的段信号控制输入信号电平(0V:

发光,+5V:

熄灯),使得发光的位显示为文字。

一个位发光的时间一般是几百微秒至几毫秒。

通常这种动态驱动电路的驱动(形成图8.24那样的周期)是利用微处理器进行。

如果是一般的LED(不是高辉度灯泡)静态发光,流过LED的电流有几毫安至几十毫安就足够了。

动态点灯时由于熄灯的时间较长,流过静态发光场合电流的2~3倍就能够获得足够的辉度。

图8.23的电路中,每段LED各流过30mA电流。

流过LED的电流由串联到各段的限流电阻R1~ R7决定。

首先,由于2SA1048置于导通状态时的饱和电压VCE(sat)非常小(0.1V以下),可以忽略不计。

所以,从电源电压减去7段LED的电压降2V(显示用LED 的正向电压降与流过的电流不怎么有关,为2V)以及达林顿连接的集电极发射极间电压0.6V值余下的就是加在R1~ R7上的电压。

为了使流过LED的电流为30mA,取R1~ R7=82Ω(=(5V-2V-0.6V)/30mA)。

图8.23的电路采用了7段LED有共同阴极的共阴极型LED。

如果是采用共阳极型LED,其电路如图8.25所示,段一侧的开关电路要与数字型开关电路调换。

8.5.3LED显示器动态驱动电路(射极跟随器)

图8.26与图8.23相同也是7段LED的动态驱动电路。

数字一侧的驱动电路是达林顿连接的发射极接地型开关。

段驱动电路采用NPN晶体管射极跟随器型开关。

这个电路与前面的图8.23比较,由于采用射极跟随器型开关,所以没有必要给基极插入限流电阻,从而减少了电路的元件数目。

流过段的电流也与图8.23的电路相同,设定为30mA。

由于射极跟随器型开关晶体管的CE是0.6V(图8.23的发射极接地型开关中VCE(sat)在0.1V以下,可以忽略),所以R1~ R7的值小了(R1~ R7=(5V-2V-0.6V-0.6V)/30mA≈62Ω)。

8.5.4光耦合器的传输电路

如图8.27所示,光耦合器是由LED(发光二极管)与光敏二极管(接收光并将光转换为电流的二极管)以及晶体管组合起来的放大/开关器件(也有用光敏晶体管(利用光进行接通/断开的晶体管)替代光敏二极管和晶体管的器件)。

光耦合器是通过电流流过LED