FM24C64.docx

《FM24C64.docx》由会员分享,可在线阅读,更多相关《FM24C64.docx(39页珍藏版)》请在冰豆网上搜索。

FM24C64

FM24C64

64KbFRAMSerialMemory

Features

64KbitFerroelectricNonvolatileRAM

∙Organizedas8,192x8bits

∙HighEndurance1Trillion(1012)Read/Writes

∙45YearDataRetention

∙NoDelay™Writes

∙AdvancedHigh-ReliabilityFerroelectricProcess

FastTwo-wireSerialInterface

∙Upto1MHzmaximumbusfrequency

∙DirecthardwarereplacementforEEPROM

∙Supportslegacytimingfor100kHz&400kHz

Description

TheFM24C64isa64-kilobitnonvolatilememory

LowPowerOperation

∙5Voperation

∙150∝AActiveCurrent(100kHz)

∙10∝AStandbyCurrent

IndustryStandardConfiguration

∙IndustrialTemperature-40︒Cto+85︒C

∙8-pin“Green”/RoHSSOIC(-G)

∙Grade3AEC-Q100Qualified(-G)

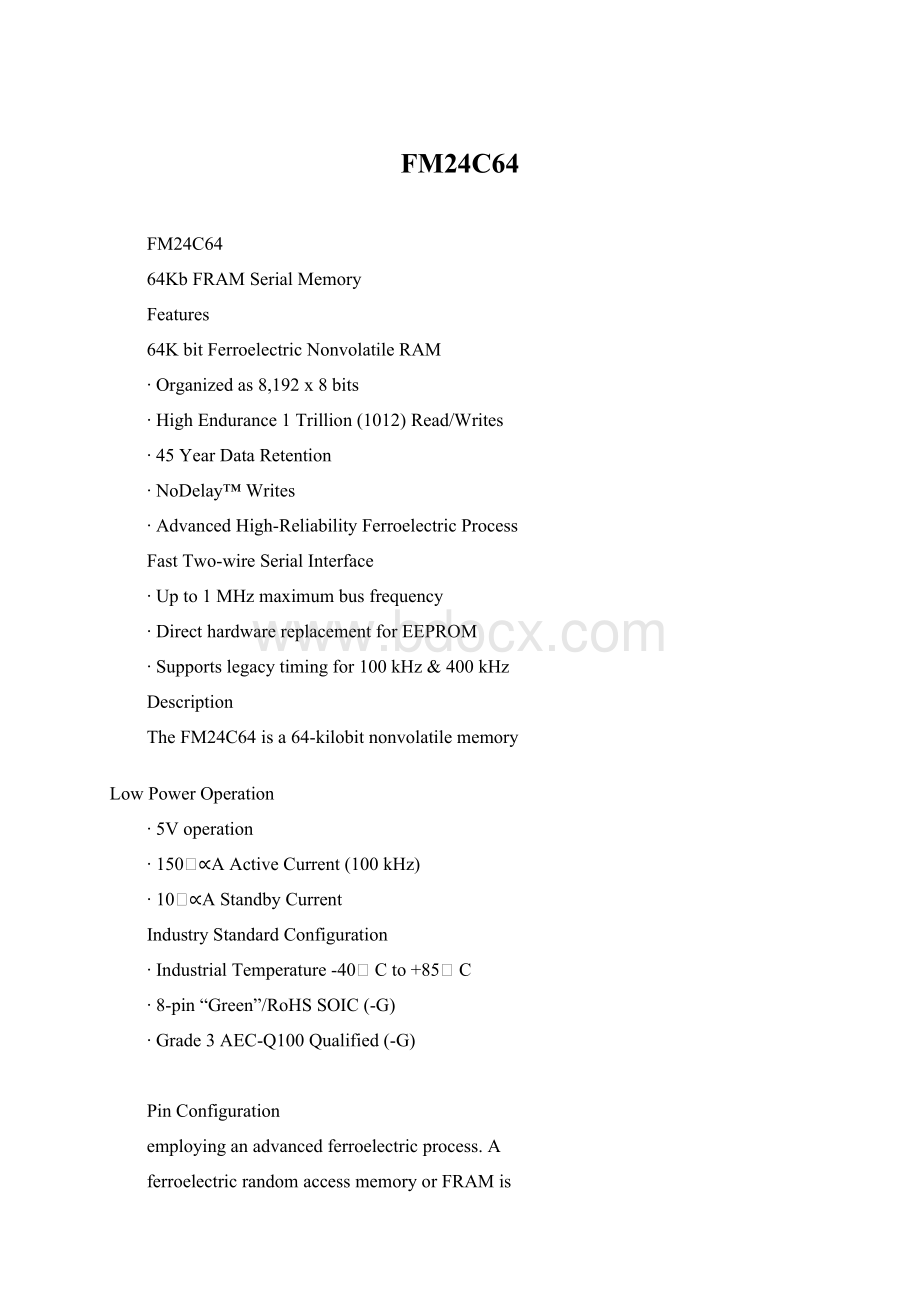

PinConfiguration

employinganadvancedferroelectricprocess.A

ferroelectricrandomaccessmemoryorFRAMis

nonvolatileandperformsreadsandwriteslikea

RAM.Itprovidesreliabledataretentionfor45years

whileeliminatingthecomplexities,overhead,and

systemlevelreliabilityproblemscausedby

EEPROMandothernonvolatilememories.

A0

A1

A2

VSS

1

2

3

4

8

7

6

5

VDD

WP

SCL

SDA

TheFM24C64performswriteoperationsatbus

speed.Nowritedelaysareincurred.Dataiswrittento

thememoryarrayinthecycleafterithasbeen

successfullytransferredtothedevice.Thenextbus

cyclemaycommenceimmediately.TheFM24C64is

capableofsupporting1012read/writecycles,ora

milliontimesmorewritecyclesthanEEPROM.

ThesecapabilitiesmaketheFM24C64idealfor

nonvolatilememoryapplicationsrequiringfrequent

orrapidwrites.Examplesrangefromdatacollection

wherethenumberofwritecyclesmaybecritical,to

demandingindustrialcontrolswherethelongwrite

timeofEEPROMcancausedataloss.The

combinationoffeaturesallowsmorefrequentdata

writeswithlessoverheadforthesystem.

TheFM24C64providessubstantialbenefitstousers

ofserialEEPROM,yetthesebenefitsareavailablein

ahardwaredrop-inreplacement.TheFM24C64is

availableinanindustrystandard8-pinSOICpackage

usingatwo-wireprotocol.Thespecificationsare

guaranteedoveranindustrialtemperaturerangeof

-40°Cto+85°C.

ThisproductconformstospecificationsperthetermsoftheRamtron

standardwarranty.TheproducthascompletedRamtron’sinternal

qualificationtestingandhasreachedproductionstatus.

*Endoflife.LasttimebuyJune2009.

RamtronInternationalCorporation

1850RamtronDrive,ColoradoSprings,CO80921

(800)545-FRAM,(719)481-7000

Rev.3.1

May2009

1of12

PinNames

Function

A0-A2

DeviceSelectAddress

SDA

SerialData/address

SCL

SerialClock

WP

WriteProtect

VSS

Ground

VDD

SupplyVoltage

OrderingInformation

FM24C64-G

“Green”/RoHS8-pinSOIC

FM24C64-GTR

“Green”/RoHS8-pinSOIC,

Tape&Reel

FM24C64-S*

8-pinSOIC

FM24C64-STR*

8-pinSOIC,Tape&Reel

FM24C64

Counter

Address

Latch

1,024x64

FRAMArray

8

SDA

SCL

WP

SerialtoParallel

Converter

ControlLogic

DataLatch

A0-A2

Figure1.FM24C64BlockDiagram

PinDescription

Rev.3.1

May2009

2of12

PinName

I/O

PinDescription

A0-A2

Input

Address2-0:

Thesepinsareusedtoselectoneofupto8devicesofthesametypeon

thesametwo-wirebus.Toselectthedevice,theaddressvalueonthethreepinsmust

matchthecorrespondingbitscontainedinthedeviceaddress.

SDA

I/O

SerialDataAddress:

Thisisabi-directionalpinusedtoshiftserialdataandaddresses

forthetwo-wireinterface.Itemploysanopen-drainoutputandisintendedtobewire-

OR’dwithotherdevicesonthetwo-wirebus.TheinputbufferincorporatesaSchmitt

triggerfornoiseimmunityandtheoutputdriverincludesslopecontrolforfalling

edges.Apull-upresistorisrequired.

SCL

Input

SerialClock:

Theserialclockinputforthetwo-wireinterface.Dataisclockedoutof

thedeviceontheSCLfallingedge,andclockedinontheSCLrisingedge.TheSCL

inputalsoincorporatesaSchmitttriggerinputforimprovednoiseimmunity.

WP

Input

WriteProtect:

WhenWPishigh,addressesintheupperquadrantofthelogical

memorymapwillbewrite-protected.Writeaccessispermittedtothelowerthree-

quartersoftheaddressspace.WhenWPislow,alladdressesmaybewritten.Thispin

mustnotbeleftfloating.

VDD

Supply

SupplyVoltage:

5V

VSS

Supply

Ground

FM24C64

Overview

TheFM24C64isaserialFRAMmemory.The

memoryarrayislogicallyorganizedasa8,192x8bit

memoryarrayandisaccessedusinganindustry

standardtwo-wireinterface.Functionaloperationof

theFRAMissimilartoserialEEPROMs.Themajor

differencebetweentheFM24C64andaserial

EEPROMwiththesamepinoutrelatestoitssuperior

writeperformance.

MemoryArchitecture

WhenaccessingtheFM24C64,theuseraddresses

8,192locationseachwith8databits.Thesedatabits

areshiftedserially.The8,192addressesareaccessed

usingthetwo-wireprotocol,whichincludesaslave

address(todistinguishfromothernon-memory

devices),andanextended16-bitaddress.Onlythe

lower13bitsareusedbythedecoderforaccessing

thememory.Theupperthreeaddressbitsshouldbe

setto0forcompatibilitywithlargerdevicesinthe

future.

Thememoryisreadorwrittenatthespeedofthe

two-wirebus.UnlikeanEEPROM,itisnot

necessarytopollthedeviceforareadycondition

sincewritesoccuratbusspeed.Thatis,bythetimea

newbustransactioncanbeshiftedintothepart,a

Two-wireInterface

TheFM24C64employsabi-directionaltwo-wirebus

protocolusingfewpinsandlittleboardspace.Figure

2illustratesatypicalsystemconfigurationusingthe

FM24C64inamicrocontroller-basedsystem.The

industrystandardtwo-wirebusisfamiliartomany

usersbutisdescribedinthissection.

Byconvention,anydevicethatissendingdataonto

thebusisthetransmitterwhilethetargetdevicefor

thisdataisthereceiver.Thedevicethatiscontrolling

thebusisthemaster.Themasterisresponsiblefor

generatingtheclocksignalforalloperations.Any

deviceonthebusthatisbeingcontrolledisaslave.

TheFM24C64alwaysisaslavedevice.

Thebusprotocoliscontrolledbytransitionstatesin

theSDAandSCLsignals.Therearefourconditions:

Start,Stop,Databit,andAcknowledge.Figure3

illustratesthesignalconditionsthatspecifythefour

states.Detailedtimingdiagramsareshowninthe

ElectricalSpecificationssection.

VDD

Rmin=1.8KΩ

writeoperationiscomplete.Thisisexplainedinmore

detailintheinterfacesectionbelow.

Userscanexpectseveralobvioussystembenefits

fromtheFM24C64duetoitsfastwritecycleand

Microcontroller

Rmax=tR/Cbus

highenduranceascomparedwithEEPROM.

SDA

SCL

SDA

SCL

Howevertherearelessobviousbenefitsaswell.For

exampleinahighnoiseenvironment,thefast-write

operationislesssusceptibletocorruptionthanan

EEPROMsinceitiscompletedquickly.Bycontrast,

FM24C64

A0A1A2

FM24C64

A0A1A2

anEEPROMrequiringmillisecondstowriteis

vulnerabletonoiseduringmuchofthecycle.

NotethattheFM24C64containsnopower

managementcircuitsotherthanasimpleinternal

power-onreset.Itistheuser’sresponsibilityto

ensurethatVDDiswithindatasheettolerancesto

preventincorrectoperation.

Rev.3.1

May2009

Figure2.TypicalSystemConfiguration

3of12

FM24C64

Figure3.DataTransferProtocol

StopCondition

AStopconditionisindicatedwhenthebusmaster

drivesSDAfromlowtohighwhiletheSCLsignalis

high.AlloperationsmustendwithaStopcondition.

Ifanoperationispendingwhenastopisasserted,the

operationwillbeaborted.Themastermusthave

controlofSDA(notamemoryread)inordertoassert

aStopcondition.

StartCondition

AStartconditionisindicatedwhenthebusmaster

drivesSDAfromhightolowwhiletheSCLsignalis

high.Allreadandwritetransactionsbeginwitha

Startcondition.Anoperationinprogresscanbe

abortedbyassertingaStartconditionatanytime.

AbortinganoperationusingtheStartconditionwill

readytheFM24C64foranewoperation.

Ifduringoperationthepowersupplydropsbelowthe

specifiedVDDminimum,thesystemshouldissuea

Startconditionpriortoperforminganotheroperation

Data/AddressTransfer

Alldatatransfers(includingaddresses)takeplace

whiletheSCLsignalishigh.Exceptunderthetwo

conditionsdescribedabove,theSDAsignalshould

notchangewhileSCLishigh.

Acknowledge

TheAcknowledgetakesplaceafterthe8thdatabit

hasbeentransferredinanytransaction.Duringthis

statethetransmittershouldreleasetheSDAbusto

allowthereceivertodriveit.Thereceiverdrivesthe

SDAsignallowtoacknowledgereceiptofthebyte.

IfthereceiverdoesnotdriveSDAlow,thecondition

isaNo-Acknowledgeandtheoperationisaborted.

Rev.3.1

May2009

Thereceivercouldfailtoack