武汉大学电气数电仿真实验.docx

《武汉大学电气数电仿真实验.docx》由会员分享,可在线阅读,更多相关《武汉大学电气数电仿真实验.docx(12页珍藏版)》请在冰豆网上搜索。

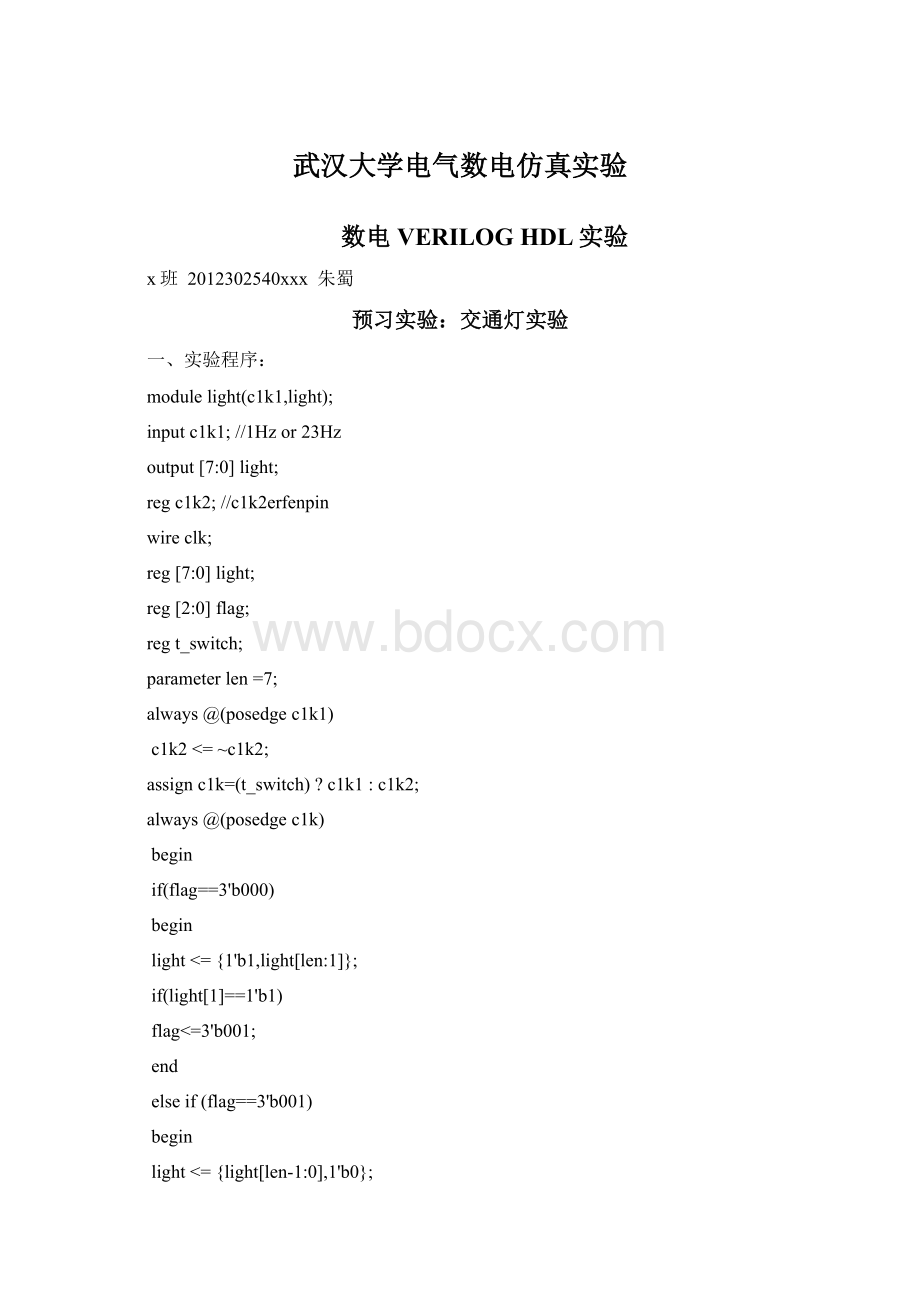

武汉大学电气数电仿真实验

数电VERILOGHDL实验

x班2012302540xxx朱蜀

预习实验:

交通灯实验

一、实验程序:

modulelight(c1k1,light);

inputc1k1;//1Hzor23Hz

output[7:

0]light;

regc1k2;//c1k2erfenpin

wireclk;

reg[7:

0]light;

reg[2:

0]flag;

regt_switch;

parameterlen=7;

always@(posedgec1k1)

c1k2<=~c1k2;

assignc1k=(t_switch)?

c1k1:

c1k2;

always@(posedgec1k)

begin

if(flag==3'b000)

begin

light<={1'b1,light[len:

1]};

if(light[1]==1'b1)

flag<=3'b001;

end

elseif(flag==3'b001)

begin

light<={light[len-1:

0],1'b0};

if(light[6]==1'b0)

flag<=3'b010;

end

elseif(flag==3'b010)

begin

light[len:

4]<={light[len-1:

4],1'b1};

light[len-4:

0]<={1'b1,light[len-4:

1]};

if(light[1]==1'b1)

flag<=3'b011;

end

elseif(flag==3'b011)

begin

light[len:

4]<={1'b0,light[len:

5]};

light[len-4:

0]<={light[len-5:

0],1'b0};

if(light[2]==1'b0)

flag<=3'b100;

end

elseif(flag==3'b100)

begin

light[len:

4]<={1'b1,light[len:

5]};

light[len-4:

0]<={1'b1,light[len-4:

1]};

if(light[1]==1'b1)

flag<=3'b101;

end

elseif(flag==3'b101)

begin

light<=8'h00;

flag<=3'b110;

end

elseif(flag==3'b110)

begin

t_switch<=~t_switch;

flag<=3'b000;

end

end

endmodule

二、实验波形:

三、实验电路:

实验一:

1位全加器的设计

一、实验目的:

1、掌握QuartusⅡ8.0软件使用流程。

2、初步掌握VERILOG的编程方法。

二、实验原理:

一位全加器的真值表如下:

A

B

Ci

S

Co

0

0

0

0

0

0

0

1

1

0

0

1

0

1

0

0

1

1

0

1

1

0

0

1

0

1

0

1

0

1

1

1

0

0

1

1

1

1

1

1

一位全加器的逻辑表达式为:

Sum=a^b^ci;

Co=a&b|(a^b)&Ci.

三、实验程序:

modulefulladder(a,b,c1,ch,sum);

inputa,b,c1;

outputch,sum;

regch,sum;

always@(aorborc1)

begin

sum=a^b^c1;

ch=a&b|(a^b)&c1;

end

endmodule

四、实验波形:

五、实验电路:

六、将实验电路保存为元件符号,供实验二使用。

保存方法如下:

file菜单下的creatsymbolsfiles。

实验二:

四位全加器的设计

一、实验目的:

1、掌握图形层次设计方法;

2、熟悉QUARTUSⅡ8.0软件的使用及设计流程;

3、掌握全加器原理,能进行多位全加器的设计。

二、实验原理图:

调用实验一所完成的一位全加器。

实验三:

三输入与门、三输入或门

一、实验目的:

1、理解简单组合电路设计方法。

2、掌握基本门电路的应用。

二、实验原理:

三输入与门、三输入或门的输出分别为:

Out=a&b&c;out=a^b^c;

三、实验程序:

moduleinput3_AND(A,B,C,L);//and

inputA,B,C;

outputL;

assignL=A&B&C;

endmodule

moduleinput3_OR(A,B,C,L);//or

inputA,B,C;

outputL;

assignL=A^B^C;

endmodule

四、实验波形:

实验四:

8-3优先编码器

一、实验目的:

1、熟悉常用编码器的功能逻辑。

2、熟悉VERILOG的代码编写方法。

二、实验代码:

(采用两种编码方式)

1、

moduleyouxian8_3bianmaqi(X,Y);

input[7:

0]X;

output[2:

0]Y;

assignY[0]=~(~(X[1])&X[2]&X[4]&X[6]|~(X[3])&X[4]&X[6]|~(X[5])&X[6]|~(X[7]));

assignY[1]=~(~(X[2])&X[4]&X[5]|~(X[3])&X[4]&X[5]|~(X[6])|~(X[7]));

assignY[2]=X[4]&X[5]&X[6]&X[7];

endmodule

2、

moduleyouxian8_3bianmaqi(X,Y);

input[7:

0]X;

output[2:

0]Y;

reg[2:

0]Y;

always@(X)

if(~X[7])Y=3'b000;else

if(~X[6])Y=3'b001;else

if(~X[5])Y=3'b010;else

if(~X[4])Y=3'b011;else

if(~X[3])Y=3'b100;else

if(~X[2])Y=3'b101;else

if(~X[1])Y=3'b110;elseY=3'b111;

endmodule

三、程序波形:

实验五:

3-8线译码器

一、实验目的:

1、熟悉常用译码器的逻辑功能。

2、掌握复杂译码器的设计方法。

二、实验代码:

moduleswitch3_8(EN,X,Y);

input[0:

2]X;

inputEN;//ENweishinengxinghao

output[0:

7]Y;

reg[0:

7]Y;

always@(X)

if(EN)Y=8'b11111111;

else

begin

if(X==3'b000)Y=8'b01111111;

if(X==3'b001)Y=8'b10111111;

if(X==3'b010)Y=8'b11011111;

if(X==3'b011)Y=8'b11101111;

if(X==3'b100)Y=8'b11110111;

if(X==3'b101)Y=8'b11111011;

if(X==3'b110)Y=8'b11111101;

if(X==3'b111)Y=8'b11111110;

end

endmodule

三、实验电路:

实验六:

八位十进制频率计实验

一、实验目的:

1、进一步了解VERILOG语言功能

2、了解EDA在高频工作下的优势,这是单片机无法比拟的

二、实验代码:

(包括一个十进制计数器、一个四位锁存器)

1、以下是四位锁存器

moduleoctal(clk,en,d_in,q_in);

inputclk,en;

input[3:

0]d_in;

output[3:

0]q_in;

reg[3:

0]Q;

assignq_in=Q;

always@(posedgeclk)

if(!

en)

beginQ<=d_in;end

endmodule

2、以下是十进制计数器

modulepinlvji8_10(clr,CP,EN,load,D,Q,TC);

input[0:

3]D;

output[0:

3]Q;

inputclr,CP,EN,load;

outputTC;

regTC;

reg[0:

3]Q;

always@(posedgeCP)

if(EN)

begin

if(~clr)beginQ<=4'b0000;TC<=1'b0;end

else

if(~load)Q<=D;

else

if(CP)

begin

Q<=Q+1'b1;if(Q==4'b1111)TC<=1'b1;elseTC<=1'b0;

end

end

endmodule

三、实验波形:

图6.1四位锁存器波形

图6.2(a)十进制计数器clr控制波形

图6.2(b)十进制计数器load控制波形

图6.2(c)十进制计数器TC进位信号波形

实验心得与体会:

通过本次QUARTUS软件的学习,初步掌握了两种编辑方法。

一种是用VERILOG语言编写,一种是图形编辑,两种方法都方便快捷,具有其他硬件无可比拟的优势。

对于我们所在专业,数字电路是必不可少的一门专业知识,有了这个软件无疑给我们提供了很大方便,在以后的日子里,一定要加强这方面知识的学习。